Professional Documents

Culture Documents

VHDL Program

Uploaded by

Jaswanth TejaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VHDL Program

Uploaded by

Jaswanth TejaCopyright:

Available Formats

the VHDL code for 2-4 decoder. ibrary ieee; use ieee.std_logic_1164.

all; entity decoder_2_4 is port( a: in std_logic_vector(1 downto 0); en: in std_logic; y: out std_logic_vector(3 downto 0) ); end decoder_2_4; architecture arch of decoder_2_4 is begin y <= "0000" when (en='0') else "0001" when (a="00") else "0010" when (a="01") else "0100" when (a="10") else "1000"; -- a="11" end arch; VHDL Code for 4 Bit Comparator LIBRARY ieee ; USE ieee.std_logic_1164.all ; USE ieee.std_logic_arith.all ; ENTITY compare IS PORT ( A, B : IN SIGNED(3 DOWNTO 0) ; AeqB, AgtB, AltB : OUT STD_LOGIC ) ; END compare ; ARCHITECTURE Behavior OF compare IS BEGIN AeqB <= 1 WHEN A = B ELSE 0 ; AgtB <= 1 WHEN A > B ELSE 0 ; AltB <= 1 WHEN A < B ELSE 0 ; END Behavior ; VHDL Code for JK flip flop --libraries to be used are specified here library IEEE; use IEEE.STD_LOGIC_1164.ALL; --entity declaration with port definitions entity JK_Flipflop is port ( clk: in std_logic; J, K: in std_logic; Q, Qbar: out std_logic; reset: in std_logic );

end JK_Flipflop; --architecture of entity architecture Behavioral of JK_Flipflop is --signal declaration. signal qtemp,qbartemp : std_logic :='0'; begin Q <= qtemp; Qbar <= qbartemp; process(clk,reset) begin if(reset = '1') then --Reset the output. qtemp <= '0'; qbartemp <= '1'; elsif( rising_edge(clk) ) then if(J='0' and K='0') then --No change in the output NULL; elsif(J='0' and K='1') then --Set the output. qtemp <= '0'; qbartemp <= '1'; elsif(J='1' and K='0') then --Reset the output. qtemp <= '1'; qbartemp <= '0'; else --Toggle the output. qtemp <= not qtemp; qbartemp <= not qbartemp; end if; end if; end process; end Behavioral; VHDL Code for T flip flop library ieee; use ieee.std_logic_1164.all entity tff is port( clk: in std_logic; reset: in std_logic; t: in std_logic; q: out std_logic ); enf tff; architecture behave of tff is signal q_reg: std_logic; signal q_next: std_logic; begin

process begin if (reset = '1') then q_reg <= '0'; elsif (clk'event and clk = '1') then q_reg <= q_next; end if; end process; q_next <= q_reg when t = '0' else not(q_reg); q <= q_reg; end behave; 4-Bit BCD Up Counter with Clock Enable library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Counter2_VHDL is port( Clock_enable: in std_logic; Clock: in std_logic; Reset: in std_logic; Output: out std_logic_vector(0 to 3)); end Counter2_VHDL; architecture Behavioral of Counter2_VHDL is signal temp: std_logic_vector(0 to 3); begin process(Clock,Reset) begin if Reset='1' then temp <= "0000"; elsif(Clock'event and Clock='1') then if Clock_enable='0' then if temp="1001" then temp<="0000"; else temp <= temp + 1; end if; else temp <= temp; end if; end if; end process; Output <= temp; end Behavioral;

VHDL code for Full Adder using dataflow style LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY fulladd IS PORT ( Cin, x, y s, Cout : OUT END fulladd ; : IN STD_LOGIC ; STD_LOGIC ) ;

ARCHITECTURE beh OF fulladd IS BEGIN s <= x XOR y XOR Cin ; Cout <= (x AND y) OR (Cin AND x) OR (Cin AND y) ; END beh ;

VHDL code for Full Adder using structural style

library IEEE; use IEEE.std_logic_1164.all; entity bejoy_fa is port(In1,In2,c_in : in std_logic; sum, c_out : out std_logic); end bejoy_fa; architecture arc of bejoy_fa is component half_adder port(a,b : in std_logic; sum, carry : out std_logic); end component; component or_2 port(a,b : in std_logic; c : out std_logic); end component; signal s1, s2, s3 : std_logic; begin H1: half_adder port map(a=>In1, b=>In2, sum=>s1, carry=>s3); H2: half_adder port map(a=>s1, b=>c_in, sum=>sum, carry=>s2); O1: or_2 port map(a=> s2, b=>s3, c=>c_out); end arc; entity half_adder is port (a,b : in bit ; sum,carry : out bit);

end half_adder; architecture arc of half_adder is begin sum<= a xor b; carry <= a and b; end arc; entity or_2 is port (a,b : in bit ; c : out bit); end or_2; architecture arc of or_2 is begin c<= a or b; end arc;

--VHDL code for BEHAVIORAL model of Full Adder library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity FA_Bhr is port(Fx, Fy, Fcin : in BIT; Fs, Fcout : out BIT); end FA_Bhr; architecture FA_struct of FA_Bhr is component HAport (hx, hy :in BIT; hs, hcout: out BIT); end component; signal s1, c1, c2 : BIT; begin HA1: HA port map (Fx, Fy, s1, c1); HA2: HA port map (s1, Fcin, Fs, c2); Fcout <= c1 OR c2; end FA_struct;

You might also like

- Standard VHDL ExamplesDocument56 pagesStandard VHDL Examplesshilpi lavaniaNo ratings yet

- VHDL Programs LabDocument20 pagesVHDL Programs LabVasu SiriNo ratings yet

- VHDL CodeDocument34 pagesVHDL CodeHimanshu Thakur100% (1)

- VHDL Lab FileDocument48 pagesVHDL Lab FileAnkit Gupta100% (1)

- VHDL FileDocument25 pagesVHDL Filenitin_280890No ratings yet

- Programming FPGAsDocument38 pagesProgramming FPGAssayuri8910No ratings yet

- Demux VHDL Code Using Behavioural ModelingDocument1 pageDemux VHDL Code Using Behavioural ModelingOP2RNo ratings yet

- VHDL Digital NAND Gate Program.Document14 pagesVHDL Digital NAND Gate Program.Muchamad Aldi AnantaNo ratings yet

- VHDL TD - CorrigéDocument6 pagesVHDL TD - CorrigéSahsah AbdeslamNo ratings yet

- The VHDL Hardware Description Language: CSEE W4840Document31 pagesThe VHDL Hardware Description Language: CSEE W4840ankit bansalNo ratings yet

- Following Is The Verilog Code For FlipDocument26 pagesFollowing Is The Verilog Code For FlipDivya MuraliNo ratings yet

- Xlinx - VLSI Practical Lab ManualDocument31 pagesXlinx - VLSI Practical Lab ManualSamarth J Parikh0% (1)

- Decade CounterDocument3 pagesDecade CounterManohar thota100% (1)

- VHDL Code For 4-Bit Shift RegisterDocument17 pagesVHDL Code For 4-Bit Shift RegisterAnónimo AnónimoNo ratings yet

- Exercices VHDLDocument83 pagesExercices VHDLFadi Akoury50% (2)

- VHDL LabDocument18 pagesVHDL Labapi-370179750% (2)

- VHDL Code For Digital Clock On FPGADocument6 pagesVHDL Code For Digital Clock On FPGASidney O. EbotNo ratings yet

- Digital Clock in VHDLDocument2 pagesDigital Clock in VHDLTapas KolteNo ratings yet

- VHDLDocument11 pagesVHDLlizhi0007No ratings yet

- VHDL Practical Exam GuideDocument95 pagesVHDL Practical Exam GuideIslam SehsahNo ratings yet

- Design of Binary Multiplier Using Adders-3017 PDFDocument5 pagesDesign of Binary Multiplier Using Adders-3017 PDFAdrian Walter JavierNo ratings yet

- VerilogDocument34 pagesVerilogromeoalvzNo ratings yet

- VHDL BasicDocument242 pagesVHDL BasicKiran GunasegaranNo ratings yet

- Binary To Excess 3 VHDL Code Using Structural ModelingDocument1 pageBinary To Excess 3 VHDL Code Using Structural ModelingOP2RNo ratings yet

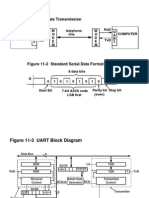

- UARTDocument26 pagesUARTShantanu Tripathi100% (2)

- VHDL PresentationDocument76 pagesVHDL PresentationChutiyaNo ratings yet

- Verilog BasicsDocument42 pagesVerilog BasicsKarthik SharmaNo ratings yet

- AssignmentDocument58 pagesAssignmentTờ ÙngNo ratings yet

- 4bit Array MultiplierDocument4 pages4bit Array MultiplierRahul TiwariNo ratings yet

- 4-Bit ALUDocument3 pages4-Bit ALUdipendughoshNo ratings yet

- Verilog HDL Lectuer 5Document36 pagesVerilog HDL Lectuer 5Nilesh GulveNo ratings yet

- Verilog Modules For Common Digital FunctionsDocument30 pagesVerilog Modules For Common Digital Functionselle868No ratings yet

- VHDL UartDocument53 pagesVHDL UartEhsan Mahdavi100% (1)

- VHDL Samples1Document55 pagesVHDL Samples1ramu143416305No ratings yet

- VHDL ProgramsDocument30 pagesVHDL ProgramsVijay Singh100% (1)

- VHDL For A Code LockDocument7 pagesVHDL For A Code LockRidaAbdeLkrimiNo ratings yet

- VHDL Code For 4 Bit ComparatorDocument2 pagesVHDL Code For 4 Bit Comparatornady220944% (9)

- HDL Manual 2020 5th Sem E&CE 18ECL58Document74 pagesHDL Manual 2020 5th Sem E&CE 18ECL58vishvakiranaNo ratings yet

- J-K - To - D Flip-Flop Conversion VHDL CodeDocument2 pagesJ-K - To - D Flip-Flop Conversion VHDL CodeOP2RNo ratings yet

- Xilinx ISE VHDL and Simulator Tutorial V 14.7Document38 pagesXilinx ISE VHDL and Simulator Tutorial V 14.7ReeseNo ratings yet

- HDL Manual 2019 5th Sem E&CE 17ECL58Document77 pagesHDL Manual 2019 5th Sem E&CE 17ECL58vishvakirana100% (1)

- FPGA Temp SensorDocument8 pagesFPGA Temp SensorNam NguyenNo ratings yet

- VHDL ExamplesDocument28 pagesVHDL Examplesapi-3731978No ratings yet

- VerilogDocument61 pagesVerilogSathish Kumar100% (1)

- FPGA Temp SensorDocument8 pagesFPGA Temp SensorRajan BhartiNo ratings yet

- Verilog Code For Fir FilterDocument58 pagesVerilog Code For Fir FilterKishore KumarNo ratings yet

- 8 Bit ALU by XilinxDocument16 pages8 Bit ALU by XilinxDIPTANU MAJUMDERNo ratings yet

- Ver I Log ExamplesDocument22 pagesVer I Log ExamplesDayanand Gowda KrNo ratings yet

- Half and Full Adder Using VHDLDocument16 pagesHalf and Full Adder Using VHDLnady2209100% (3)

- Digital Lab Cs 6211 VHDL ProgramsDocument13 pagesDigital Lab Cs 6211 VHDL ProgramsMurugan GNo ratings yet

- VHDLDocument13 pagesVHDLSrijeeta SenNo ratings yet

- Experiment No.1: A Binary To Gray ConverterDocument26 pagesExperiment No.1: A Binary To Gray ConverterVarun SharmaNo ratings yet

- Micro TPDocument7 pagesMicro TPsebastienNo ratings yet

- Unit 3: Combinational Circuit DesignDocument30 pagesUnit 3: Combinational Circuit DesignKarn AroraNo ratings yet

- VHDL From BotrosDocument17 pagesVHDL From BotrossanjanaNo ratings yet

- Date: 28 September, 2015: VHDL Assighment 2Document15 pagesDate: 28 September, 2015: VHDL Assighment 2Ishan DarwhekarNo ratings yet

- Design and Simulation of Logic Gates Using VHDLDocument26 pagesDesign and Simulation of Logic Gates Using VHDLSushanth BabuNo ratings yet

- Asynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterDocument20 pagesAsynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterKalagadda BikshaluNo ratings yet

- V HDL SampleDocument5 pagesV HDL Sampleppat2006No ratings yet

- DSD Lab ManualDocument16 pagesDSD Lab ManualPreeti SinghNo ratings yet

- Programming 8051 MicrocontrollerDocument121 pagesProgramming 8051 MicrocontrollertakenoveraccountNo ratings yet

- 100G Transport SystemsDocument12 pages100G Transport Systemsaltamirandodapaz@msn.comNo ratings yet

- UntitledDocument258 pagesUntitledSaanounNo ratings yet

- vr7000 Brochure PDFDocument4 pagesvr7000 Brochure PDFvangNo ratings yet

- B.E. ECE FinalDocument126 pagesB.E. ECE FinalGanapathi SubramanianNo ratings yet

- 350W Single Output DC-DC Converter: SeriesDocument3 pages350W Single Output DC-DC Converter: Seriesninjai_thelittleninjaNo ratings yet

- Fulltext MosfetDocument192 pagesFulltext MosfetMuhammad Khosyi'inNo ratings yet

- B2.D.3.02 Dual Band 900+2100MHz (Rosenberger)Document2 pagesB2.D.3.02 Dual Band 900+2100MHz (Rosenberger)Bui Trung Hieu0% (1)

- Sytem BusDocument24 pagesSytem BusRam RamNo ratings yet

- 07 B OdaiE ActiveOpticalComp SlidesDocument23 pages07 B OdaiE ActiveOpticalComp SlidesDeepansh AgrawalNo ratings yet

- L2-ELN-SPE-012.pdf SCADA CablingDocument7 pagesL2-ELN-SPE-012.pdf SCADA CablinghardikNo ratings yet

- DS-K1T804AMF Fingerprint Access Control TerminalDocument3 pagesDS-K1T804AMF Fingerprint Access Control TerminalLuis RomeroNo ratings yet

- Ctia Ota Test Plan 3 8 2Document628 pagesCtia Ota Test Plan 3 8 2Sub FireNo ratings yet

- First-Class in Every Sense.: Sound & Vision 2011 - 2012Document27 pagesFirst-Class in Every Sense.: Sound & Vision 2011 - 2012Razvan BaraganNo ratings yet

- Port City International University: Mid-Term Lab ReportDocument5 pagesPort City International University: Mid-Term Lab ReportMohammad Azimul HoqueNo ratings yet

- CB FailDocument6 pagesCB FailAhmed Said GhonimyNo ratings yet

- SM-J120H.HZ Galaxy J1 2016Document8 pagesSM-J120H.HZ Galaxy J1 2016New LeoNo ratings yet

- HP 1 Foxconn PM-AMD (PM A HPC S PROTO A X1 090826D2)Document68 pagesHP 1 Foxconn PM-AMD (PM A HPC S PROTO A X1 090826D2)Cedomir GajicNo ratings yet

- Ebook - Guitar Rig - Tutorials by Jerry McphersonDocument11 pagesEbook - Guitar Rig - Tutorials by Jerry McphersonJoe MassoNo ratings yet

- Itu-T: Ethernet Service Activation Test MethodologyDocument38 pagesItu-T: Ethernet Service Activation Test MethodologyJamez STNo ratings yet

- Thesis NewDocument55 pagesThesis NewHasan juwelNo ratings yet

- Answer Final BEKC2433 - 1819 - Sem01Document26 pagesAnswer Final BEKC2433 - 1819 - Sem01Hui ShanNo ratings yet

- 12V Light Dimmer CircuitDocument6 pages12V Light Dimmer CircuitJuan CarNo ratings yet

- Channel Allocation in Cellular SystemDocument40 pagesChannel Allocation in Cellular SystemNishant MittalNo ratings yet

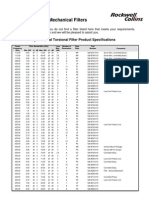

- Collins Torsional Mechanical Filters: Symmetrical Torsional Filter Product SpecificationsDocument2 pagesCollins Torsional Mechanical Filters: Symmetrical Torsional Filter Product SpecificationsGdfsndh GfdvhjzdNo ratings yet

- Ac Network AnalysisDocument28 pagesAc Network AnalysistrizzmercadoNo ratings yet

- Max Value Shove and CallDocument613 pagesMax Value Shove and CallDragoș DragomirNo ratings yet

- Tarea Unidad IV AEF 1052 Unidad IvaDocument1 pageTarea Unidad IV AEF 1052 Unidad IvaMaelenBecsaNo ratings yet

- 3G PSR CheckpointsDocument13 pages3G PSR CheckpointsKulbeerSinghNo ratings yet

- PLC Presentation NewDocument27 pagesPLC Presentation Newgautamjoshi83% (6)

- Hacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxFrom EverandHacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxRating: 4.5 out of 5 stars4.5/5 (67)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsFrom EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsRating: 5 out of 5 stars5/5 (4)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyFrom EverandChip War: The Quest to Dominate the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (229)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)From EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Rating: 5 out of 5 stars5/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102From EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Rating: 5 out of 5 stars5/5 (2)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsFrom EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongNo ratings yet

- Chip War: The Fight for the World's Most Critical TechnologyFrom EverandChip War: The Fight for the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (82)

- Microsoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsFrom EverandMicrosoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsNo ratings yet

- ITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationFrom EverandITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationRating: 5 out of 5 stars5/5 (2)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]From EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Rating: 5 out of 5 stars5/5 (4)

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsFrom EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsRating: 5 out of 5 stars5/5 (1)

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionFrom EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionRating: 5 out of 5 stars5/5 (4)

- Hacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.From EverandHacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.Rating: 5 out of 5 stars5/5 (2)

- Palo Alto Networks: The Ultimate Guide To Quickly Pass All The Exams And Getting Certified. Real Practice Test With Detailed Screenshots, Answers And ExplanationsFrom EverandPalo Alto Networks: The Ultimate Guide To Quickly Pass All The Exams And Getting Certified. Real Practice Test With Detailed Screenshots, Answers And ExplanationsNo ratings yet

- Computer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)From EverandComputer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)Rating: 4 out of 5 stars4/5 (4)

- Set Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNFrom EverandSet Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNRating: 5 out of 5 stars5/5 (1)

- Cybersecurity: The Beginner's Guide: A comprehensive guide to getting started in cybersecurityFrom EverandCybersecurity: The Beginner's Guide: A comprehensive guide to getting started in cybersecurityRating: 5 out of 5 stars5/5 (2)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715431191?v=1)