Professional Documents

Culture Documents

Lab 1

Uploaded by

Fawad KhanOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab 1

Uploaded by

Fawad KhanCopyright:

Available Formats

Lab 01 Lab Title: Introduction to Microwind and Analysis of CMOS 0.25micron Technology MOSFETs.

Lab Objective: In this lab students will be introduced to a Layout based EDA tool Microwind and the introduction will be accompanied with analysis of MOS transistors. The tool used in this lab is Microwind. The tasks given in the lab include, Familiarity and Hands on Example using the tool. Layout Design using the tool. Study of MOSFET Characteristics. Analog Simulation of MOSFETs. Tool used: Microwind Lab Description: MOSFET The Metal Oxide Semiconductor Field Effect Transistor is very important part of Digital Integrated Circuits. It is mostly used as switch in digital design. MOSFET is a four terminal device. The voltage applied to the gate terminal determine the current flow between drain and source terminals. The body/substrate of the transistor is the fourth terminal. Mostly the fourth terminal (body/substrate) of the device is connected to dc supply that is identical for all devices of the same type (GND for nMOS and Vdd for pMOS). Usually this terminal is not shown on the schematics. nMOS The nMOS transistor consists of n+ drain and source diffusion regions, which are embedded in a p-type substrate. The electrons in the channel beneath the gate between source and drain terminal are responsible for the current flow. pMOS The pMOS transistor consists of p+ drain and source diffusion regions, which are embedded in an n-type substrate. The holes in the channel beneath the gate between source and drain terminal are responsible for the current flow. CMOS The CMOS (Complementary MOS) consist of both p-type and n-type MOS. The advantage of CMOS is its low power design due its Static behavior. Design/ Diagram/Circuit

Lab Instructions a) Open the Microwind3-1 by double clicking it located in the installed directory of microwind 3-1

The following screen will be appeared

b) Select the foundry using the command File > Select Foundry c) Select 0.25-micron process by selecting cmos025.tec file. Click Open tab to continue.

d) Save the design as Lab01using the command File > Save as. e) Create an nMOS by using the nMOS generator button in the Palette

You can set the width and length of MOS by typing in the fields Width MOS and Length MOS either in micron or in lambda units as indicated in the above figure. Click on Generate Device Tab to generate the device.

f) Apply the voltages and output node using the symbol buttons Vdd, Gnd, Add a Pulse, and Visible node in the Palette menu, as indicated in the following figure. You can use the Stretch/Move command button for these actions.

g) Click on the Run Tab on the Tool bar menu to start the simulation or using the command Simulate > Run Simulation.

h) Now apply the Vdd to the n+ diffusion or drain terminal instead of Vss, run the simulation again.

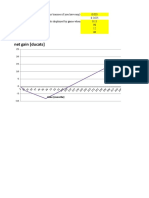

Analyze the simulation waveform, use different values of voltages for Vdd by double clicking on it and set the voltage level. Now we will make the above schematics.

Similarly the nMOS can be analyzed using different widths and different input voltages. i) Save the design.

Lab Tasks: Task#1: Task#2: Task#3: Task#4: Layout design analysis of nMOS using MOS generator. Layout design analysis of pMOS using MOS generator. Manually design the layout of nMOS. Manually design the layout of pMOS.

You might also like

- Securityinmobileadhocnetworks 130201071944 Phpapp02Document44 pagesSecurityinmobileadhocnetworks 130201071944 Phpapp02Fawad KhanNo ratings yet

- MicroWind Tutorial MineDocument12 pagesMicroWind Tutorial MineFawad Khan100% (1)

- MicroWind Tutorial MineDocument12 pagesMicroWind Tutorial MineFawad Khan100% (1)

- Lab 1Document6 pagesLab 1Fawad KhanNo ratings yet

- ADocument98 pagesAFawad KhanNo ratings yet

- Class & Programming Time TablesDocument1 pageClass & Programming Time TablesFawad KhanNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Tanner 02Document30 pagesTanner 02Saloni JainNo ratings yet

- Theoretical Framework on Cash Management and Business ValueDocument2 pagesTheoretical Framework on Cash Management and Business ValuePaula ReyesNo ratings yet

- Delta AirlinesDocument14 pagesDelta AirlinesAssignmentLab.com100% (2)

- Swot Analysis of Indian Road NetworkDocument2 pagesSwot Analysis of Indian Road NetworkArpit Vaidya100% (1)

- Industrialattachmentoffakirknitwearsltd 140511095156 Phpapp02Document140 pagesIndustrialattachmentoffakirknitwearsltd 140511095156 Phpapp02Anonymous etwfe5No ratings yet

- Market StructureDocument42 pagesMarket StructureSurya PanwarNo ratings yet

- Karachi Head Office Membership ListDocument10 pagesKarachi Head Office Membership ListUsama KHan100% (1)

- Tortillas From The Homesick TexanDocument6 pagesTortillas From The Homesick TexannezbeNo ratings yet

- Eu4 Loan-To-Build Profits CalculatorDocument8 pagesEu4 Loan-To-Build Profits CalculatorAnonymous pw0ajGNo ratings yet

- 10713-10611 NumbersDocument63 pages10713-10611 NumbersAbhishek PatelNo ratings yet

- Pollard's -Method ExplainedDocument4 pagesPollard's -Method ExplainedRanjith M KumarNo ratings yet

- Ultimate Financial ModelDocument33 pagesUltimate Financial ModelTulay Farra100% (1)

- Capital Budgeting Study at Panasonic CarbonDocument8 pagesCapital Budgeting Study at Panasonic Carbone WAYNo ratings yet

- Budgeting and Cost ControlDocument7 pagesBudgeting and Cost Controlnags18888No ratings yet

- PRC Room Assignment For December 2013 Nursing Board Exam (Cebu)Document150 pagesPRC Room Assignment For December 2013 Nursing Board Exam (Cebu)PhilippineNursingDirectory.comNo ratings yet

- Solutions For Economics Review QuestionsDocument28 pagesSolutions For Economics Review QuestionsDoris Acheng67% (3)

- OPOSing Telugu Curries PDFDocument2 pagesOPOSing Telugu Curries PDFpaadam68100% (2)

- Sweat GaloreDocument17 pagesSweat GaloreMuhdAfiq50% (2)

- Case Questions Spring 2012Document2 pagesCase Questions Spring 2012Refika TetikNo ratings yet

- Bhutans Gross National HappinessDocument4 pagesBhutans Gross National HappinessscrNo ratings yet

- Econ Reflective EssayDocument4 pagesEcon Reflective Essayapi-402338485No ratings yet

- Hotel ReportDocument6 pagesHotel ReportRamji SimhadriNo ratings yet

- Irf4104Gpbf: FeaturesDocument9 pagesIrf4104Gpbf: FeaturesAdam StevensonNo ratings yet

- Indian All Colleges Cources List For BcomDocument56 pagesIndian All Colleges Cources List For BcomAkshayKawaleNo ratings yet

- Shampoo Project Implications Dec Can IntellectsDocument13 pagesShampoo Project Implications Dec Can IntellectsRakesh SainikNo ratings yet

- CH 01Document28 pagesCH 01aliNo ratings yet

- I Foresaw ItDocument3 pagesI Foresaw ItGrace AvellanoNo ratings yet

- PC3200 DDR II RAM (DDR-400) model size compatibility guideDocument7 pagesPC3200 DDR II RAM (DDR-400) model size compatibility guideEduard RubiaNo ratings yet

- Multiple Choice: Performance Measurement, Compensation, and Multinational ConsiderationsDocument13 pagesMultiple Choice: Performance Measurement, Compensation, and Multinational ConsiderationsJEP WalwalNo ratings yet

- Association of Senior Citizens Hyderabad Newsletter May 2012Document4 pagesAssociation of Senior Citizens Hyderabad Newsletter May 2012rnctechNo ratings yet