Professional Documents

Culture Documents

Design Calculations For Robust I2C Communications - EDNDesign Calculations For Robust I2C Communications - EDN

Uploaded by

Anonymous DGq0O15nNzOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design Calculations For Robust I2C Communications - EDNDesign Calculations For Robust I2C Communications - EDN

Uploaded by

Anonymous DGq0O15nNzCopyright:

Available Formats

Design calculations for robust I2C communications | EDN

http://www.edn.com/design/analog/4371297/Design-calculations-for-rob...

EE Times

EDN

DataSheets.com

Design News

EBN

Test & Measurement World

Embedded.com

TechOnline

Events

UBM Electronics

Home > Analog Design Center > How To Article

Design calculations for robust I2C communications

Chris Parris, Senior Applications Engineer and Jonathan Dillon, Senior Applications Engineer, Memory Products Division, Microchip Technology Inc. - April 18, 2012 Many systems use an I2C bus for internal communications between devices, such as microprocessors, microcontrollers, memories, and other digitally-controlled devices. This bus topology relies on correctly sized resistance pull-ups for reliable, robust communications. Incorrectly sizing these resistors can lead to erroneous bus conditions and transmission errors caused by noise or changes in temperature and operating voltages, and by variations between devices. I2C is a two-wire synchronous bus with the SCL line used as a clock, produced by the bus master. The SDA line is used for bi-directional data transfer. The data line is modified while the clock is in specific states, to indicate the start and stop of transmissions, and avoid additional lines. The I2C bus is built around open-collector outputs, where a device can pull a line low through a transistor to ground, as shown in Figure 1. This allows easy arbitration over control of the bus, enabling the implementation of bi-directional communications on a single data line and multi-master support. As shown in Figure 1, each line has an external resistor to Vdd, which pulls the line high when released or idle.

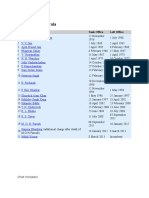

Figure 1: I2C Bus topology. The three considerations when determining the pull-up resistor values (Rp) are: Supply voltage (Vdd) Total bus capacitance (CBUS) Total high-level input current (IIH) Calculating the ideal pull-up resistor values for the following example conditions: Supply voltage (Vdd) of 5V Clock frequency of 400 KHz Bus capacitance of 100 pF Supply Voltage (Vdd) The I2C specification defines a voltage below VIL, or 30% of the supply voltage, as a logical low and, likewise, above VIH, or 70% of the supply voltage, as a logical high, as shown in Figure 2. A voltage between these two levels leads to an undefined logic level. In reality, the pin will read either logical high or low in this range, but it may vary between devices, with temperatures, voltages, noise sources and other environmental factors influencing the logic levels.

1 of 4

1/12/2013 11:47 PM

Design calculations for robust I2C communications | EDN

http://www.edn.com/design/analog/4371297/Design-calculations-for-rob...

Figure 2: Specified voltage levels for logical High and Low. The supply voltage limits the minimum Rp value for which the bus can be pulled low. A strong pull-up will prevent a device from being able to bring the line sufficiently low, to ensure a logical low is detected. This is caused by the potential divider formed between the pull-up resistor and the on-resistance of the transistor to ground, as shown in Figure 3. The on resistance of the transistor is not typically specified. Instead, a maximum sink current (IOL) is given for which the voltage drop across the transistor is below the output logical low-voltage level (VOL). Applying Ohm's Law yields Equation 1.

Figure 3: Open-collector topology and equivalent circuit. For Microchip's I2C EEPROM devices, the VOL specification is a maximum of 0.4V at an IOL of 3 mA, with other manufacturers devices in a similar range. Equation 1: Minimum pull-up resistance, allowing the bus to be pulled low.

For multiple devices on the bus, the minimum Rp is determined by the device with the lowest sink current. Total Bus Capacitance (CBUS) On the SCL and SDA lines, the capacitance includes all pins, connections, PCB traces and wire. Combined, this is referred to as the bus capacitance and, for long traces and cabling, this can be significant. The open-collector topology requires the external resistor to pull the line high when released. The pull-up resistor, coupled with the bus capacitance, has an RC time constant, which limits the rise time. This becomes significant with increasing clock frequencies, as less time is available for the line to rise. If the selected resistor value is too high, the line may not rise to a logical high before it is next pulled low. This is an important consideration for designs that feature many devices on a single bus, which often have higher bus capacitance.

2 of 4

1/12/2013 11:47 PM

Design calculations for robust I2C communications | EDN

http://www.edn.com/design/analog/4371297/Design-calculations-for-rob...

Figure 4: Charge time for transition between logical Low to High. Bus capacitance can be calculated from PCB trace lengths and published pin capacitance, or measured using capacitance probes or smart tweezers. If a precise calculation or measurement of the bus capacitance is not possible, an overestimated worst-case reading should provide a safe maximum-resistance value. Equation 2 is the general equation used to determine the voltage across a charging capacitive load, as a function of time. This allows for the calculation of the time required for the bus voltage to rise to a particular value, for a specific pull-up resistance and bus capacitance. Equation 2: General equation of charging a capacitor through a resistor.

We can then calculate the time (T1) for the voltage to rise to VIL; the time (T2) to rise to VIH; and, critically, the time between these two levels (TR), as shown in Figure 4. Since both VIL and VIH are products of Vdd, the equation is independent of supply voltage, since the Vdd terms cancel out.

The maximum rise time for a variety of operating voltages is specified by the I2C standard, and is determined by the pull-up resistance. From this time and the bus capacitance, we can calculate the maximum allowable pull-up resistance (Rp). For a 400 kHz clock frequency at 5V, the specified maximum rise time, (TR), is 300 ns, given the bus capacitance CBUS of 100 pF. Equation 3: Minimum pull-up resistance value to meet I2C rise-time standard.

Total High-Level Input Current (IIH) Even when no device is pulling down the line and it is a logical high, current continues to flow through the pull-up resistors. This current is caused by the leakage of the digital inputs of the devices on the bus, from low quality PCB materials and possibly from soldering residues. Some of these cannot be foreseen, but, assuming quality materials and good manufacturing practices, the input pin leakage is dominant. From Figure 2, the line needs to be above VIH to be regarded as logical high, when there are no devices pulling the bus low. The leakage current limits the maximum value of Rp, such that the voltage drop across it does not prevent the line from being pulled above VIH. It is also prudent to allow some guard margin on the VIH specification, to prevent noise spikes from bringing the voltage below the VIH level. For robust operation in a high-noise environment, the I2C specification recommends 0.2 Vdd as a suitable margin above VIH. Equation 4: Additional margin over logical high input level.

3 of 4

1/12/2013 11:47 PM

Design calculations for robust I2C communications | EDN

http://www.edn.com/design/analog/4371297/Design-calculations-for-rob...

The leakage of digital inputs is normally given in the datasheet of devices and, for Microchip's I2C EEPROM devices, the maximum input leakage current (IlIEE) is 1 A. The minimum components for a system are a microcontroller I2C master and an I2C slave device. For this example, assuming a microcontroller with 1 A input leakage (IlIMCU) and four I2C EEPROM devices, and allowing 100% margin, IIH is 10 A. Equation 5. Leakage current due to pin leakages for defined bus.

Applying Ohm's law, we can determine the maximum value for Rp that will meet these specifications Equation 6: Minimum pull-up resistance value to ensure logical high.

Resistor Value Calculation From the supply voltage, the bus capacitance and the leakage calculations, we have a range of values for RP.

The 50 K maximum caused by the leakage current can be discarded, since the bus capacitance dominates. As a result, the range of acceptable resistor values is

Designers should choose a value near the middle of the range, to provide as much guard banding as possible. For this example, a 2.2 K pull-up resistor would be ideal. Bus Speed vs. Power Consumption The pull-up resistors must be reduced in size, when increasing the bus speed or when there is significant bus capacitance. The lower-value resistors cause increased current draw, as each logical low on the bus creates a path to ground, negatively impacting power consumption. The bus speed can become a trade-off between completing tasks quickly and returning a system to a low-power idle state, versus the additional current draw created by the higher bus speed requirements. For applications with very low power budgets, SPI may be a better-suited bus protocol, since it uses driven lines, instead of open collectors.

Share your thoughts.

4 of 4

1/12/2013 11:47 PM

You might also like

- UNI/O Application NoteDocument8 pagesUNI/O Application NoteRhenan WafooNo ratings yet

- Design of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerDocument4 pagesDesign of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerSunil PandeyNo ratings yet

- Maximum Leakage Power Estimation For CMOS CircuitsDocument9 pagesMaximum Leakage Power Estimation For CMOS Circuitsowais74No ratings yet

- EDN Design Ideas 1998Document166 pagesEDN Design Ideas 1998chag1956100% (4)

- 2.8-GHz Prescaler Keeps Cost Down PDFDocument14 pages2.8-GHz Prescaler Keeps Cost Down PDFagmnm1962No ratings yet

- Slup 228Document32 pagesSlup 228cohama4No ratings yet

- PP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsDocument6 pagesPP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsEditorijset IjsetNo ratings yet

- Hsio Chapter11 BookDocument21 pagesHsio Chapter11 BookAkshay PNo ratings yet

- Design of A Low-Dropout Linear RegulatorDocument4 pagesDesign of A Low-Dropout Linear RegulatorParindraNo ratings yet

- Gabriel Rincon-Mora-Analog IC Design With Low-Dropout Regulators (LDOs) (Electronic Engineering) (2009) PDFDocument373 pagesGabriel Rincon-Mora-Analog IC Design With Low-Dropout Regulators (LDOs) (Electronic Engineering) (2009) PDFNguyen HaNo ratings yet

- ICIEAPaper Voltage Sags PsimDocument8 pagesICIEAPaper Voltage Sags Psimjefao_MMANo ratings yet

- Flyback Converter Without SnubberDocument2 pagesFlyback Converter Without SnubberReena ElangovanNo ratings yet

- dt97 3Document6 pagesdt97 3ofilipNo ratings yet

- Precise Kilometer Calculation by Underground Cable Fault DetectorDocument27 pagesPrecise Kilometer Calculation by Underground Cable Fault DetectorAbhinavNo ratings yet

- "Power Line Communication": 1.dhiraj S. Bhojane 2.saurabh R. Chaudhari 3. Prakash D. More 4.eshant G. RajgureDocument7 pages"Power Line Communication": 1.dhiraj S. Bhojane 2.saurabh R. Chaudhari 3. Prakash D. More 4.eshant G. RajgureChanna SenavirathnaNo ratings yet

- EE 22442 - Embedded Systems Fall 2013: Chapter ThreeDocument32 pagesEE 22442 - Embedded Systems Fall 2013: Chapter ThreeFarooq BushnaqNo ratings yet

- 2020 Aip Switch Node Layout Considerations For Emc - r1.0Document5 pages2020 Aip Switch Node Layout Considerations For Emc - r1.0OmeLeila KhaliliNo ratings yet

- Tips N Tricks-MicrochipDocument20 pagesTips N Tricks-Microchipbanana567No ratings yet

- Embedded System Timing Analysis Basics: Part 2 - Fan-Out & Loading AnalysisDocument6 pagesEmbedded System Timing Analysis Basics: Part 2 - Fan-Out & Loading AnalysisMuni TheBossNo ratings yet

- Remote Tracking and Breaking System For VehiclesDocument5 pagesRemote Tracking and Breaking System For VehiclesseventhsensegroupNo ratings yet

- MC13783 Buck and Boost Inductor Sizing: Application NoteDocument8 pagesMC13783 Buck and Boost Inductor Sizing: Application NoteSyed Qaseem AliNo ratings yet

- 1MRG008054 en Application Note Function Description For High Impedance Busbar ProtectionDocument13 pages1MRG008054 en Application Note Function Description For High Impedance Busbar ProtectionOsama Ahmad Chaudhary100% (1)

- Buck Converter Design DemystifiedDocument6 pagesBuck Converter Design DemystifiedEric MorissetNo ratings yet

- 4200 Pulsed-IV ApplicationsGuideDocument75 pages4200 Pulsed-IV ApplicationsGuideStefan-Marian IordacheNo ratings yet

- Stop Fried Boards, Garbled Data: Proper Surge ProtectionDocument2 pagesStop Fried Boards, Garbled Data: Proper Surge ProtectionMansoor AbbasNo ratings yet

- Wair Ya 2010Document6 pagesWair Ya 2010abhishek shuklaNo ratings yet

- Low Power ThesisDocument6 pagesLow Power Thesistiffanybarbermobile100% (2)

- DC Lab ManualDocument27 pagesDC Lab ManualKhushboo ManchandaNo ratings yet

- Arduino-based cable fault detection system locates issuesDocument7 pagesArduino-based cable fault detection system locates issuesUmair Mansoor100% (1)

- TECHNICAL BRIEF: North America 60Hz: Calculating AC Line Voltage Rise For IQ-Series Micros With Q CableDocument24 pagesTECHNICAL BRIEF: North America 60Hz: Calculating AC Line Voltage Rise For IQ-Series Micros With Q CableHernan RojasNo ratings yet

- Arduino Based Underground Cable Fault Detection: Submitted By: AJIT .P. SINGH Faran AnsariDocument19 pagesArduino Based Underground Cable Fault Detection: Submitted By: AJIT .P. SINGH Faran Ansariq8400No ratings yet

- A 93.7% Peak Efficiency DC-DC Buck Converter With All-Pass Network Based Passive Level Shifter in 55 NM CMOSDocument4 pagesA 93.7% Peak Efficiency DC-DC Buck Converter With All-Pass Network Based Passive Level Shifter in 55 NM CMOSRaghvendra DeshpandeNo ratings yet

- Sub-Threshold Adiabatic Logic For Low Power ApplicationsDocument7 pagesSub-Threshold Adiabatic Logic For Low Power ApplicationsarcherselevatorsNo ratings yet

- Field-Effect Transistors and Transistor AmplifiersDocument6 pagesField-Effect Transistors and Transistor Amplifierssuper_lativoNo ratings yet

- 004 Pwm-OcxiDocument7 pages004 Pwm-OcxiNeodymeNo ratings yet

- 2020 IC Design Contest: Full-Custom CategoryDocument6 pages2020 IC Design Contest: Full-Custom CategoryE94086018陳寧文No ratings yet

- PC Based Appliances Controller Ag 111508Document8 pagesPC Based Appliances Controller Ag 111508Patel PratikNo ratings yet

- Simulation of Extra High Voltage Long Transmission LinesDocument18 pagesSimulation of Extra High Voltage Long Transmission LinesAaryarohit NaskarNo ratings yet

- Coiled For ProtectionDocument6 pagesCoiled For ProtectionAbdelsalam ElhaffarNo ratings yet

- A Fully Isolated Delta-Sigma ADC For Shunt Based Current SensingDocument9 pagesA Fully Isolated Delta-Sigma ADC For Shunt Based Current Sensingpramani90No ratings yet

- Flyback Converter Design ThesisDocument8 pagesFlyback Converter Design Thesisleanneuhlsterlingheights100% (2)

- 1MRG008054 en Application Note Function Description For High Impedance Busbar Protection PDFDocument13 pages1MRG008054 en Application Note Function Description For High Impedance Busbar Protection PDFnp_bhuvaneswarNo ratings yet

- Layout Design of CMOS Buffer To Reduce Area and PowerDocument4 pagesLayout Design of CMOS Buffer To Reduce Area and PowerIJIRSTNo ratings yet

- Basic Stamp - Digital Signal ConditioningDocument27 pagesBasic Stamp - Digital Signal ConditioningRussellNo ratings yet

- Power Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationDocument5 pagesPower Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationM ANo ratings yet

- Low Power Techniques For VLSI DesignDocument6 pagesLow Power Techniques For VLSI DesignjainatinNo ratings yet

- Capacitance Adapter For Multimeter: (Document Subtitle)Document11 pagesCapacitance Adapter For Multimeter: (Document Subtitle)Kashif Hassan100% (1)

- Underground Cable Fault Distance Locator: Project OnDocument31 pagesUnderground Cable Fault Distance Locator: Project OnsmartyNo ratings yet

- Digital and Pulse-Train Conditioning: Digital I/O InterfacingDocument6 pagesDigital and Pulse-Train Conditioning: Digital I/O InterfacingcoolhemakumarNo ratings yet

- Inrush Current ControlDocument8 pagesInrush Current ControlbrahimNo ratings yet

- Design and Simulation of RF Energy Extracting CircuitsDocument28 pagesDesign and Simulation of RF Energy Extracting CircuitsHaresh SinghNo ratings yet

- Lic QB With AnswerDocument29 pagesLic QB With AnswerNoddy SenNo ratings yet

- An Introduction To Telephone Line Interfacing Using The PIC Micro ControllerDocument46 pagesAn Introduction To Telephone Line Interfacing Using The PIC Micro Controllerayaz_shiraziNo ratings yet

- Current Differential Line Protection Setting ConsiderationsDocument28 pagesCurrent Differential Line Protection Setting ConsiderationskankokwahNo ratings yet

- 5 Volts To 3.3Document3 pages5 Volts To 3.3pablorc30No ratings yet

- Mobile Charging System Using Radio Frequency Energy HarvestingDocument3 pagesMobile Charging System Using Radio Frequency Energy HarvestingBrightworld ProjectsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Highly Integrated Gate Drivers for Si and GaN Power TransistorsFrom EverandHighly Integrated Gate Drivers for Si and GaN Power TransistorsNo ratings yet

- 08126260Document6 pages08126260Anonymous DGq0O15nNzNo ratings yet

- A Quasi-Optical: Converter With BifocalDocument5 pagesA Quasi-Optical: Converter With BifocalAnonymous DGq0O15nNzNo ratings yet

- Causal and Non Causal SystemsDocument9 pagesCausal and Non Causal SystemsAnonymous DGq0O15nNzNo ratings yet

- Microsoft PowerPoint - Sample1Document6 pagesMicrosoft PowerPoint - Sample1Anonymous DGq0O15nNzNo ratings yet

- 17 MTRDCDocument7 pages17 MTRDCAnonymous DGq0O15nNzNo ratings yet

- Microwave Tube Types: Klystrons, TWTs, Magnetrons & MoreDocument4 pagesMicrowave Tube Types: Klystrons, TWTs, Magnetrons & MoreAnonymous DGq0O15nNzNo ratings yet

- HSST Computer Science 2004Document10 pagesHSST Computer Science 2004dreams299No ratings yet

- Syllabus STA 20170727 PDFDocument2 pagesSyllabus STA 20170727 PDFgagandeep anandNo ratings yet

- Ranking B SchoolsDocument2 pagesRanking B SchoolsAnonymous DGq0O15nNzNo ratings yet

- Stretchable Optical Waveguides: © 2014 Optical Society of AmericaDocument12 pagesStretchable Optical Waveguides: © 2014 Optical Society of AmericaAnonymous DGq0O15nNzNo ratings yet

- The Taurat and The Injeel: A Lamp and A LightDocument2 pagesThe Taurat and The Injeel: A Lamp and A LightAnonymous DGq0O15nNz100% (2)

- HSST Computer Science 2011Document12 pagesHSST Computer Science 2011Anonymous DGq0O15nNzNo ratings yet

- Approved Annual Programme 2014Document1 pageApproved Annual Programme 2014Kiran KumarNo ratings yet

- Thesis-Millimetre Wave, Quasi-Optical ComplexDocument273 pagesThesis-Millimetre Wave, Quasi-Optical ComplexAnonymous DGq0O15nNzNo ratings yet

- General Knowledge PRASAR BHARTI PDFDocument0 pagesGeneral Knowledge PRASAR BHARTI PDFSrinivas SaiNo ratings yet

- Intelligence Bureau Government of India: (Ministry of Home Affairs)Document1 pageIntelligence Bureau Government of India: (Ministry of Home Affairs)Anonymous DGq0O15nNzNo ratings yet

- Teaching NotesDocument76 pagesTeaching NotesAnonymous DGq0O15nNzNo ratings yet

- India General Knowledge 2013 For Competitive ExamsDocument184 pagesIndia General Knowledge 2013 For Competitive Examsaekalaivan12100% (1)

- Taraweeh Tasbihaat EnglishDocument2 pagesTaraweeh Tasbihaat EnglishAnonymous DGq0O15nNzNo ratings yet

- Selected The Suitable Word Which Bears The Same Relation With The Third Word As The Relation of The Second With The FirstDocument50 pagesSelected The Suitable Word Which Bears The Same Relation With The Third Word As The Relation of The Second With The FirstAnonymous DGq0O15nNzNo ratings yet

- Governors of KeralaDocument13 pagesGovernors of KeralaAnonymous DGq0O15nNzNo ratings yet

- Carnegie Mellon Virtual Memory ConceptsDocument36 pagesCarnegie Mellon Virtual Memory ConceptsMalu MohanNo ratings yet

- Opto ElectronicsDocument12 pagesOpto ElectronicsAnonymous DGq0O15nNzNo ratings yet

- Oe 21 22 27286Document5 pagesOe 21 22 27286Anonymous DGq0O15nNzNo ratings yet

- Trends in OptiicsDocument30 pagesTrends in OptiicsAnonymous DGq0O15nNzNo ratings yet

- MuxDocument24 pagesMuxHamdi RezaNo ratings yet

- DuanselingDocument20 pagesDuanselingB Rajesh ReddyNo ratings yet

- General Properties of Linear and Nonlinear Systems: Key PointsDocument11 pagesGeneral Properties of Linear and Nonlinear Systems: Key PointsPatrick TenederoNo ratings yet

- Paper23 PGDMM Public Procurement MCQ Sept2021Document25 pagesPaper23 PGDMM Public Procurement MCQ Sept2021Gagan VermaNo ratings yet

- Analog Communication Interview Questions and AnswersDocument34 pagesAnalog Communication Interview Questions and AnswerssarveshNo ratings yet

- Douglas Frayne Sargonic and Gutian Periods, 2334-2113 BCDocument182 pagesDouglas Frayne Sargonic and Gutian Periods, 2334-2113 BClibrary364100% (3)

- CHECK LIST FOR HIGH RISE BUILDING NOCDocument15 pagesCHECK LIST FOR HIGH RISE BUILDING NOCNedunuri.Madhav Murthy100% (2)

- ICS Technical College Prospectus 2024 Edition 1Document36 pagesICS Technical College Prospectus 2024 Edition 1samuel287kalumeNo ratings yet

- 4PW16741-1 B EKBT - Bufftertank - Installation Manuals - EnglishDocument6 pages4PW16741-1 B EKBT - Bufftertank - Installation Manuals - EnglishBernard GaterNo ratings yet

- ATM ReportDocument16 pagesATM Reportsoftware8832100% (1)

- Etoposide JurnalDocument6 pagesEtoposide JurnalShalie VhiantyNo ratings yet

- Materials Science & Engineering A: Alena Kreitcberg, Vladimir Brailovski, Sylvain TurenneDocument10 pagesMaterials Science & Engineering A: Alena Kreitcberg, Vladimir Brailovski, Sylvain TurenneVikrant Saumitra mm20d401No ratings yet

- Rigor Mortis and Lividity in Estimating Time of DeathDocument2 pagesRigor Mortis and Lividity in Estimating Time of DeathfunnyrokstarNo ratings yet

- ATLAS CYLINDER LUBRICATOR MANUALDocument36 pagesATLAS CYLINDER LUBRICATOR MANUALKaleb Z king webNo ratings yet

- Assurance Audit of Prepaid ExpendituresDocument7 pagesAssurance Audit of Prepaid ExpendituresRatna Dwi YulintinaNo ratings yet

- Newly Constructed Masculinity' in Mahesh Dattani's Dance Like A ManDocument4 pagesNewly Constructed Masculinity' in Mahesh Dattani's Dance Like A ManIJELS Research JournalNo ratings yet

- Schedule FinalDocument6 pagesSchedule FinalJamora ManilynNo ratings yet

- Understanding Urbanization & Urban Community DevelopmentDocument44 pagesUnderstanding Urbanization & Urban Community DevelopmentS.Rengasamy89% (28)

- Assignment No. 8 (Culture 1) : Discuss The Significance of Montessori Cultural Exercises.? Hfodhfsfnsfsfsajk AnsDocument10 pagesAssignment No. 8 (Culture 1) : Discuss The Significance of Montessori Cultural Exercises.? Hfodhfsfnsfsfsajk Anseman zahraNo ratings yet

- Upper Six 2013 STPM Physics 2 Trial ExamDocument11 pagesUpper Six 2013 STPM Physics 2 Trial ExamOw Yu Zen100% (2)

- PPPoE Packet Format - HCNADocument6 pagesPPPoE Packet Format - HCNARobert Sanchez OchochoqueNo ratings yet

- French Ox Cheek Stew with MushroomsDocument2 pagesFrench Ox Cheek Stew with MushroomsMihai LeancăNo ratings yet

- ExportDocument18 pagesExportDolon MukherjeeNo ratings yet

- Unit 5 Vocabulary Basic 1 Match 1-10 With A-J To Make Innovations and InventionsDocument6 pagesUnit 5 Vocabulary Basic 1 Match 1-10 With A-J To Make Innovations and InventionsCristina Garcia50% (2)

- Genigraphics Poster Template 36x48aDocument1 pageGenigraphics Poster Template 36x48aMenrie Elle ArabosNo ratings yet

- Volume 4-6Document757 pagesVolume 4-6AKNo ratings yet

- NVH PDFDocument3 pagesNVH PDFSubhendu BarisalNo ratings yet

- Armitage Tutorial for Cyber Attack ManagementDocument54 pagesArmitage Tutorial for Cyber Attack Managementworkmumbai3870No ratings yet

- German BasicDocument60 pagesGerman BasicchahirNo ratings yet

- 74VHCU04Document6 pages74VHCU04Alexandre S. CorrêaNo ratings yet

- Starting an NGO - A Guide to the Key StepsDocument22 pagesStarting an NGO - A Guide to the Key StepsBadam SinduriNo ratings yet

- Iwwusa Final Report IdsDocument216 pagesIwwusa Final Report IdsRituNo ratings yet

- Release emotions with simple questionsDocument10 pagesRelease emotions with simple questionsDubravko ThorNo ratings yet