Professional Documents

Culture Documents

Chapter01 Exercises

Uploaded by

Đỗ Công ThànhOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter01 Exercises

Uploaded by

Đỗ Công ThànhCopyright:

Available Formats

dce

2010

COMPUTER ARCHITECTURE CE2010

BK

TP.HCM

Faculty of Computer Science and Engineering Department of Computer Engineering Nam Ho

dce

2010

Chapter 1

Computer Abstraction and Technology - Exercises

Adapted from Computer Organization and Design, 4th Edition, Patterson & Hennessy, 2008

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

dce

2010

Pitfall: MIPS as a Performance Metric

MIPS: Millions of Instructions Per Second

Doesnt account for

Differences in ISAs between computers Differences in complexity between instructions

Instruction count MIPS = Execution time 106 Instruction count Clock rate = = Instruction count CPI CPI 106 6 10 Clock rate

CPI varies between programs on a given CPU

Computer Architecture Chapter 1 2010, Dr. Dinh Duc Anh Vu 3

dce

2010

Using MIPS

There are three problems with MIPS:

MIPS specifies the instruction execution rate but not the capabilities of the instructions MIPS varies between programs on the same computer MIPS can vary inversely with performance (see the next example)

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

dce

2010

Exercise 1

Consider the machine with the following three instruction classes and CPI:

CPI for this instruction class A B C 1 2 3

CPI

Now suppose we measure the code for the same program from two different compilers and obtain the following data:

Code from Compiler 1 Compiler 2 Instruction count in (billons) for each instruction class A B C 5 1 1 10 1 1

Assume that the machines clock rate is 500 MHz. Which code sequence will execute faster according to execution time ? According to MIPS?

2010, Dr. Dinh Duc Anh Vu 5

Computer Architecture Chapter 1

dce

2010

Exercise 1

Using the formula: CPU clock cycles

Clock Cycles = (CPIi Instruction Count i )

i=1 n

Execution time = CPU clock cycles/clock rate

Compiler 1:

CPU clock cycles = (5 x 1 + 1 x 2 + 1 x 3) x 109 = 10 x 109 cycles Execution time = (10 x 109)/500 x 106 = 20 seconds

Compiler 2:

CPU clock cycles = (10 x 1 + 1 x 2 + 1 x 3) x 109 = 15 x 109 cycles Execution time = (15 x 109)/(500 x 106) = 30 seconds

Therefore compiler 1 generates a faster program

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

dce

2010

Exercise 1

Instruction count MIPS = Execution Time 106

Compiler 1: Compiler 2:

(5 + 1 + 1) 109 MIPS = = 350 6 20 10 (10 + 1 + 1) 109 MIPS = = 400 6 30 10

Although compiler 2 has a higher MIPS rating, the code from generated by compiler 1 runs faster

Computer Architecture Chapter 1 2010, Dr. Dinh Duc Anh Vu 7

dce

2010

Exercise 2

PowerPC G4 can execute 4 instructions/cycle with a clock rate 867 MHz. What is the MIPS rate ? Answer:

CPI = 1/4 MIPS = 1/(CPI x Cycle Time x 106) MIPS = Clock Rate/CPI x 106 MIPS = 4 x 867 = 3468

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

dce

2010

Speedup - Amdahls Law

Speedup = Execution Time Old --------------------------------Execution Time New

1

Tbefore improved = --------------Timproved

Speedup = ----------------------------------, n is the improvement factor 1 fenhanced + fenhanced/n Taffected fenhanced = ----------------, Tbefore improved = Taffected + Tunaffected Tbefore improved

Timproved =

Taffected + Tunaffected improvement factor

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

dce

2010

Exercise 3

Consider the implementation of a ISA. The clock rate is 2Ghz. What is the execution time of the following program ?

Arith Instructions CPI 500 1 Store 50 5 Load 100 5 Branch 50 2

Execution Time = (500 1 + 50 5 + 100 5 + 50 2) 0.5 109 = 675 ns If the number of load instructions can be reduced by one-half, what is the speedup and the CPI? Execution Time = (500 1 + 50 5 + 50 5 + 50 2) 0.5 109 = 550 ns Speedup = 675/550 = 1.22 CPI = Execution Time x Clock rate/ Instruction Count CPI = 550 x 10-9 x 2 x 109/700 = 1.57

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

10

dce

2010

Exercise 4

Speedup = Execution Time Old --------------------------------Execution Time New

1

Tbefore improved = --------------Timproved

Prove that Speedup = ---------------------------------1 fenhanced + fenhanced/n n is the improvement factor Taffected fenhanced = ---------------Tbefore improved Tbefore improved = Taffected + Tunaffected

Taffected Timproved = + Tunaffected improvement factor

Computer Architecture Chapter 1 2010, Dr. Dinh Duc Anh Vu 11

dce

2010

Exercise 5

A common transformation required in graphics processors is square root. Implementations of floating-point (FP) square root vary significantly in performance, especially among processors designed for graphics. Suppose FP square root (FPSQR) is responsible for 20% of the execution time of a critical graphics benchmark. One proposal is to enhance the FPSQR hardware and speed up this operation by a factor of 10. The other alternative is just to try to make all FP instructions in the graphics processor run faster by a factor of 1.6; FP instructions are responsible for half of the execution time for the application. Compare these two design alternatives.

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

12

dce

2010

Exercise 5

SpeedupFPSQR

1 = = 1.22 = 0.2 0.82 (1 0.2) + 10 1

SpeedupFP =

1 = = 1.23 0.5 0.8125 (1 0.5) + 1.6

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

13

dce

2010

Geometric Mean

GM =

n

Execution time ratio

i =1

The advantage of the geometric mean is that

It is independent of the running times of the individual programs And it doesnt matter which computer is used for normalization.

The drawback to using geometric means of execution times is that

They violate our fundamental principle of performance measurement, they do not predict execution time

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

14

dce

2010

Geometric Mean

A and B have the same performance. Performance of C is 0.63 of A or B. Unfortunately, the total execution time of A is 10 times longer than that of B, and B in turn is about 3 times longer than C.

2010, Dr. Dinh Duc Anh Vu 15

Computer Architecture Chapter 1

dce

2010

Exercise 6

Show that the Geometric Mean doesnt matter which computer is used for normalization.

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

16

dce

2010

Fallacy: MFLOPS

MFLOPS: Million Floating-point Operations Per Second Fallacy: MFLOPS is a consistent and useful measure of performance. For example, the Cray C90 has no divide instruction, while the Intel Pentium has divide, square root, sine, and cosine

Computer Architecture Chapter 1

2010, Dr. Dinh Duc Anh Vu

17

dce

2010

Exercise 7

Consider the programs in the following table, running on a processor with clock rate = 3GHz. Find the MFLOPS for the program a, b.

Program a: FPop = 106 0.4 = 4 105, clockcylesfp = CPI No. FP instr. = 4 105 Tfp = 4 105 0.33 109 = 1.32 104 then MFLOPS = 3.03 103 Program b: FPop = 3 106 0.4 = 1.2 106, clockcylesfp = CPI No. FP instr. = 0.70 1.2 106 Tfp = 0.84 106 0.33 109 = 2.77 104 then MFLOPS = 4.33 103

Computer Architecture Chapter 1 2010, Dr. Dinh Duc Anh Vu 18

You might also like

- Fig 8 5-7Document4 pagesFig 8 5-7Đỗ Công ThànhNo ratings yet

- JavaCollections AbbrevDocument21 pagesJavaCollections Abbrevankitgaur36No ratings yet

- Chapter05 ExercisesDocument11 pagesChapter05 ExercisesĐỗ Công ThànhNo ratings yet

- Chapter04 ExercisesDocument8 pagesChapter04 ExercisesĐỗ Công ThànhNo ratings yet

- Chapter03 ExercisesDocument6 pagesChapter03 ExercisesĐỗ Công ThànhNo ratings yet

- COMPUTER ARCHITECTURE EXERCISESDocument20 pagesCOMPUTER ARCHITECTURE EXERCISESĐỗ Công ThànhNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Stator Generator EolianDocument40 pagesStator Generator EolianCatalin BordeiNo ratings yet

- Design of Bulk CarrierDocument7 pagesDesign of Bulk CarrierhoangductuanNo ratings yet

- 0620 Chemistry: MARK SCHEME For The March 2015 SeriesDocument6 pages0620 Chemistry: MARK SCHEME For The March 2015 SeriesDark GreenNo ratings yet

- Word Processing and Desktop Publishing SoftwareDocument24 pagesWord Processing and Desktop Publishing SoftwareMubarak KashiNo ratings yet

- Ae53 Ac53 At53Document4 pagesAe53 Ac53 At53M Taher BamyaniNo ratings yet

- DefinitionsHypothesesPosterior Analytics (Landor)Document12 pagesDefinitionsHypothesesPosterior Analytics (Landor)Daniel Rojas UNo ratings yet

- Pipesim Model Management Program: For Reservoir, Production, and Process ModelingDocument2 pagesPipesim Model Management Program: For Reservoir, Production, and Process ModelingMauricio AlvaradoNo ratings yet

- Chemical Composition, Properties, and Standards of Steel Grade 42CrMo4 (1.7225Document1 pageChemical Composition, Properties, and Standards of Steel Grade 42CrMo4 (1.7225ADITYA_PATHAK100% (1)

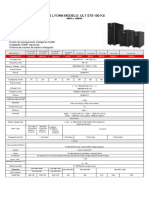

- Ups Lyonn Modelo: Ult St5-100 KS: 10KVA A 120KVADocument1 pageUps Lyonn Modelo: Ult St5-100 KS: 10KVA A 120KVASebastian Matias CruzNo ratings yet

- ZIEHL ABEGG Main Catalogue Centrifugal Fans With IEC Standard MotoDocument285 pagesZIEHL ABEGG Main Catalogue Centrifugal Fans With IEC Standard MotoTomislav BrezicNo ratings yet

- Ordinary Dierential Equations Principles and ApplicationsDocument349 pagesOrdinary Dierential Equations Principles and ApplicationsSokratis Spyrou100% (1)

- (Advances in Cryogenic Engineering 37) Takayuki Kishi, Mizuo Kudo, Hiromasa Iisaka (Auth.), R. W. Fast (Eds.) - Advances in Cryogenic Engineering-Springer US (1991)Document729 pages(Advances in Cryogenic Engineering 37) Takayuki Kishi, Mizuo Kudo, Hiromasa Iisaka (Auth.), R. W. Fast (Eds.) - Advances in Cryogenic Engineering-Springer US (1991)ksvvijNo ratings yet

- 925E II 24 PG A4 Broch - 12 - 2020 - DCECDocument13 pages925E II 24 PG A4 Broch - 12 - 2020 - DCECekkyagungNo ratings yet

- L6565 DatasheetDocument17 pagesL6565 DatasheetJose BenavidesNo ratings yet

- Text Linguistics and Classical Studies - Facebook Com LinguaLIBDocument129 pagesText Linguistics and Classical Studies - Facebook Com LinguaLIBEnglish Buzz100% (1)

- Preparation Exam API 510:N°01 QuestionsDocument3 pagesPreparation Exam API 510:N°01 QuestionskorichiNo ratings yet

- CM-4G-GPS Quick Guide: Short Guide How To Start Using CM-GPRS ModuleDocument4 pagesCM-4G-GPS Quick Guide: Short Guide How To Start Using CM-GPRS Modulezakki ahmadNo ratings yet

- SM 1201r9 UsxrayDocument500 pagesSM 1201r9 UsxrayMurat KaanNo ratings yet

- Detailed Geotechnical ReportDocument29 pagesDetailed Geotechnical Reportathar abbasNo ratings yet

- Beyond SVGFDocument66 pagesBeyond SVGFLiliana QueiroloNo ratings yet

- Unitplan2 Chi-SquareDocument11 pagesUnitplan2 Chi-Squareapi-285549920No ratings yet

- HP LaserJet 5P - 6P Service Manual (Proper)Document116 pagesHP LaserJet 5P - 6P Service Manual (Proper)maroudasp100% (1)

- On Handwritten Digit RecognitionDocument15 pagesOn Handwritten Digit RecognitionAnkit Upadhyay100% (1)

- UDP Control and Monitoring With PIC Microcontroller - StudentCompanion PDFDocument14 pagesUDP Control and Monitoring With PIC Microcontroller - StudentCompanion PDFVport PortNo ratings yet

- Carbon 06 00052Document17 pagesCarbon 06 00052Elbahi DjaalabNo ratings yet

- Grade 6 MathDocument12 pagesGrade 6 Mathapi-264682510No ratings yet

- UNIT 7 - Atomic TransactionsDocument30 pagesUNIT 7 - Atomic TransactionslavanyatumuNo ratings yet

- Simple Backup/Restore Utility With SQL-: Introduction To SQL-DMODocument8 pagesSimple Backup/Restore Utility With SQL-: Introduction To SQL-DMOZaeni Marjiyanto, A.mdNo ratings yet

- Reso Course PlannerDocument2 pagesReso Course PlannerSnehasishGhosh100% (1)

- Spreader BeamDocument7 pagesSpreader BeamAnonymous sfkedkymNo ratings yet