Professional Documents

Culture Documents

EP4SGX360

Uploaded by

Manjunath ReddyOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EP4SGX360

Uploaded by

Manjunath ReddyCopyright:

Available Formats

Section I.

Stratix IV Device Datasheet

This section includes the following chapters:

Chapter 1, DC and Switching Characteristics

Revision History

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the full handbook.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

I2

Section I: Stratix IV Device Datasheet

Stratix IV Device Handbook, Volume 4

December 2008

Altera Corporation

1. DC and Switching Characteristics

SIV54001-2.1

Electrical Characteristics

This chapter covers the electrical characteristics for Stratix IV devices.

Operating Conditions

When Stratix IV devices are implemented in a system, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Stratix IV devices, system designers must consider the following operating requirements. Stratix IV devices are offered in both commercial and industrial grades. Commercial devices are offered in -2 (fastest), -2x, -3, and -4 speed grades.

Absolute Maximum Ratings

Absolute maximum ratings define the maximum operating conditions for Stratix IV devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied at these conditions. 1 Conditions beyond those listed in Table 11 and Table 12 may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

Table 11. Stratix IV Device Absolute Maximum Ratings Symbol VC C VC CP T VC CP GM VC CA UX VC CB AT VC CP D VC CIO VC C_C LK IN VC CD_P LL VC CA _PLL VI TJ TS TG Description Core voltage and periphery circuitry power supply Power supply for programmable power technology Configuration pins power supply Auxiliary supply for the programmable power technology Battery back-up power supply for design security volatile key register I/O pre-driver power supply I/O power supply Differential clock input power supply PLL digital power supply PLL analog power supply DC input voltage Operating junction temperature Storage temperature (No bias) Minimum -0.5 -0.5 -0.5 -0.5 -0.5 -0.5 -0.5 -0.5 -0.5 -0.5 -0.5 -40 -65 Maximum 1.35 2.25 3.75 3.75 3.75 3.75 3.9 3.75 1.35 3.75 4.0 100 150 Unit V V V V V V V V V V V C C

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

12

Table 12. Stratix IV GX Transceiver Power Supply Absolute Maximum Ratings Symbol VC CA _L VC CA _R VC CHIP_L VC CHIP_R VC CR_L VC CR_R VC CT_L VC CT_R VC CL_GXB Ln (2) VC CL_GXB Rn (2) VC CH_GX BLn (2) VC CH_GX BRn (2)

Note to Table 12:

(1) n=0, 1, 2, 3

Description Transceiver high voltage power (left side) Transceiver high voltage power (right side) Transceiver HIP digital power (left side) Transceiver HIP digital power (right side) Receiver power (left side) Receiver power (right side) Transmitter power (left side) Transmitter power (right side) Transceiver clock power (left side) Transceiver clock power (right side) Transmitter output buffer power (left side) Transmitter output buffer power (right side)

Minimum

Maximum 3.15 / 2.625 3.15 / 2.625 0.99 0.99 1.21 1.21 1.21 1.21 1.21 1.21 1.54 / 1.65 1.54 / 1.65

Unit V V V V V V V V

Maximum Allowed Overshoot/Undershoot Voltage During transitions, input signals may overshoot to the voltage shown in Table 13 and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns. Table 13 lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime. The maximum allowed overshoot duration is specified as a percentage of high-time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle. For example, a signal that overshoots to 4.3 V can only be at 4.3 V for ~5% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 5/10ths of a year.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

13

Table 13. Maximum Allowed Overshoot During Transitions Symbol Vi (AC) Description AC input voltage Condition 4.0 V 4.05 V 4.1 V 4.15 V 4.2 V 4.25 V 4.3 V 4.35 V 4.4 V 4.45 V 4.5 V 4.55 V 4.6 V Overshoot Duration as % of High Time 100.000 79.330 46.270 27.030 15.800 9.240 5.410 3.160 1.850 1.080 0.630 0.370 0.220 Unit % % % % % % % % % % % % %

Recommended Operating Conditions

This section lists the functional operation limits for AC and DC parameters for Stratix IV devices. The steady-state voltage and current values expected from Stratix IV devices are provided in Table 14. All supplies must be strictly monotonic, without plateaus.

Table 14. Stratix IV Device Recommended Operating Conditions (Part 1 of 2) Symbol VC C VC CP T VC CA UX VC CP D VC CIO Description Core voltage and periphery circuitry power supply Power supply for programmable power technology Auxiliary supply for the programmable power technology I/O pre-driver (3.0 V) power supply I/O pre-driver (2.5 V) power supply I/O buffers (3.0-V) power supply I/O buffers (2.5-V) power supply I/O buffers (1.8-V) power supply I/O buffers (1.5-V) power supply I/O buffers (1.2-V) power supply VC CP GM Configuration pins (3.0-V) power supply Configuration pins (2.5-V) power supply Configuration pins (1.8-V) power supply VC CA _PLL VC CD_P LL PLL analog voltage regulator power supply PLL digital voltage regulator power supply Condition Minimum 0.87 1.45 2.375 2.85 2.375 2.85 2.375 1.71 1.425 1.14 2.85 2.375 1.71 2.375 0.87 Typical 0.90 1.50 2.5 3 2.5 3 2.5 1.8 1.5 1.2 3 2.5 1.8 2.5 0.90 Maximum 0.93 1.55 2.625 3.15 2.625 3.15 2.625 1.89 1.575 1.26 3.15 2.625 1.89 2.625 0.93 Unit V V V V V V V V V V V V V V V

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

14

Table 14. Stratix IV Device Recommended Operating Conditions (Part 2 of 2) Symbol VC C_C LK IN VC CB AT VI VO TJ tRAM P Description Differential clock input power supply Battery back-up power supply (For design security volatile key register) DC input voltage Output voltage Operating junction temperature Power supply ramp time Condition Commercial Industrial Normal POR Fast POR (1)

Note to Table 14:

(1) If the PORSEL pin is connected to VC C, all supplies must ramp up within 12 ms.

Minimum 2.375 1.2 0.5 0 0 40 0.05 0.05

Typical 2.5 3.0

Maximum 2.625 3.3 3.6 VC CIO 85 100 100 12

Unit V V V V C C ms ms

Table 15 shows the transceiver power supply recommended operating conditions.

Table 15. Stratix IV GX Transceiver Power Supply Recommended Operating Conditions Symbol VC CA _L VC CA _R VC CHIP_L (1) VC CHIP_R (1) VC CR_L VC CR_R VC CT_L VC CT_R VC CL_GXB Ln (2) VC CL_GXB Rn (2) VC CH_GX BLn (2) VC CH_GX BRn (2)

Note to Table 15:

(1) If VCCHIP_L is connected to the same power supply source as VCC, the tighter VCC recommended operating conditions need to be met. (2) n=0, 1, 2, 3

Description Transceiver high voltage power (left side) Transceiver high voltage power (right side) Transceiver HIP digital power (left side) Transceiver HIP digital power (right side) Receiver power (left side) Receiver power (right side) Transmitter power (left side) Transmitter power (right side) Transceiver clock power (left side) Transceiver clock power (right side) Transmitter output buffer power (left side) Transmitter output buffer power (right side)

Minimum 2.85/2.375 0.855 1.045 1.045 1.045 1.33/1.425

Typical 3.0/2.5 0.9 1.1 1.1 1.1 1.4/1.5

Maximum 3.15/2.625 0.945 1.155 1.155 1.155 1.47/1.575

Unit V V V V V V V V

DC Characteristics

This section lists the supply current, I/O pin leakage current, input pin capacitance, on-chip termination tolerance, and hot socketing specifications. Supply Current Standby current is the current the device draws after the device is configured, with no inputs or outputs toggling and no activity in the device. Since these currents vary largely with resources used, use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

15

Table 16 lists supply current specifications for VCC_CLKIN , VCCPGM , and VCCAUX. Use the EPE to get supply current estimates for remaining power supplies.

Table 16. Supply Current Specifications for VCC_CLKIN, VCCPGM , and VCCAUX Symbol I CLKIN IPGM IAUX Parameter VCC_CLKIN current specifications VCCPGM current specifications VCCAUX current specification Min 0 0 0 Max 250 250 250 Unit mA mA mA

I/O Pin Leakage Current Table 17 defines the Stratix IV I/O pin leakage current specifications.

Table 17. Stratix IV I/O Pin Leakage Current Symbol II IOZ Description Input pin Tri-stated I/O pin Conditions VI = 0V to VCC IOM AX VO = 0V to VCC IOMA X Min -10 -10 Typ Max 10 10 Unit A A

On-Chip Termination (OCT) Specifications Table 18 lists the Stratix IV series and parallel OCT calibration accuracy.

Table 18. On-Chip Termination With Calibration Specification for I/Os - Preliminary Calibration Accuracy Symbol 25- RS 3.0/2.5 50- RS 3.0/2.5 50- RT 2.5 25- RS 1.8 50- RS 1.8 50- RT 1.8 50- RS 1.5 50- RT 1.5 50- RS 1.2 50- RT 1.2 Description 25- series termination 50- series termination 50- parallel termination 25- series termination 50- series termination 50- parallel termination 50- series termination 50- parallel termination 50- series termination 50- series termination Conditions VC CIO = 3.0/2.5 V VC CIO = 3.0/2.5 V VCC IO = 2.5 V VCC IO = 1.8 V VCC IO = 1.8 V VCC IO = 1.8 V VCC IO = 1.5 V VCC IO = 1.5 V VCC IO = 1.2 V VCC IO = 1.2 V Commercial 5 5 10 5 5 10 8 10 8 10 Unit % % % % % % % % % %

The calibration accuracy for calibrated series and parallel OCTs are applicable at the moment of calibration. When PVT conditions change after calibration, the tolerance may change. Table 19 lists the Stratix IV OCT resistance tolerance to PVT changes.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

16

Table 19. I/O On-Chip Termination Resistance Tolerance - Preliminary Resistance Tolerance Symbol ROC T_UNCAL ROC T_CAL Description Internal series/parallel OCT with calibration Internal series/parallel OCT without calibration Commercial 5 30 Unit % %

OCT calibration is automatically performed at power-up for OCT-enabled I/Os. Table 110 lists OCT variation with temperature and voltage after power-up calibration. Use Equation 11 to determine the OCT variation when voltage and temperature vary after power-up calibration.

Equation 11. OCT Variation Without Re-Calibration (Note 1)

dR dR ROCT = RC AL 1 + ------ T + ------ V dT dV

Note to Equation 11:

(1) RCAL is calibrated on-chip termination at power up. T and V are variations in temperature and voltage with respect to temperature and VCCIO values, respectively, at power up.

Table 110. On-Chip Termination Variation after Power-Up Calibration - Preliminary Symbol dR/dV Description OCT variation with voltage without re-calibration VC CIO (V) 3.0 2.5 1.8 1.5 1.2 dR/dT OCT variation with temperature without re-calibration 3.0 2.5 1.8 1.5 1.2 Commercial Typical 0.029 0.036 0.033 0.033 0.033 0.294 0.301 0.355 0.344 0.348 Industrial Typical /C Unit /V

Pin Capacitance Table 111 shows the Stratix IV device family pin capacitance.

Table 111. Stratix IV Device Capacitance (Note 1) - Preliminary (Part 1 of 2) Symbol CIOTB CIOLR CC LKTB CC LKLR Description Input capacitance on top/bottom I/O pins Input capacitance on left/right I/O pins Input capacitance on top/bottom dedicated clock input pins Input capacitance on left/right dedicated clock input pins Typical 8 8 5 5 Unit pF pF pF pF

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

17

Table 111. Stratix IV Device Capacitance (Note 1) - Preliminary (Part 2 of 2) Symbol COUTF B Description Input capacitance on dual-purpose clock output/feedback pins Typical 8 Unit pF

Note to Table 111:

(1) Pending silicon characterization.

Hot Socketing Table 112 defines the hot socketing specification for Stratix IV devices.

Table 112. Stratix IV Hot Socketing Specifications - Preliminary Symbol IIIOP IN(DC) IIOPIN(A C) Description DC current per I/O pin AC current per I/O pin Maximum 300 A 8 mA for Trise > 10 ns

I/O Standard Specifications

Table 113 through Table 118 list input voltage (VIH and VIL), output voltage (VOH and VOL), and current drive characteristics (IOH and IOL) for various I/O standards supported by Stratix IV devices. These tables also show the Stratix IV device family I/O standard specifications. Refer to the Glossary on page 134 for an explanation of terms used in Table 113 through Table 118. VOL and VOH values are valid at the corresponding IOH and IOL, respectively.

Table 113. Single-Ended I/O Standards VCC IO (V) I/O Standard LVTTL LVCMOS 2.5 V Min 2.85 2.85 2.375 Typ 3 3 2.5 Max 3.15 3.15 2.625 Min -0.3 -0.3 -0.3 VIL (V) Max 0.8 0.8 0.7 Min 1.7 1.7 1.7 VIH (V) Max VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VOL (V) Max 0.4 0.2 0.2 0.4 0.7 1.8 V 1.5 V 1.2 V 3.0-V PCI 3.0-V PCI-X 1.71 1.425 1.14 2.85 2.85 1.8 1.5 1.2 3 3 1.89 1.575 1.26 3.15 3.15 -0.3 -0.3 -0.3 0.35 * VCC IO 0.35 * VCC IO 0.35 * VCC IO 0.3 * VCC IO 0.35 * VCC IO 0.65 * VCC IO 0.65 * VCC IO 0.65 * VCC IO 0.5 * VCC IO 0.5 * VCC IO VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 3.6 0.45 0.25 * VCC IO 0.25 * VCC IO 0.1 * VCC IO 0.1 * VCC IO VOH (V) Min 2.4 VC CIO - 0.2 2.1 2 1.7 VC CIO -0.45 0.75 * VC CIO 0.75 * VC CIO 0.9 * VCCIO 0.9 * VCCIO IO L (mA) 2 0.1 0.1 1 2 2 2 2 1.5 1.5 IO H (mA) -2 -0.1 -0.1 -1 -2 -2 -2 -2 -0.5 -0.5

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

18

Table 114. Single-Ended SSTL and HSTL I/O Reference Voltage Specifications VCC IO(V) I/O Standard SSTL-2 Class I, II SSTL-18 Class I, II SSTL-15 Class I, II HSTL-18 Class I, II HSTL-15 Class I, II HSTL-12 Class I, II Min 2.375 1.71 1.425 1.71 1.425 1.14 Typ 2.5 1.8 1.5 1.8 1.5 1.2 Max 2.625 1.89 1.575 1.89 1.575 1.26 Min 0.49 * VCCIO 0.49 * VCCIO 0.49 * VCCIO 0.85 0.68 0.48 * VCCIO VR EF(V) Typ 0.5 * VCC IO 0.5 * VCC IO 0.5 * VCC IO 0.9 0.75 0.5 * VCC IO Max 0.51 * VCC IO 0.51 * VCC IO 0.51 * VCC IO 0.95 0.9 0.52 * VCC IO Min VREF 0.04 VREF 0.04 VREF 0.04 VTT(V) Typ VREF VREF VREF VCCIO/2 VCCIO/2 VCCIO/2 Max VREF + 0.04 VREF + 0.04 VREF + 0.04

Table 115. Single-Ended SSTL and HSTL I/O Standards Signal Specifications VIL(D C)(V) I/O Standard SSTL-2 Class I SSTL-2 Class II SSTL-18 Class I SSTL-18 Class II SSTL-15 Class I SSTL-15 Class II HSTL-18 Class I HSTL-18 Class II HSTL-15 Class I HSTL-15 Class II HSTL-12 Class I HSTL-12 Class II Min -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 -0.15 -0.15 Max VREF 0.15 VREF 0.15 VREF 0.125 VREF 0.125 VREF -0.1 VREF -0.1 VREF -0.1 VREF -0.1 VREF -0.1 VREF -0.1 VREF 0.08 VREF 0.08 VIH (DC )(V) Min VREF + 0.15 VREF + 0.15 VREF + 0.125 VREF + 0.125 VREF + 0.1 VREF + 0.1 VREF + 0.1 VREF + 0.1 VREF + 0.1 VREF + 0.1 VREF + 0.08 VREF + 0.08 Max VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.3 VCC IO + 0.15 VCC IO + 0.15 VIL(A C)(V) Max VREF - 0.31 VREF - 0.31 VREF -0.25 VREF -0.25 VREF 0.175 VREF 0.175 VREF -0.2 VREF -0.2 VREF -0.2 VREF -0.2 VREF -0.15 VREF -0.15 VIH(A C)(V) Min VREF + 0.31 VREF + 0.31 VREF + 0.25 VREF + 0.25 VREF + 0.175 VREF + 0.175 VREF + 0.2 VREF + 0.2 VREF + 0.2 VREF + 0.2 VREF + 0.15 VREF + 0.15 VO L(V) Max VTT 0.57 VTT 0.76 VTT 0.475 0.28 0.2 * VCC IO 0.2 * VCC IO 0.4 0.4 0.4 0.4 0.25* VCC IO 0.25* VCC IO VO H(V) Min VTT + 0.57 VTT + 0.76 VTT + 0.475 VC CIO 0.28 0.8 * VCC IO 0.8 * VCC IO VC CIO -0.4 VC CIO -0.4 VC CIO -0.4 VC CIO -0.4 0.75* VCC IO 0.75* VCC IO Iol (mA) 8.1 16.2 6.7 13.4 8 16 8 16 8 16 8 16 I oh (mA) -8.1 -16.2 -6.7 -13.4 -8 -16 -8 -16 -8 -16 -8 -16

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Electrical Characteristics

19

Table 116. Differential SSTL I/O Standards VC CIO(V) I/O Standard SSTL-2 Class I, II SSTL-18 Class I, II SSTL-15 Class I, II Min 2.375 1.71 Typ 2.5 1.8 Max 2.625 1.89 VC SWING (DC)(V) Min 0.3 0.3 Max VCCIO + 0.6 VCC IO + 0.6 Min VCC IO/2 - 0.2 VCC IO/2 0.175 VX (A C)(V) Typ Max VCC IO /2 + 0.2 VCC IO /2 + 0.175 VSWIN G(AC )(V) Min 0.6 0.5 Max VC CIO + 0.6 VC CIO + 0.6 Min VCC IO/2 - 0.15 VCC IO/2 0.125 VO X(AC )(V) Typ Max VCC IO /2 + 0.15 VCC IO /2 + 0.125

1.425

1.5

1.575

0.2

VC CIO/2

0.4

VC CIO/2

Table 117. Differential HSTL I/O Standards VCC IO (V) I/O Standard HSTL-18 Class I HSTL-15 Class I, II HSTL-12 Class I, II Min 1.71 1.425 1.14 Typ 1.8 1.5 1.2 Max 1.89 1.575 1.26 VDIF(D C)(V) Min 0.2 0.2 0.2 Max Min 0.78 0.68 VX(AC )(V) Typ 0.5* VC CIO Max 1.12 0.9 Min 0.8 0.7 0.4* VCC IO VCM (DC)(V) Typ 0.5* VCC IO Max 1.12 0.9 0.6* VCC IO VD IF(A C)(V) Min 0.4 0.4 0.3 Max

Table 118. Differential I/O Standard Specifications (Part 1 of 2) (Note 1), (2) VCC IO (V) I/O Standard 2.5V LVDS (HIO) 2.5V LVDS (VIO) RSDS (HIO) RSDS (VIO) MiniLVDS (HIO) MiniLVDS (VIO) Min 2.37 5 Typ 2.5 Max VID (mV) Min Condition VC M = 1.25V Max 2.37 5 2.5 2.625 100 VC M = 1.25V 2.37 5 2.37 5 2.37 5 2.37 5 2.5 2.5 2.5 2.625 100 2.625 100 2.625 200 VC M = 1.25V VC M = 1.25V 600 Min 0.05 1.05 0.05 1.05 0.3 0.3 0.4 VICM (D C)(V) Conditio n Dm ax <= 700Mbps Dm ax > 700Mbps Dm ax <= 700Mbps Dm ax > 700Mbps Max 1.8 1.55 1.8 1.55 1.4 1.4 1.32 5 1.32 5 VO D(V) (3) Min 0.24 7 0.24 7 0.1 0.1 0.25 Typ 0.2 0.2 Ma x 0.6 0.6 0.6 0.6 0.6 VO CM (V) (3) Min 1.12 5 1 0.5 0.5 0.5 Typ 1.2 5 1.2 5 1.2 1.2 1.2 Max 1.37 5 1.5 1.5 1.4 1.5 1.4

2.625 100

2.5

2.625 200

600

0.4

0.25

0.6

0.5

1.2

1.5

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

110

Table 118. Differential I/O Standard Specifications (Part 2 of 2) (Note 1), (2) VCC IO (V) I/O Standard LVPECL (VIO) (4) Min 2.37 5

Notes to Table 118:

(1) (2) (3) (4) (5) VIO (vertical I/O) is top and bottom I/Os; HIO (horizontal I/O) is left and right I/Os. 1.4V/1.5V PCML transceiver I/O standard specifications are described in the section Transceiver Performance Specifications on page 110. RL range: 90 <= RL <= 110 . LVPECL specifications apply only to CLK input pins on column I/Os. For DMAX > 700 Mbps, the minimum input voltage is 0.85 V; the maximum input voltage is 1.75 V. For FMA X <=700Mbps, the minimum input voltage is 0.45 V; the maximum input voltage is 1.95 V.

VID (mV) Max Min Condition Max Min 0.6 0.6

VICM (D C)(V) Conditio n Dm ax <= 700Mbps Dm ax > 700Mbps Max 1.8 (5) 1.6 (5)

VO D(V) (3) Min Typ Ma x

VO CM (V) (3) Min Typ Max

Typ 2.5

2.625 300

Power Consumption

Altera offers two ways to estimate power consumption for a design: the Excel-based Early Power Estimator and the Quartus II PowerPlay Power Analyzer feature. The interactive Excel-based Early Power Estimator is typically used prior to designing the FPGA in order to get a magnitude estimate of the device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, combined with detailed circuit models, can yield very accurate power estimates. f For more information about power estimation tools, refer to the PowerPlay Early Power Estimator User Guide for Stratix III and Stratix IV FPGAs and the PowerPlay Power Analysis chapter in the Quartus II Handbook.

Switching Characteristics

This section provides performance characteristics of Stratix IV core and periphery blocks for commercial grade devices. These characteristics can be designated as Preliminary and Final. Preliminary characteristics are created using simulation results, process data, and other known parameters. Final numbers are based on actual silicon characterization and testing. These numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions. The upper-right hand corner of a table shows the designation as Preliminary or Final.

Transceiver Performance Specifications

This sections describes transceiver performance specifications. Table 119 lists Stratix IV GX transceiver specifications.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

111

Table 119. Stratix IV GX Transceiver Specification (Part 1 of 4) -3 Commercial/Industrial and -2x Commercial Speed Grade (1) Min Typ Max

-2 Speed Commercial Speed Grade Symbol/ Description Reference Clock Input frequency from REFCLK input pins Phase frequency detector (CMU PLL and receiver CDR) Absolute VMAX for a REFCLK pin Operational VMAX for a REFCLK pin Absolute VMIN for a REFCLK pin Rise/fall time Duty cycle Peak-to-peak differential input voltage Spread-spectrum modulating clock frequency Spread-spectrum downspread On-chip termination resistors VICM (AC coupled) VICM (DC coupled) 50 50 637.5 425 Conditions Min Typ Max

-4 Speed Commercial Speed Grade Min Typ Max Unit

50 50

637.5 325

50 50

622.08 MHz 325 MHz

-0.3 45 200

1.6 1.5 0.2 55 1600

-0.3 45 200

1.6 1.5 0.2 55 1600

-0.3 45 200

1.6 1.5 0.2 55 1600

V V V UI % mV

PCI Express

30

33

30

33

30

33

kHz

PCI Express HCSL I/O standard for PCI Express reference clock

250

0 to -0.5% 100 1100

550

250

0 to -0.5% 100 1100

550

250

0 to -0.5% 100 1100

550

mV mV

RREF Transceiver Clocks Calibration block clock frequency fixedclk clock frequency reconfig_clk clock frequency

2000 1%

2000 1%

2000 1%

PCI Express Receiver Detect Dynamic reconfiguration clock frequency

10 2.5/ 37.5 (2)

125

125 50

10 2.5/ 37.5 (2)

125

125 50

10 2.5/ 37.5 (2)

125

125 50

MHz MHz

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

112

Table 119. Stratix IV GX Transceiver Specification (Part 2 of 4) -3 Commercial/Industrial and -2x Commercial Speed Grade (1) Min Typ 1 Max

-2 Speed Commercial Speed Grade Symbol/ Description Transceiver block minimum power-down pulse width Receiver Data rate Absolute VM AX for a receiver pin (3) Operational VM AX for a receiver pin Absolute VM IN for a receiver pin Maximum peak-topeak differential input voltage VID (diff p-p) Minimum peak-topeak differential input voltage VID (diff p-p) VICM VICM = 0.82 V setting VICM =1 .1 V setting (4) Data Rate = 600 Mbps to 5 Gbps. Data Rate > 5Gbps. VICM = 0.82 V setting VICM =1 .1 V setting (4) Differential on-chip termination resistors 85 setting 100 setting 120 setting 150- setting Return loss differential mode PCI Express XAUI (OIF) CEI Return loss common mode PCI Express XAUI (OIF) CEI 600 -0.4 100 165 820 1100 85 100 120 150 8500 1.6 1.5 2.7 1.6 Conditions Min Typ 1 Max

-4 Speed Commercial Speed Grade Min Typ 1 Max Unit s

600 -0.4 100 165

820 1100 85 100 120 150

6500 1.6 1.5 2.7 1.6

600 -0.4 165

820 1100 85 100 120 150

5000 1.6 1.5 2.7 1.6

Mbp s V V V V V mV mV mV mV

50 MHz to 1.25 GHz: -10dB 100 MHz to 2.5 GHz: -10dB 100 MHz to 4.875 GHz: -8dB 4.875 GHz to 10 GHz: 16.6 dB/decade slope 50 MHz to 1.25 GHz: -6dB 100 MHz to 2.5 GHz: -6dB 100 MHz to 4.875 GHz: -6dB 4.875 GHz to 10 GHz: 16.6 dB/decade slope

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

113

Table 119. Stratix IV GX Transceiver Specification (Part 3 of 4) -3 Commercial/Industrial and -2x Commercial Speed Grade (1) Min Typ Max

-2 Speed Commercial Speed Grade Symbol/ Description Programmable PPM detector (5) Run length Programmable equalization Signal detect/loss threshold CDR LTR time (6) CDR minimum T1b (7) LTD lock time (8) Data lock time from rx_freqlocked (9) Programmable DC gain Conditions PCI Express (PIPE) Mode 65 15 0 80 100 4000 4000 16 175 75 Min Typ Max

-4 Speed Commercial Speed Grade Min Typ Max Unit ppm 65 15 0 80 100 16 175 75 4000 4000 UI dB mV s s ns ns

62.5, 100, 125, 200, 250, 300, 500, 1000 65 15 0 80 100 16 175 75 4000 4000

DC Gain Setting =0 DC Gain Setting =1 DC Gain Setting =2 DC Gain Setting =3 DC Gain Setting =4

0 3 6 9 12

0 3 6 9 12

0 3 6 9 12

dB dB dB dB dB

Transmitter Data rate VOC M Differential on-chip termination resistors 0.65 V setting 600 650 85 100 120 150 8500 600 650 85 100 120 150 6500 600 650 85 100 120 150 5000 Mbp s mV

85 setting 100 setting 120 setting 150- setting

Return loss differential mode

PCI Express XAUI (OIF) CEI

50 MHz to 1.25 GHz: -10dB 312 MHz to 625 MHz: -10dB 625 MHz to 3.125 GHz: -10dB/decade slope 100 MHz to 4.875 GHz: -8dB 4.875 GHz to 10 GHz: 16.6 dB/decade slope

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

114

Table 119. Stratix IV GX Transceiver Specification (Part 4 of 4) -3 Commercial/Industrial and -2x Commercial Speed Grade (1) Min Typ Max

-2 Speed Commercial Speed Grade Symbol/ Description Return loss common mode Conditions PCI Express (OIF) CEI 50 50 200 200 15 120 300 Min Typ Max

-4 Speed Commercial Speed Grade Min Typ Max Unit

50 MHz to 1.25 GHz: -6dB 100 MHz to 4.875 GHz: -6dB 4.875 GHz to 10 GHz: 16.6 dB/decade slope 50 50 200 200 15 120 300 50 50 200 200 15 120 300 ps ps ps ps ps

Rise time Fall time Intra differential pair skew Intra-transceiver block skew Inter-transceiver block skew CMU PLL0 and CMU PLL1 CMU PLL lock time from CMUPLL_reset deassertion PLD-Transceiver Interface Interface speed Digital reset pulse width

Notes to Table 119:

100

100

100

25

250

25

250

25

250

MHz

Minimum is 2 parallel clock cycles

(1) The -2x speed grade is the fastest speed grade offered in the following Stratix IV GX devices: EP4SGX70DF29, EP4SGX110DF29, EP4SGX110FF35, EP4SGX230DF29, EP4SGX110FF35, EP4SGX230DF29, EP4SGX230FF35, EP4SGX290FF35, EP4SGX290FH29, EP4SGX360FF35, and EPSGX360FH29. (2) The minimum reconfig_clk frequency is 2.5 MHz if the transceiver channel is configured in transmitter only mode. The minimum reconfig_clk frequency is 37.5MHz if the transceiver channel is configured in receiver only or receiver and transmitter mode. For more details, refer to the Stratix IV Dynamic Reconfiguration chapter in volume 1 of the Stratix IV Device Handbook. (3) The device cannot tolerate prolonged operation at this absolute maximum. (4) The 1.1-V RX VIC M setting must be used if the input serial data standard is LVDS and the link is DC coupled. (5) The rate matcher supports only up to +/-300 ppm. (6) Time taken to rx_pll_locked goes high from rx_analogreset deassertion. Refer to Figure 11. (7) Time for which the CDR must be kept in lock-to-reference mode after rx_pll_locked goes high and before rx_locktodata is asserted in manual mode. Refer to Figure 11. (8) Time taken to recover valid data after the rx_locktodata signal is asserted in manual mode. Refer to Figure 11. (9) Time taken to recover valid data after the rx_freqlocked signal goes high in automatic mode. Refer to Figure 12.

Figure 11 shows the lock time parameters in manual mode. Figure 12 shows the lock time parameters in automatic mode. 1 LTD = Lock-To-Data LTR = Lock-To-Reference

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

115

Figure 11. Lock Time Parameters for Manual Mode

r x_analogreset

CDR status

LTR

LTD

r x_pll_locked

r x_locktodata

Invalid Data r x_dataout

Valid data

CDR LTR Time

LTD lock time

CDR Minimum T1b

Figure 12. Lock Time Parameters for Automatic Mode

CDR status

LTR

LTD

r x_freqlocked

r x_dataout

Invalid

data

Valid

data

Data lock time from rx_freqlocked

Table 120 through Table 123 show the typical VOD for various differential termination settings.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

116

Table 120. Typical VOD Setting, TX Term = 85 VO D Setting (mV) Symbol VOD Typical (mV) 0 170 1 340 2 510 3 595 4 680 5 765 6 850 7 1020

Table 121. Typical VOD Setting, TX Term = 100 W VO D Setting (mV) Symbol VOD Typical (mV) 0 200 1 400 2 600 3 700 4 800 5 900 6 1000 7 1200

Table 122. Typical VOD Setting, TX Term = 120 VO D Setting (mV) Symbol VOD Typical (mV) 0 240 1 480 2 720 3 840 4 960 5 1080 6 1200

Table 123. Typical VOD Setting, TX Term = 150 VOD Setting (mV) Symbol VOD Typical (mV) 0 300 1 600 2 900 3 1050 4 1200 5 1350

Table 124 shows the Stratix IV GX transceiver block AC specifications.

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 1 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Conditions Min Typ Max -3 Speed Commercial and Industrial Speed Grade Min Typ Max -4 Speed Commercial Speed Grade Min Typ Max Unit

SONET/SDH Transmit Jitter Generation (3) Peak-to-peak jitter at 622.08 Mbps RMS jitter at 622.08 Mbps Peak-to-peak jitter at 2488.32 Mbps RMS jitter at 2488.32 Mbps Pattern = PRBS23 Pattern = PRBS23 Pattern = PRBS23 Pattern = PRBS23 0.1 0.01 0.1 0.01 0.1 0.01 0.1 0.01 0.1 0.01 0.1 0.01 UI UI UI UI

SONET/SDH Receiver Jitter Tolerance (3)

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

117

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 2 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Jitter tolerance at 622.08 Mbps Conditions Jitter frequency = 0.03 KHz Pattern = PRBS23 Jitter frequency = 25 KHZ Pattern = PRBS23 Jitter frequency = 250 KHz Pattern = PRBS23 Jitter tolerance at 2488.32 MBps Jitter frequency = 0.06 KHz Pattern = PRBS23 Jitter frequency = 100 KHZ Pattern = PRBS23 Jitter frequency = 1 MHz Pattern = PRBS23 Jitter frequency = 10 MHz Pattern = PRBS23 Fibre Channel Transmit Jitter Generation (4), (12) Total jitter FC-1 Deterministic jitter FC-1 Total jitter FC-2 Deterministic jitter FC-2 Total jitter FC-4 Deterministic jitter FC-4 Pattern = CRPAT Pattern = CRPAT Pattern = CRPAT Pattern = CRPAT Pattern = CRPAT Pattern = CRPAT 0.23 0.11 0.33 0.2 0.52 0.33 0.23 0.11 0.33 0.2 0.52 0.33 0.23 0.11 0.33 0.2 0.52 0.33 UI UI UI UI UI UI > 0.15 > 0.15 > 0.15 UI > 0.15 > 0.15 > 0.15 UI > 1.5 > 1.5 > 1.5 UI > 15 > 15 > 15 UI > 0.15 > 0.15 > 0.15 UI > 1.5 > 1.5 > 1.5 UI Min Typ > 15 Max -3 Speed Commercial and Industrial Speed Grade Min Typ > 15 Max -4 Speed Commercial Speed Grade Min Typ > 15 Max Unit UI

Fibre Channel Receiver Jitter Tolerance (4), (13) Deterministic jitter FC-1 Random jitter FC-1 Sinusoidal jitter FC-1 Deterministic jitter FC-2 Random jitter FC-2 Sinusoidal jitter FC-2 Pattern = CJTPAT Pattern = CJTPAT Fc/25000 Fc/1667 Pattern = CJTPAT Pattern = CJTPAT Fc/25000 Fc/1667 > 0.37 > 0.31 > 1.5 > 0.1 > 0.33 > 0.29 > 1.5 > 0.1 > 0.37 > 0.31 > 1.5 > 0.1 > 0.33 > 0.29 > 1.5 > 0.1 > 0.37 > 0.31 > 1.5 > 0.1 > 0.33 > 0.29 > 1.5 > 0.1 UI UI UI UI UI UI UI UI

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

118

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 3 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Deterministic jitter FC-4 Random jitter FC-4 Sinusoidal jitter FC-4 Conditions Pattern = CJTPAT Pattern = CJTPAT Fc/25000 Fc/1667 XAUI Transmit Jitter Generation (5) Total jitter at 3.125 Gbps Deterministic jitter at 3.125 Gbps Pattern = CJPAT Pattern = CJPAT 0.3 0.17 0.3 0.17 0.3 0.17 UI UI Min Typ > 0.33 > 0.29 > 1.5 > 0.1 Max -3 Speed Commercial and Industrial Speed Grade Min Typ > 0.33 > 0.29 > 1.5 > 0.1 Max -4 Speed Commercial Speed Grade Min Typ > 0.33 > 0.29 > 1.5 > 0.1 Max Unit UI UI UI UI

XAUI Receiver Jitter Tolerance (5) Total jitter Deterministic jitter Peak-to-peak jitter Peak-to-peak jitter Peak-to-peak jitter Jitter frequency = 22.1 KHz Jitter frequency = 1.875 MHz Jitter frequency = 20 MHz > 0.65 > 0.37 > 8.5 > 0.1 > 0.1 > 0.65 > 0.37 > 8.5 > 0.1 > 0.1 > 0.65 > 0.37 > 8.5 > 0.1 > 0.1 UI UI UI UI UI

PCI Express Transmit Jitter Generation (6) Total jitter at 2.5 Gbps (Gen1) Total jitter at 5 Gbps (Gen2) Compliance pattern Compliance pattern 0.25 0.25 0.25 UI UI

PCI Express Receiver Jitter Tolerance (6) Total jitter at 2.5 Gbps (Gen1) Total jitter at 2.5 Gbps (Gen2) Compliance pattern Compliance pattern > 0.6 > 0.6 > 0.6 UI UI

Serial RapidIO Transmit Jitter Generation (7) Deterministic jitter (peak-to-peak) Total jitter (peak-to-peak) Data Rate = 1.25, 2.5, 3.125 Gbps Pattern = CJPAT Data Rate = 1.25, 2.5, 3.125 Gbps Pattern = CJPAT Serial RapidIO Receiver Jitter Tolerance (7) Deterministic jitter tolerance (peak-to-peak) Data Rate = 1.25, 2.5, 3.125 Gbps Pattern = CJPAT > 0.37 > 0.37 > 0.37 UI 0.35 0.35 0.35 UI 0.17 0.17 0.17 UI

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

119

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 4 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Combined deterministic and random jitter tolerance (peak-to-peak) Sinusoidal jitter tolerance (peak-to-peak) Conditions Data Rate = 1.25, 2.5, 3.125 Gbps Pattern = CJPAT Jitter Frequency = 22.1 KHz Data Rate = 1.25, 2.5, 3.125 Gbps Pattern = CJPAT Jitter Frequency = 1.875 MHz Data Rate = 1.25, 2.5, 3.125 Gbps Pattern = CJPAT Jitter Frequency = 20 MHz Data Rate = 1.25, 2.5, 3.125 Gbps Pattern = CJPAT GIGE Transmit Jitter Generation (8) Deterministic jitter (peak-to-peak) Total jitter (peak-to-peak) Pattern = CRPAT 0.279 0.279 0.279 UI Pattern = CRPAT 0.14 0.14 0.14 UI > 0.1 > 0.1 > 0.1 UI > 0.1 > 0.1 > 0.1 UI > 8.5 > 8.5 > 8.5 UI Min Typ > 0.55 Max -3 Speed Commercial and Industrial Speed Grade Min Typ > 0.55 Max -4 Speed Commercial Speed Grade Min Typ > 0.55 Max Unit UI

GIGE Receiver Jitter Tolerance (8) Deterministic jitter tolerance (peak-to-peak) Combined deterministic and random jitter tolerance (peak-to-peak) Pattern = CJPAT Pattern = CJPAT > 0.4 > 0.66 > 0.4 > 0.66 > 0.4 > 0.66 UI UI

HiGig Transmit Jitter Generation (9) Deterministic jitter (peak-to-peak) Total jitter (peak-to-peak) Data Rate = 3.75 Gbps Pattern = CJPAT Data Rate = 3.75 Gbps Pattern = CJPAT HiGig Receiver Jitter Tolerance (9) Deterministic jitter tolerance (peak-to-peak) Combined deterministic and random jitter tolerance (peak-to-peak) Data Rate = 3.75 Gbps Pattern = CJPAT Data Rate = 3.75 Gbps Pattern = CJPAT > 0.65 UI > 0.37 UI 0.35 UI 0.17 UI

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

120

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 5 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Sinusoidal jitter tolerance (peak-to-peak) Conditions Jitter Frequency = 22.1 KHz Data Rate = 3.75 Gbps Pattern = CJPAT Jitter Frequency = 1.875MHz Data Rate = 3.75 Gbps Pattern = CJPAT Jitter Frequency = 20 MHz Data Rate = 3.75 Gbps Pattern = CJPAT (OIF) CEI Transmitter Jitter Generation (10) Total jitter (peak-to-peak) Data Rate = 6.375 Gbps Pattern = PRBS15 BER = 10-12 (OIF) CEI Receiver Jitter Tolerance (10) Deterministic jitter tolerance (peak-to-peak) Data Rate = 6.375 Gbps Pattern = PRBS31 BER = 10-12 Combined deterministic and random jitter tolerance (peak-to-peak) Data Rate = 6.375 Gbps Pattern=PRBS31 BER = 10- 12 > 0.988 N/A N/A UI > 0.675 N/A N/A UI 0.3 N/A N/A UI > 0.1 UI > 0.1 UI Min Typ > 8.5 Max -3 Speed Commercial and Industrial Speed Grade Min Typ Max -4 Speed Commercial Speed Grade Min Typ Max Unit UI

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

121

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 6 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Sinusoidal jitter tolerance (peak-to-peak) Conditions Jitter Frequency = 38.2 KHz Data Rate = 6.375 Gbps Pattern = PRBS31 BER = 10-12 Jitter Frequency = 3.82 MHz Data Rate = 6.375 Gbps Pattern = PRBS31 BER = 10-12 Jitter Frequency = 20 MHz Data Rate= 6.375 Gbps Pattern = PRBS31 BER = 10-12 SDI Transmitter Jitter Generation (11) Alignment jitter (peak-to-peak) Data Rate = 1.485 Gbps (HD) Pattern = Color Bar Low-Frequency RollOff = 100 KHz Data Rate = 2.97 Gbps (3G) Pattern = Color Bar Low-Frequency Roll-Off = 100 KHz SDI Receiver Jitter Tolerance (11) 0.2 0.2 0.2 UI > 0.05 N/A N/A UI > 0.05 N/A N/A UI Min Typ >5 Max -3 Speed Commercial and Industrial Speed Grade Min N/A Typ Max -4 Speed Commercial Speed Grade Min N/A Typ Max Unit UI

0.3

0.3

0.3

UI

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

122

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 7 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Sinusoidal jitter tolerance (peak-to-peak) Conditions Jitter Frequency = 15 KHz Data Rate = 2.97 Gbps (3G) Pattern = Single Line Scramble Color Bar Jitter Frequency = 100 KHz Data Rate = 2.97 Gbps (3G) Pattern = Single Line Scramble Color Bar Jitter Frequency = 148.5 MHz Data Rate = 2.97 Gbps (3G) Pattern = Single Line Scramble Color Bar > 0.3 > 0.3 > 0.3 UI > 0.3 > 0.3 > 0.3 UI Min Typ >2 Max -3 Speed Commercial and Industrial Speed Grade Min Typ >2 Max -4 Speed Commercial Speed Grade Min Typ >2 Max Unit UI

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

123

Table 124. Stratix IV GX Transceiver Block AC Specification (Note 1), (2) (Part 8 of 8) -2 Speed Commercial Speed Grade Symbol/ Description Sinusoidal jitter tolerance (peak-to-peak) Conditions Jitter Frequency = 20 KHz Data Rate = 1.485 Gbps (HD) Pattern = 75% Color Bar Jitter Frequency = 100 KHz Data Rate = 1.485 Gbps (HD) Pattern = 75% Color Bar Jitter Frequency = 148.5 MHz Data Rate = 1.485 Gbps (HD) Pattern =75% Color Bar

Notes to Table 124:

(1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) Dedicated refclk pins were used to drive the input reference clocks. Jitter numbers specified are valid for the stated conditions only. The jitter numbers for SONET/SDH are compliant to the GR-253-CORE Issue 3 Specification. The jitter numbers for Fibre Channel are compliant to the FC-PI-4 Specification revision 6.10. The jitter numbers for XAUI are compliant to the IEEE802.3ae-2002 Specification. The jitter numbers for PCI Express are compliant to the PCIe Base Specification 2.0. The jitter numbers for Serial RapidIO are compliant to the RapidIO Specification 1.3. The jitter numbers for GIGE are compliant to the IEEE802.3-2002 Specification. The jitter numbers for HiGig are compliant to the IEEE802.3ae-2002 Specification. The jitter numbers for (OIF) CEI are compliant to the OIF-CEI-02.0 Specification. The HD-SDI and 3G-SDI jitter numbers are compliant to the SMPTE292M and SMPTE424M Specifications. The fibre channel transmitter jitter generation numbers are compliant to the specification at T interoperability point. The fibre channel receiver jitter tolerance numbers are compliant to the specification at R interoperability point.

-3 Speed Commercial and Industrial Speed Grade Min Typ >1 Max

-4 Speed Commercial Speed Grade Min Typ >1 Max Unit UI

Min

Typ >1

Max

> 0.2

> 0.2

> 0.2

UI

> 0.2

> 0.2

> 0.2

UI

Core Performance Specifications

This sections describes the clock tree, PLL, DSP, TriMatrix, and configuration and JTAG specifications.

Clock Tree Specifications

Table 125 lists the clock tree specifications for Stratix IV devices.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

124

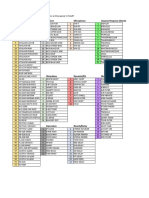

Table 125. Stratix IV Clock Tree Performance - Preliminary Performance Device EP4SE110 EP4SE230 EP4SE290 EP4SE360 EP4SE530 EP4SE680 EP4SGX70 EP4SGX110 EP4SGX230 EP4SGX290 EP4SGX360 EP4SGX530 -2/-2x Speed Grade 600 600 600 600 600 600 600 600 600 600 600 600 -3 Speed Grade 500 500 500 500 500 500 500 500 500 500 500 500 -4 Speed Grade 450 450 450 450 450 450 450 450 450 450 450 450 Unit MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz

PLL Specifications

Table 126 describes the Stratix IV PLL specifications when operating in both the commercial junction temperature range (0 to 85C) and the industrial junction temperature range (-40 to 100C).

Table 126. Stratix IV PLL Specifications - Preliminary (Part 1 of 2) Symbol fIN fINPF D fVC O ( 2) fINDUTY fEINDUTY tINCC J fOUT fOUT_EXT tOUTDUTY tOUTPJ _DC tOUTPJ _IO tFC OMP tCONF IGPLL tCONF IGPHAS E fSC ANC LK tLOCK Input clock frequency Input frequency to the PFD PLL VCO operating Range Input clock duty cycle External feedback clock input duty cycle Input clock cycle to cycle jitter Output frequency for internal global or regional clock Output frequency for external clock output Duty cycle for external clock output (when set to 50%) Dedicated clock output period jitter Regular I/O clock output period jitter External feedback clock compensation time Time required to reconfigure PLL scan chains Time required to reconfigure phase shift scanclk frequency Time required to lock from end of device configuration Description Min 5 5 600 40 40 45 1 Typ 50 (4) Max 720 (1) 325 1300 60 60 (4) 717 (3) 717 (3) 55 (4) (4) 10 1 100 (4) Unit MHz MHz MHz % % ps MHz MHz % ps ps ns SCANCLK cycles SCANCLK cycles MHz ms

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

125

Table 126. Stratix IV PLL Specifications - Preliminary (Part 2 of 2) Symbol tDLOCK fCL B W Description Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) PLL closed-loop low bandwidth range PLL closed-loop medium bandwidth range PLL closed-loop high bandwidth range tPLL_P SERR tARES ET

(1) (2) (3) (4)

Min 10

Typ (4) (4) (4) (4)

Max (4)

Unit ms MHz MHz MHz ps ns

Accuracy of PLL phase shift Minimum pulse width on areset signal

Notes to Table 126:

FIN is limited by I/O FMA X. The VCO frequency reported by Quartus II software is after the post scale divider (k) and may be outside the VCO min and max range. This specification is limited by the lower of the two: I/O FMA X or FOUT of the PLL. Pending silicon characterization.

DSP Block Specifications

Table 127 describes the Stratix IV DSP block performance specifications.

Table 127. Stratix IV DSP Block Performance Specifications (Note 1) - Preliminary Resources Used Number of Multipliers 1 1 1 1 4 4 2 2 1 1 -2/-2x Speed Grade 490 490 550 440 490 490 490 390 440 440 Performance -3 Speed Grade 405 405 455 365 405 405 405 320 365 365 -4 Speed Grade 375 375 420 335 375 375 375 300 335 335

Mode 99-bit multiplier 1212-bit multiplier 1818-bit multiplier 3636-bit multiplier 1818-bit multiply accumulator 1818-bit multiply adder 1818-bit multiply adder-signed full precision 1818-bit multiply adder with loopback (2) 36-bit shift (32 bit data) Double mode

Notes to Table 127:

Unit MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz

(1) Maximum is for fully pipelined block with Round and Saturation disabled. (2) Maximum is for non-pipelined block with loopback input registers disabled and Round and Saturation disabled.

TriMatrix Memory Block Specifications

Table 128 describes the Stratix IV TriMatrix memory block specifications.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

126

Table 128. Stratix IV TriMatrix Memory Block Performance Specifications Preliminary Resources Used TriMatrix Memory 1 1 1 1 1 1 1 1 1 1 -2 /-2x Speed Grade 600 600 600 600 600 600 600 600 333 600 Performance -3 Speed Grade 500 500 500 500 500 500 500 500 275 500 -4 Speed Grade 450 450 450 450 450 450 450 450 250 450

Memory MLAB

Mode Single port 6410 Simple dual-port 3220 single clock Simple dual-port 6410 single clock

ALUTs 0 0 0 0 0 0 0 0 0 0

Unit MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz

M9K Block

Single-port 25636 Simple dual-port 25636 single CLK True dual port 51218 single CLK Single-port 2K72 Simple dual-port 2K72 dual CLK Simple dual-port 2K64 dual CLK (with ECC) True dual-port 4K36 dual CLK

M144K

Configuration and JTAG Specifications

Table 129 lists the Stratix IV configuration mode specifications.

Table 129. Stratix IV Configuration Mode Specifications - Preliminary Programming Mode Passive serial Fast passive parallel Fast active serial Remote update only in fast AS mode DCLK Fmax 125 125 40 10 Unit MHz MHz MHz MHz

Table 130 shows the JTAG timing parameters and values for Stratix IV devices.

Table 130. Stratix IV JTAG Timing Parameters and Values - Preliminary Symbol tJC P tJC H tJC L tJP SU (TDI) tJP SU (TMS ) tJP H tJP CO tJP ZX tJP XZ Description TCK clock period TCK clock high time TCK clock low time TDI JTAG port setup time TMS JTAG port setup time JTAG port hold time JTAG port clock to output JTAG port high impedance to valid output JTAG port valid output to high impedance Min 30 14 14 1 3 5 Max 11 (1) 14 (1) 14 (1) Unit ns ns ns ns ns ns ns ns ns

Note to Table 130:

(1) A 1 ns adder is required for each VCC IO voltage step down from 3.3 V. For example, tJPC O = 12 ns if V C CIO of the TDO I/O bank = 2.5 V, or 13 ns if it equals 1.8 V.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

127

Temperature Sensing Diode Specifications

Table 131 lists the specifications for the Stratix IV temperature sensing diode.

Table 131. Temperature Sensing Diode Specifications - Preliminary Symbol fTSD_INCLK tDUTY_TS D_INC LK Description TSD Input Clock Frequency (without CLK divider) TSD Input Clock Frequency (with CLK divider) Duty Cycle of TSD Input Clock Min 0.25 38 45 Max 1.01 42 55 Unit MHz MHz %

Periphery Performance

This section describes periphery performance including high-speed I/O, external memory interface, and OCT calibration block specifications.

High-Speed I/O Specification

Table 132 shows the high-speed I/O timing for Stratix IV devices.

Table 132. High-Speed I/O Specifications for Fastest Speed Grade - Preliminary (Note 1), (2), (3), (4) (Part 1 of 2) -2/-2x Speed Grade Symbol fIN (input reference clock frequency) = fHS DR / W fHSC LK (source synchronous output clock frequency) fHSDR (data rate) Conditions Clock boost factor, W = 1 to 40 Serdes factor, J = 3 to 10 Serdes factor, J = 2, Uses DDR Registers Serdes factor, J = 1, Uses SDR Register fHSDRDPA (DPA data rate) Transmitter channel-to-channel skew (TCCS) Receiver sampling window (SW) tOUTJITTER_DC tOUTJITTER_IO Output t RIS E Output t FA LL tDUTY DPA run length Serdes factor, J = 3 to 10 All differential standards All differential standards All differential I/O standards All differential I/O standards Tx output clock duty cycle Min 5 5 (5) 150 (6) (6) 150 45 Typ 50 Max 717 717 1600 1250 717 (7) 1600 (5) (5) (5) (5) (5) (5) 55 (5) Unit MHz MHz Mbps Mbps Mbps Mbps ps ps ps ps ps ps % UI

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

128

Table 132. High-Speed I/O Specifications for Fastest Speed Grade - Preliminary (Note 1), (2), (3), (4) (Part 2 of 2) -2/-2x Speed Grade Symbol DPA jitter tolerance

Notes to Table 132:

(1) When J = 4 to 10, the SERDES block is used. (2) When J = 1 or 2, the SERDES block is bypassed. (3) The input clock frequency and the W factor must satisfy the following Left/Right PLL output specification: 150 <= input clock frequency W <= 1600 MHz. (4) Specifications for -3 and -4 speed grades will be available after silicon characterization. (5) Pending silicon characterization. (6) The minimum specification is dependent on the clock source (for example, PLL or clock pin) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register does not have a minimum toggle rate. (7) Same as device clock tree F M AX.

Conditions Data channel peak-to-peak jitter tolerance

Min (5)

Typ

Max

Unit UI

Table 133 shows the DPA lock time specifications for Stratix IV devices.

Table 133. DPA Lock Time Specifications - Preliminary Standard SPI-4 Parallel Rapid I/O Miscellaneous

Note to Table 133:

(1) Pending silicon characterization.

Training Pattern 00000000001111111111 00001111 10010000 10101010 01010101

Transition Density 10% 25% 50% 100%

Min (1) (1) (1) (1) (1)

Unit Number of repetitions Number of repetitions Number of repetitions Number of repetitions Number of repetitions

External Memory Interface Specifications

Table 134 through Table 143 list the external memory interface specifications for the Stratix IV device family. Use these tables for memory interface timing analysis.

Table 134. Stratix IV Maximum Clock Rate Support for External Memory Interfaces with Half-Rate Controller (Note 1), (2) (Part 1 of 2) Stratix IV GX Devices with 1152-Pin (with 24 Transceivers), 1517-Pin, and 1932-Pin Packages 2 Speed Grade (MHz) Column I/O Banks 533 400 200 Row I/O Banks (3) 333 333 200 3 Speed Grade (MHz) Column I/O Banks 400 333 200 Row I/O Banks (3) 333 333 200 4 Speed Grade (MHz) Column Row I/O Banks I/O (3) Banks 333 333 200 333 333 200 Stratix IV GX Devices with 780-Pin and 1152-Pin (with 16 Transceivers) Packages -2x Speed Grade (MHz) Column I/O Banks 333 333 200 Row I/O Banks (3) 333 333 200 -3 Speed Grade (MHz) Column I/O Banks 333 333 200 Row I/O Banks (3) 333 333 200 -4 Speed Grade (MHz) Column I/O Banks 333 333 200 Row I/O Banks (3) 333 333 200

Memory Standards DDR3 SDRAM (4) DDR2 SDRAM (4) DDR SDRAM (4)

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

129

Table 134. Stratix IV Maximum Clock Rate Support for External Memory Interfaces with Half-Rate Controller (Note 1), (2) (Part 2 of 2) Stratix IV GX Devices with 1152-Pin (with 24 Transceivers), 1517-Pin, and 1932-Pin Packages 2 Speed Grade (MHz) Column I/O Banks 400 Row I/O Banks (3) 300 3 Speed Grade (MHz) Column I/O Banks 350 Row I/O Banks (3) 300 4 Speed Grade (MHz) Column Row I/O Banks I/O (3) Banks 300 300 Stratix IV GX Devices with 780-Pin and 1152-Pin (with 16 Transceivers) Packages -2x Speed Grade (MHz) Column I/O Banks 300 Row I/O Banks (3) 300 -3 Speed Grade (MHz) Column I/O Banks 300 Row I/O Banks (3) 300 -4 Speed Grade (MHz) Column I/O Banks 300 Row I/O Banks (3) 300

Memory Standards QDRII+SRAM (2.5 clock cycle latency only) (5), (6) QDRII SRAM (1.5-V and 1.8-V HSTL) (6) RLDRAM II (1.5-V and 1.8-V HSTL)

Notes to Table 134:

350

300

300

300

300

300

300

300

300

300

300

300

400

333

333

333

333

333

333

333

333

333

333

333

(1) Numbers are preliminary pending characterization. The supported operating frequencies listed here are memory interface maximums for the FPGA device family. Your designs actual achievable performance is based on design and system-specific factors, as well as static timing analysis of the completed design. (2) Column I/Os refer to top and bottom I/Os. Row I/Os refer to left and right I/Os. (3) The row I/O banks do not support 1.5-V HSTL and SSTL Class II I/O standards. (4) This applies for interfaces with both modules and components. (5) The QDRII+ SRAM devices with 2.0 clock cycle latency are not supported due to hardware limitations. (6) Stratix IV devices in the 780- and 1152-pin packages support 36 QDRII+/QDRII SRAM at a lower maximum frequency as detailed in the External Memory Interfaces in Stratix IV Devices chapter in volume 1 of the Stratix IV Device Handbook.

Table 135. Stratix IV Maximum Clock Rate Support for External Memory Interfaces with Full-Rate Controller (Note 1), (2), (3) -2/-2x Speed Grade (MHz) Memory Standards DDR2 SDRAM DDR SDRAM

Notes to Table 135:

(1) Numbers are preliminary until characterization is final. The supported operating frequencies listed here are memory interface maximums for the FPGA device family. Your designs actual achievable performance is based on design and system-specific factors, as well as static timing analysis of the completed design. (2) Column I/Os refer to top and bottom I/Os. Row I/Os refer to left and right I/Os. (3) This applies for interfaces with both modules and components. (4) The row I/O banks do not support 1.5 V HSTL and SSTL Class II I/O standards.

-3 Speed Grade (MHz) Column I/O Banks 233 200 Row I/O Banks (4) 233 200

-4 Speed Grade (MHz) Column I/O Banks 200 200 Row I/O Banks (4) 200 200

Column I/O Banks 267 200

Row I/O Banks (4) 267 200

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

130

Table 136. Stratix IV Maximum Clock Rate Support with the 36 Mode Emulation (Note 1), (2), (3) -2/-2x Speed Grade (MHz) Memory Standards QDRII+SRAM (2.5 clock cycle latency only) (4) QDRII SRAM (1.5-V and 1.8-V HSTL)

Notes to Table 136:

(1) Numbers, based on using the half-rate controller, are preliminary until characterization is final. The supported operating frequencies listed here are memory interface maximums for the FPGA device family. Your designs actual achievable performance is based on design and system-specific factors as well as static timing analysis of the completed design. (2) The performance listed in this table is lower than the performance listed in Table 134 due to double loading of the CQ/CQn pins. Double loading causes degradation in the signal slew rate which affects FPGA delay. Furthermore, due to the difference in slew rate, there is a shift in the setup and hold time window. You can perform an IBIS simulation to illustrate the shift in the clock signals. (3) Column I/Os refer to top and bottom I/Os. Row I/Os refer to left and right I/Os. (4) The QDRII+ SRAM devices with 2.0 clock cycle latency are not supported due to hardware limitations.

-3/-3x Speed Grade (MHz) Column I/O Banks 250 Row I/O Banks (4) 167

4 Speed Grade (MHz) Column I/O Banks 250 Row I/O Banks (4) 167

Column I/O Banks 300

Row I/O Banks (4) 250

300

250

250

167

250

167

External Memory I/O Timing Specifications Table 137 and Table 138 list Stratix IV device timing uncertainties on the read and write data paths. Use these specifications to determine timing margins for source synchronous paths between a Stratix IV FPGA and an external memory device.

Table 137. Sampling Window (SW) - Read Side - Preliminary Sampling window (ps) -2/-2x Speed Grade Memory Type DDR3 DDR2 Differential DDR2 SEIO DDR1 SEIO QDRII/II+ I/O Standard 1.5 SSTL 1.8 V SSTL 1.8 V SSTL 2.5 V SSTL 1.5 V HSTL Width 4 8 4 8 4 8 4 8 9 18 36 QDRII/II+ Emulation QDRII 1.5 V HSTL 1.8 V HSTL 36 9 18 36 Setup 250 250 181 181 231 231 231 231 231 261 261 261 231 261 261 Hold 250 250 306 306 256 256 256 256 256 286 286 328 256 286 286 -3 Speed Grade Setup 300 300 234 234 284 284 284 284 284 314 314 314 284 314 314 Hold 300 300 326 326 276 276 261 261 261 291 291 337 261 291 291 -4 Speed Grade Setup 374 374 257 257 307 307 307 307 307 337 337 337 307 337 337 Hold 374 374 326 326 276 276 261 261 261 291 291 350 261 291 291

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

131

Table 137. Sampling Window (SW) - Read Side - Preliminary Sampling window (ps) -2/-2x Speed Grade Memory Type RLDRAM II I/O Standard 1.5 V HSTL Width 9 18 9 18 Setup 181 211 181 211 Hold 306 336 306 336 -3 Speed Grade Setup 234 264 234 264 Hold 326 356 326 356 -4 Speed Grade Setup 257 287 257 287 Hold 326 356 326 356

Table 138. Transmitter Channel-to-Channel Skew (TCCS) - Write Side - Preliminary TCCS (ps) -2/-2x Speed Grade Memory Type DDR3 DDR2 Differential DDR2 SEIO DDR1 SEIO QDRII/II+ I/O Standard 1.5 SSTL 1.8 V SSTL 1.8 V SSTL 2.5 V SSTL 1.5 V HSTL Width 4 8 4 8 4 8 4 8 9 18 36 QDRII/II+ Emulation QDRII 1.5 V HSTL 1.8 V HSTL 36 9 18 36 RLDRAM II 1.5 9 18 9 18 Lead 260 260 229 229 316 316 313 313 260 290 290 310 229 259 259 260 290 229 259 Lag 260 260 246 246 168 168 157 157 248 278 278 298 246 276 276 248 278 246 276 -3 Speed Grade Lead 290 290 230 230 318 318 315 315 262 292 292 312 230 260 260 262 292 230 260 Lag 290 290 355 355 239 239 222 222 358 388 388 408 355 385 385 358 388 355 385 -4 Speed Grade Lead 310 310 250 250 346 346 343 343 285 315 315 335 250 280 280 285 315 250 280 Lag 310 310 388 388 260 260 242 242 391 421 421 441 388 418 418 391 421 388 418

DLL and DQS Logic Block Specifications Table 139 describes the DLL frequency range specifications for Stratix IV devices.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Switching Characteristics

132

Table 139. Stratix IV DLL Frequency Range Specifications - Preliminary Frequency Range (MHz) Frequency Mode 0 1 2 3 4 5 6 -2/-2x Speed Grade 90 - 150 120 - 200 150 - 240 180 - 300 240 - 370 290 - 450 360 - 560 -3 Speed Grade 90 - 140 120 - 190 150 - 230 180 - 290 240 - 350 290 - 420 360 - 530 -4 Speed Grade 90 - 120 120 - 170 150 - 200 180 - 250 240 - 310 290 - 370 360 - 460 Resolution 22.5 30 36 45 30 36 45

Table 140 describes the DQS phase offset delay per stage for Stratix IV devices.

Table 140. DQS Phase Offset Delay Per Setting (Note 1), (2), (3) Speed Grade -2/-2x -3 -4

Notes to Table 140:

(1) The valid settings for phase offset are -64 to +63 for frequency mode 0 to 3 and -32 to +31 for frequency modes 4 to 6. (2) The typical value equals the average of the minimum and maximum values. (3) The delay settings are linear, with a cumulative delay variation of 40 ps for all speed grades. For example, when using a -2 speed grade and applying a 10 phase offset settings to a 90 phase shift at 400 MHz, the expected average cumulative delay is [625 ps + (10 * 10.5 ps) 20 ps] = 730 ps 20 ps

Min 7 8 8.5

Max 13 14 15.5

Unit ps ps ps

OCT Calibration Block Specifications

Table 141 describes the OCT calibration block specifications for Stratix IV devices.

Table 141. OCT Calibration Block Specifications Preliminary Symbol OCTUSRCLK TOC TCAL TOC TSHIFT TRS _RT Description Clock required by OCT calibration blocks Number of OCTUSRCLK clock cycles required for OCT RS/RT calibration Number of OCTUSRCLK clock cycles required for OCT code to shift out Time required to dynamically switch from RS to RT Min Typ 1000 28 2.5 Max 20 Unit MHz Cycles Cycles ns

Duty Cycle Distortion (DCD) Specifications

Table 142 lists the worst case DCD for Stratix IV devices.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics I/O Timing

133

Table 142. DCD on Stratix IV I/O Pins (Note 1), (2) Preliminary -2/2x Speed Grade Symbol Output Duty Cycle (2)

Notes to Table 142:

(1) Preliminary DCD specification applies to clock outputs from PLLs, global clock tree, and IOE driving dedicated and general purpose I/O pins. (2) Detailed DCD specifications pending silicon characterization.

-3 Speed Grade Min 45 Max 55

-4 Speed Grade Unit Min 45 Max 55 %

Min 45

Max 55

I/O Timing

Altera offers two ways to determine I/O timing: the Excel-based I/O timing and the Quartus II Timing Analyzer. The Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis. The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after place-and-route is complete. 1 The Excel-based I/O timing spreadsheet can be downloaded from the Stratix IV Device Literature webpage.

Programmable IOE Delay

Table 143 shows Stratix IV IOE programmable delay settings.

Table 143. Stratix IV IOE Programmable Delay -3 Speed Grade Parameter D1 D2 D3 D9 D10 Available Settings 16 8 8 16 7 Min Delay (ps) 150 330 155 123 118 Max Delay (ps) 900 700 2581 897 377

Programmable Output Buffer Delay

Table 144 lists the delay chain settings that control the rising and falling edge delays of the output buffer. Default delay is 0 ps.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Glossary

134

Table 144. Programmable Output Buffer Delay Symbol DOUTB UF Parameter Rising and/or falling edge delay Typ 0 (default) 50 100 150 Unit ps ps ps ps

Glossary

Table 145 shows the glossary for this chapter.

Table 145. Glossary Table Letter A B C D Subject Differential I/O Standards Receiver Input Waveforms

Single-Ended Waveform Positive Channel (p) = VIH VID Negative Channel (n) = VIL VCM Ground

Definitions

Differential Waveform

VID pn=0V VID

Transmitter Output Waveforms

Single-Ended Waveform Positive Channel (p) = VOH VOD Negative Channel (n) = VOL VCM Ground

Differential Waveform

VOD pn=0V VOD

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Glossary

135

Table 145. Glossary Table Letter F f HS CLK f HS DR f HS DRDPA G H I J J JTAG Timing Specifications Subject Left/Right PLL input clock frequency. HIGH-SPEED I/O Block: Maximum/minimum LVDS data transfer rate (fHS DR = 1/TUI), non-DPA. HIGH-SPEED I/O Block: Maximum/minimum LVDS data transfer rate (fHS DRDP A = 1/TUI), DPA. HIGH-SPEED I/O Block: Deserialization factor (width of parallel data bus). JTAG Timing Specifications are in the following figure:

TMS

Definitions

TDI t JCP t JCH TCK tJPZX TDO t JPCO t JPXZ t JCL t JPSU t JPH

K L M N O P

PLL Specifications Diagram of PLL Specifications (1)

Switchover

The block diagram shown in the following figure highlights the PLL Specification parameters:

CLKOUT Pins

fOUT_EXT

CLK

fIN

Core Clock

fINPFD

PFD CP LF VCO

fVCO

Counters C0..C9

fOUT

GCLK

RCLK

Key Reconfigurable in User Mode External Feedback

Note:

(1) CoreClock can only be fed by dedicated clock input pins or PLL outputs.

Q R RL

Receiver differential input discrete resistor (external to Stratix IV device).

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Glossary

136

Table 145. Glossary Table Letter S Subject SW (sampling window) Definitions The period of time during which the data must be valid in order to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window as shown in (the following figure):

Bit Time

0.5 x TCCS

RSKM

Sampling Window (SW)

RSKM

0.5 x TCCS

Timing Diagram Single-ended voltage referenced I/O standard The JEDEC standard for SSTl and HSTL I/O defines both the AC and DC input signal values. The AC values indicate the voltage levels at which the receiver must meet its timing specifications. The DC values indicate the voltage levels at which the final logic state of the receiver is unambiguously defined. Once the receiver input has crossed the AC value, the receiver changes to the new logic state. The new logic state is then maintained as long as the input stays beyond the AC threshold. This approach is intended to provide predictable receiver timing in the presence of input waveform ringing as shown in the following figure: Single-Ended Voltage Referenced I/O Standard

VCCIO

VOH VIH (AC )

VIH(DC) VREF

VIL(DC) VIL(AC )

VOL

VSS

tC

High-speed receiver/transmitter input and output clock period.

TCCS (channelThe timing difference between the fastest and the slowest output edges, including tCO to-channel-skew) variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under S in this table) t DUTY HIGH-SPEED I/O Block: Duty cycle on high-speed transmitter output clock. Timing Unit Interval (TUI) The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = 1/(Receiver Input Clock Frequency Multiplication Factor) = tC /w) t FA LL t INC CJ t OUTP J_IO t OUTP J_DC t RIS E U Signal high-to-low transition time (80-20%) Cycle-to-cycle jitter tolerance on PLL clock input Period jitter on general purpose I/O driven by a PLL Period jitter on dedicated clock output driven by a PLL Signal Low-to-high transition time (20-80%)

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Documents Referenced

137

Table 145. Glossary Table Letter V VIC M VID VDIF (AC ) VDIF (DC) VIH VIH( AC ) VIH( DC) VIL VIL( AC) VIL( DC) VOCM VOD W X Y Z W Subject VCM (DC) DC Common Mode Input Voltage. Input Common Mode Voltage: The common mode of the differential signal at the receiver. Input differential Voltage Swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver. AC differential Input Voltage: Minimum AC input differential voltage required for switching. DC differential Input Voltage: Minimum DC input differential voltage required for switching. Voltage Input High: The minimum positive voltage applied to the input which will be accepted by the device as a logic high. High-level AC input voltage High-level DC input voltage Voltage Input Low: The maximum positive voltage applied to the input which will be accepted by the device as a logic low. Low-level AC input voltage Low-level DC input voltage Output Common Mode Voltage: The common mode of the differential signal at the transmitter. Output differential Voltage Swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. HIGH-SPEED I/O BLOCK: Clock Boost Factor Definitions

Documents Referenced

This chapter references the following documents:

External Memory Interfaces in Stratix IV Devices chapter in volume 1 of the Stratix IV Device Handbook PowerPlay Early Power Estimator User Guide for Stratix III and Stratix IV FPGAs

PowerPlay Power Analysis chapter in the Quartus II Handbook

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

Chapter 1: DC and Switching Characteristics Document Revision History

138

Document Revision History

Table 146 shows the revision history for this document.

Table 146. Document Revision History Date and Document Version November 2008 v2.1 November 2008 v2.0

Changes Made Edited I/O Timing section Minor text edits. Updated Table 119, Table 132, Table 134 Table 139 Updated Table 11, Table 12, Table 14, Table 15, and Table 126. Removed figures from Transceiver Performance Specifications on page 110 that are repeated in the glossary.

Summary of Changes Minor text edits.

August 2008 v1.1

Minor text edits and an additional note to Table 126.

May 2008 v1.0

Initial release.

December 2008

Altera Corporation

Stratix IV Device Handbook, Volume 4

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- ProLaser III Users Manual 2006-05-08 PDFDocument47 pagesProLaser III Users Manual 2006-05-08 PDFPeter Shearer100% (1)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- 6 Bass Sequencing Tricks From Daft PunkDocument4 pages6 Bass Sequencing Tricks From Daft PunkDustinNguyenNo ratings yet

- Wiley .Verilog - Coding.for - Logic.synthesis. (2003)Document334 pagesWiley .Verilog - Coding.for - Logic.synthesis. (2003)Nguyễn Hồ Nguyên Vũ100% (12)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Scott Pilgrim Vs The World Production NotesDocument30 pagesScott Pilgrim Vs The World Production NotesWilliam Fonda0% (1)

- Perusal Script: Chip Deffaa Irving Berlin Chip DeffaaDocument77 pagesPerusal Script: Chip Deffaa Irving Berlin Chip DeffaaJoeHodgesNo ratings yet

- Airbus A320 CalloutsDocument24 pagesAirbus A320 CalloutsRaúl Martín100% (3)

- Stone Sour TaciturnDocument6 pagesStone Sour TaciturnDavid NewmanNo ratings yet

- Asic DesignDocument59 pagesAsic DesignManjunath ReddyNo ratings yet

- 1970 Musical TheatreDocument5 pages1970 Musical Theatrejack fernNo ratings yet

- Verification Planning PDFDocument7 pagesVerification Planning PDFManjunath ReddyNo ratings yet

- TCL BasicsDocument118 pagesTCL Basicssn10mmNo ratings yet

- Emr 1745Document13 pagesEmr 1745Marika Serasi0% (1)

- 8085 MicroprocessorDocument23 pages8085 Microprocessorauromaaroot196% (55)

- AQU4518R19v06: Antenna SpecificationsDocument2 pagesAQU4518R19v06: Antenna SpecificationsЕвгений Грязев0% (1)

- Formal Verification SolutionDocument80 pagesFormal Verification SolutionManjunath ReddyNo ratings yet

- Coding and Synthesis With VerilogDocument23 pagesCoding and Synthesis With Verilogshekharjha20No ratings yet

- Snug12 Slides FinalDocument29 pagesSnug12 Slides FinalManjunath ReddyNo ratings yet

- Expert Training on Verilog FIFO DesignDocument23 pagesExpert Training on Verilog FIFO DesignGupta AakashNo ratings yet

- 'Ifdef Text - Macro - Identifier: Ieee Hardware Description Language STD 1364-2001Document2 pages'Ifdef Text - Macro - Identifier: Ieee Hardware Description Language STD 1364-2001Manjunath ReddyNo ratings yet

- Lesson VerilogDocument59 pagesLesson VerilogManjunath ReddyNo ratings yet

- CFIDocument4 pagesCFIManjunath ReddyNo ratings yet

- TCLDocument81 pagesTCLManjunath ReddyNo ratings yet

- Flash MemoryDocument95 pagesFlash MemoryManjunath Reddy0% (2)

- Verilog HDL Testbench PrimerDocument14 pagesVerilog HDL Testbench Primernirmal_jate1No ratings yet

- stx4 5v4Document80 pagesstx4 5v4Manjunath ReddyNo ratings yet

- Verilog l12 MitDocument23 pagesVerilog l12 MitNishant JainNo ratings yet

- DmaDocument19 pagesDmaManjunath ReddyNo ratings yet

- C Programming TutorialDocument410 pagesC Programming TutorialManjunath ReddyNo ratings yet

- Analog Design Methodology Jnotor r3Document17 pagesAnalog Design Methodology Jnotor r3Manjunath ReddyNo ratings yet

- Data Conversion Based On FPGA Thomas KleinDocument31 pagesData Conversion Based On FPGA Thomas KleinManjunath ReddyNo ratings yet

- JESD207Document34 pagesJESD207rftotoNo ratings yet

- NiosDocument8 pagesNiosManjunath ReddyNo ratings yet

- ACTUAL FINAL DATE 2007 DFMTutorial Kahng Intro PDFDocument10 pagesACTUAL FINAL DATE 2007 DFMTutorial Kahng Intro PDFManjunath ReddyNo ratings yet

- C Programming TutorialDocument410 pagesC Programming TutorialManjunath ReddyNo ratings yet

- Digital Electronics: Flip-Flops - D, T, J-K Types & Waveforms ExplainedDocument17 pagesDigital Electronics: Flip-Flops - D, T, J-K Types & Waveforms ExplainedRongeet SodhiNo ratings yet

- Lecture Notes For Digital ElectronicsDocument43 pagesLecture Notes For Digital ElectronicsShruti GuptaNo ratings yet

- Perlbook PreviewDocument14 pagesPerlbook PreviewManjunath ReddyNo ratings yet

- LearnersDocument14 pagesLearnersManjunath ReddyNo ratings yet

- 20 Minor Key Fusion Licks: Lick 5Document3 pages20 Minor Key Fusion Licks: Lick 5JuanNo ratings yet

- Daniel Anna Cat: He She ItDocument20 pagesDaniel Anna Cat: He She ItJosé RodriguezNo ratings yet

- HeadRush Guide - BlocksDocument46 pagesHeadRush Guide - BlocksPaulo VilanovaNo ratings yet

- Poems For Practice AnnotationDocument6 pagesPoems For Practice AnnotationxxpolxxNo ratings yet

- Harp On This 911Document8 pagesHarp On This 911api-296228172No ratings yet

- Godwin Okebaram Uwah - Pirandellism and Samuel Beckett's Plays (Scripta Humanistica, Volume 48) (1989)Document147 pagesGodwin Okebaram Uwah - Pirandellism and Samuel Beckett's Plays (Scripta Humanistica, Volume 48) (1989)AniNo ratings yet

- Principal I&C Engineer or Principal Instrumentation and ControlDocument3 pagesPrincipal I&C Engineer or Principal Instrumentation and Controlapi-78419400100% (1)