Professional Documents

Culture Documents

Analog and Digital Integrated Circuit Question Bank

Uploaded by

MATHANKUMAR.SOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analog and Digital Integrated Circuit Question Bank

Uploaded by

MATHANKUMAR.SCopyright:

Available Formats

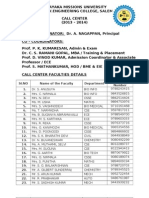

VINAYAKA MISSIONS UNIVERSITY Vinayaka Missions Kirupananda Variyar Engineering College SALEM 636 308

Programme Subject Name Objective UNIT - I 1. Define virtual short.

B.E. BIOMEDICAL ENGINEERING ANALOG AND DIGITAL ICs Question Bank

Semester

PART A

2. What is differential amplifier? 3. Define slew rate. 4. List the important characteristics of an ideal Op - Amp. 5. Define CMRR of an Op - Amp. 6. Differentiate Average & peak detector. 7. Mention some of the linear and non linear applications of Op - Amp. 8. Draw the integrator circuit using Op - Amp. 9. Define precision diode. 10. What is hysteresis? 11. Draw the circuit diagram of Astable vibrator. 12. What is meant by filters? What are the types? 13. Define PSRR of an Op - Amp. 14. Write down the applications of precision diode. 15. What is Peak detector? 16. Draw the circuit diagram of triangular generator. 17. Write short notes on Schmitt trigger and List out the applications. 18. What are the limitations of integrated circuits? 19. Draw the Op Amp symbol and state its important terminals. 20. State the advantages of voltage follower. 21. When inverting amplifier is called phase inverter?

22. Draw the circuit diagram of subtractor. 23. List the applications of differentiator circuit. 24. State the applications of V to I converter and I to V converter. 25. Draw the circuit diagram of full wave rectifier using Op - Amp. 26. List out the applications of an instrumentation amplifier and what are the requirements of instrumentation amplifier? 27. State the applications of monostable multivibrator. 28. What is clamper circuit? How clamper circuits are classified? 29. List the applications of Log amplifiers.

UNIT - I

PART B

1. Draw the circuit of inverting and non inverting amplifiers using Op Amp and Derive an expression for their gain. (12 Marks) 2. Explain integrator and differentiator with a neat diagram. Marks) 3. i) What is virtual ground? Explain with a neat circuit diagram. ii) Explain briefly about ideal differential amplifier. (12

(7 Marks) (5 Marks)

4. i) Draw the block schematic of an Op Amp and briefly explain each block. (6 Marks) ii) What are the Advantages and Disadvantages of Op - Amp? (4 Marks) iii) List the Applications and Features of Op - Amp. (2 Marks) 5. Explain Astable & Monostable multivibrator using Op - Amp with a neat diagram. (12 Marks) 6. Briefly explain triangular wave generators with a neat circuit diagram. (12 Marks) 7. Explain in detail about V to I converter and I to V converter. (12 Marks) 8. Explain about instrumentation amplifier with a neat sketch. (12 Marks) 9. Explain briefly about summing inverting and Non inverting amplifier. 10. i) Write short notes on adder, subtractor, and bridge amplifier. ii) Write short notes on half wave rectifier. iii) Explain the peak detector circuit using integrator. (12 Marks) (6 Marks) (2 Marks) (4 Marks)

UNIT II 1. Define phase comparator. 2. Define lock in range. 3. Define capture range.

PART A

4. List out the typical applications of Phase Locked Loop. 5. Define voltage controlled oscillator. 6. What is monotonicity? 7. Draw the blocks of PLL. 8. Write the operation of Voltage to Frequency ADC. 9. Define counter ramp ADC. 10. What is pull- in time? 11. Define resolution of DAC. 12. State advantage of R- 2R ladder type DAC. 13. Which is the fastest ADC and why? 14. List out the advantages of DAC. 15. Define amplitude modulation. 16. List out the disadvantages of ADC. 17. Give the specification of DAC. 18. What are the different types of ADC? 19. What is linear error? 20. Define settling time. 21. What are the stages through which PLL operates? 23. Listout the advantage and draw backs of dual slop ADC. 24. Write the two problems associated with DM. 25. Define Voltage to Frequency conversion factor. 22. Where is the successive approximation type ADC used?

UNIT II

PART B

1. i) Draw and explain the working principle of op-amp based voltage controlled oscillator circuit. (7 Marks) ii) Derive the expression for capture range of PLL. (5 Marks) 2. i) Derive the expression for lock range of PLL. ii) Explain AM demodulation using PLL. 3. i) Draw and explain frequency translator using PLL. ii) What are the applications of PLL 4. i) Briefly explain block diagram of PLL. IC 565 ii) Write short notes on frequency multiplication 5. i) Explain in detail about successive approximation DAC. ii) Give some application of AM detection. 6. i) Explain in detail about phase comparator. ii) What is meant by counters and give example? 7. i) Explain in detail about V to F & counter ramp ADC. ii) Mention some applications of parallel ADC. 8. Explain the operation of D/A converter and give some of the Advantages and Disadvantages (5 Marks) (7 Marks) (8 Marks) (4 Marks) (6 Marks) (6 Marks) (8 Marks) (4 Marks) (8 Marks) (4 Marks) (8 Marks) (4 Marks) (12 Marks)

UNIT III 1. Define radix. 2. What are the number systems? 3. Define the following: minterm and maxterm. 4. What is meant by prime implicant?

PART A

5. Convert the given binary (1101010110)10 into gray code. 6. Distinguish between 1s and 2s complements. 7. Define the terms disjunction and conjunction. 8. What are the logic gates? 9. Define SOP and POS. 10. What do you meant by LSB and MSB? 11. How will you find 2s complement of a binary number? 12. What are the alphanumeric codes? 13. Convert the given gray code (1011011101) into binary code. 14. Define karnaugh maps. 15. Write the truth table of AND, OR and NAND gates. 16. What is meant by excess 3 decimal numbers? 17. Define the law of Boolean algebra. 18. What is meant by universal gates? 19. What is Multivariable Theorem? 20. Convert (25)10 to binary. 21. What are the types of karnaugh map? 22. Write the truth table of X-OR and X-NOR. 23. Distinguish between Boolean addition and Binary addition. 24. What is meant by multilevel gates networks? 25. What are the drawbacks of K map method? 26. State De Morgans law. 27. What is the number of bits in ASCII code? What is the need for ASCII code? 28. Simplify : A + AB + A + B

UNIT III

PART B

1. i) Reduce the following function using k-map technique f ( A, B, C , D) = m(0,1, 4,8,9,10) ii) What are the methods for converting Decimal to Binary conversion? Give some examples. 2. i) Minimise the following expression in the POS form f ( A, B, C , D) = M (0, 2,3,8,9,12,13,15) ii) Explain De Morgans theorem and the duality principle with proof. 3. i) Minimize the Boolean expression: AB + ABC + ABC + ABC ii) Convert the given expression in to standard SOP. f ( A, B, C ) = AC + AB + BC + AC 4. i) Convert the following (37)10 to equivalent hexadecimal ii) Convert the following (25B) 16, (5A9.B4)16 to octal and binary. iii) Perform (4)10 - (9)10 using the 2s complement method. iv) Subtract (9)10 - (4)10 using 1s complement method. 5. Find the following i) (CB9.F5)16 + (AB8.CD)16. ii) (9E4A)16 (5FD6)16 iii) (E75)16 * (2A)16 iv) (745)8 - (263)8 6. Subtract the following using 2s complement. (i) (ii) (iii) (iv) 11101010 & 11010101 10101010 & 11010100 01011101 & 11001010 10010101 & 11100010 (3 Marks) (3 Marks) (3 Marks) (3 Marks) (6 Marks) (2 Marks) (4 Marks) (3 Marks) (3 Marks) (3 Marks) (3 Marks) (3 Marks) (3 Marks) (6 Marks) (6 Marks) (6 Marks) (6 Marks) (6 Marks)

7.

i) Convert 10101011 into its equivalent Decimal, Octal, Hexadecimal. ii) What the two method for Simplification of Boolean Functions

(6 Marks) (6 Marks) (3 Marks) (3 Marks) (3 Marks) (3 Marks)

8.

i) Obtain the octal equivalent of (3964)10 . ii) Convert octal number (1654)8 into decimal system. iii) Convert (634.640625)10 to the octal system. iv) Convert (17.35)10 to binary form.

9.

Minimize the expression using Quine McCluskey method. Y = ABC D + ABCD + ABC D + ABCD + ABCD + ABC D

10.

i) Reduce the following function using Karnaugh map technique. f ( A, B, C , D) = m(5, 6, 7,12,13) + d (4,9,14,15) ii) Reduce the following function using Karnaugh map technique. f ( A, B, C , D) = M (0,3, 4, 7,8,10,12,14) + d (2, 6) (6 Marks) (6 Marks)

UNIT IV

PART A

1. Define half adder. 2. What do you meant by Encoder? 3. 5. List out the basic types of PLD. 4. Define full adder. What is PLA? How its differ from ROM? 6. Define half subtractor. 7. What is meant by decoder? 8. 10. 11. 13. 14. 16. 18. 19. 20. 21. 22. 23. 24. 25. Differentiate sum and carry. 9. What is meant by a full subtractor? Draw a full subtractor circuit. Draw the logic diagram of half adder. Write a design procedure of combinational circuits. 12. Differentiate decoder and encoder. What is the similar between a half adder and a half subtractor? What do you meant by Comparator? 15. Define Multiplier. What is meant by multiple bit adders? 17. Write short notes on ROM. Define propagation delay. What is PAL? How it differs from ROM and PLA? What is meant by Combinational circuits? Draw the logic diagram of BCD to Excess 3 code converter Write the truth table of Full adder What is meant by binary decoder? What are the difference between decoder and demultiplexer? Write short notes on priority encoder.

UNIT IV

PART B

1.

i) Design of half adder and full adder using gates. ii) Design the logic circuit for odd parity checker.

(8 Marks) (4 Marks) (8 Marks) (4 Marks) (8 Marks) (4 Marks) (4 Marks) (8 Marks)

2.

i) Design of half subtractor & full subtractor using gates. ii) List out the design procedure of a combinational circuit.

3. i) Design a 3 to 8 Decoder using gates. ii) Draw the logic diagram of BCD to Excess 3 code converter. 4. i) Explain the various types of ROM. ii) Implement the following Boolean function using ROM. F1 ( A1 , A0 ) = m(1, 2) and F2 ( A1 , A0 ) = m(0,1,3) 5. i) Explain in detail about parallel binary adder with neat block diagram. ii) Give the comparison between PROM, PLA and PAL . 6. 7.

(6 Marks) (6 Marks)

Explain details about the design procedure of circuit 4 - bit multiplier with example. (12 Marks) i) Design a BCD to 7-Segment display decoder. ii) Design a priority encoder. (6 Marks) (6 Marks)

8. 9. 10.

How will you build a full adder using two half adders and an OR gate? Explain briefly. (12 Marks) Draw and explain the block diagram of n - bit parallel and binary adder subtractor. i) Draw and explain the block diagram of PLA. ii) Implement the following Boolean function using PLA. A( x, y, z ) = m(1, 2, 4, 6) , B ( x, y, z ) = m(0,1, 6, 7) & C ( x, y, z ) = m(2, 6) (12 Marks) (4 Marks) (8 Marks)

UNIT V 1. What is sequential circuit? 2. Define flip-flop. 3. What is shift registers? 4. 5. List out the various types of flip-flop. Define metastability. 6. Write the specifications of shift register ICs 7. List the function of asynchronous inputs. 8. What is meant by trigger?

PART A

9. Derive the characteristic equation of T flip flop. 10. What is universal shift register? 11. Draw a block diagram of sequential circuit. 12. Derive the characteristic equation of SR flip flop. 13. Write the specifications of counter ICs. 14. Define a register and shift register. 15. Write down the 74194 IC specifications. 16. What are the applications of flip-flop? 17. What is meant by synchronous circuit? 18. Define clock period. 19. What is meant by state table? 20. Draw a logic diagram of counters. 21. What is meant by state diagram? 22. Draw the state diagram of JK flip flop. 23. What is meant by asynchronous circuit? 24. Derive the characteristic equation of JK flip flop 25. What are the bistable elements?

UNIT V 1.

PART B (6 Marks) (6 Marks) (12 Marks)

i) Distinguish between combinational and sequential logic circuits. ii) What is race around condition? How its avoided? 2. Explain in detail SR & D flip-flop with neat circuit diagram

3.

Explain synchronous decade counter using JK flip-flop with block diagram in detail. (12 Marks) 4. i) Distinguish between synchronous and asynchronous sequential circuits. ii) Comparison between synchronous and asynchronous counters. 5. Explain in detail JK & T flip-flop with neat circuit diagram 6. i) Briefly explain about Ring counter with neat block diagram. ii) Write a short notes on State tables and State diagram 7. Explain right shift register using JK flip-flop with block diagram in detail. (6 Marks) (6 Marks) (12 Marks) (8 Marks) (4 Marks) (12 Marks)

8. 9. 10.

Explain synchronous decade counter using D flip-flop with block diagram in detail. (12 Marks) Explain right shift register using D flip-flop with block diagram in detail. (12 Marks)

Explain synchronous decade counter using T flip-flop with block diagram in detail. (12 Marks)

You might also like

- 68rfe IntroductionDocument71 pages68rfe IntroductionThePokeOne83% (6)

- PIC QuestionsDocument4 pagesPIC Questionsgopikrishnarao100% (1)

- ANALOG & DIGITAL INTEGRATED CIRCUIT (ADIC) Model Question PaperDocument3 pagesANALOG & DIGITAL INTEGRATED CIRCUIT (ADIC) Model Question PaperMATHANKUMAR.SNo ratings yet

- Digital Electronics Interview QuestionsDocument3 pagesDigital Electronics Interview QuestionsShailesh Kumar100% (1)

- Linear Integrated Circuit Questions and AnswersDocument22 pagesLinear Integrated Circuit Questions and Answerselakya78% (23)

- Digital Electronics Interview QuestionsDocument19 pagesDigital Electronics Interview Questionsetasuresh50% (2)

- ADVANCED ANALOG IC DESIGN Lab ManualDocument27 pagesADVANCED ANALOG IC DESIGN Lab ManualJahnavi Ratnam0% (1)

- Question Bank: UNIT I - Sensors Part - A (2 Marks)Document7 pagesQuestion Bank: UNIT I - Sensors Part - A (2 Marks)MAHALAKSHMI MALINI100% (3)

- (PDF) Teach Your Baby Math - Glenn DomanDocument200 pages(PDF) Teach Your Baby Math - Glenn Domansugapovex0% (1)

- Nitriding Ces-196 ADocument3 pagesNitriding Ces-196 AMATHANKUMAR.SNo ratings yet

- Bio Signal Processing Question BankDocument5 pagesBio Signal Processing Question BankMATHANKUMAR.S0% (1)

- ELECTROMAGNETIC THEORY - Two Mark Questions and AnswersDocument12 pagesELECTROMAGNETIC THEORY - Two Mark Questions and AnswersRavi Kannappan80% (5)

- RMK Engineering College MEMS Question BankDocument4 pagesRMK Engineering College MEMS Question Bankvirudaianand0% (1)

- Avanto Magnet System Error MessagesDocument21 pagesAvanto Magnet System Error MessagesMuhammad Ahmad75% (4)

- Content Beyond SyllabusDocument3 pagesContent Beyond SyllabusMohan Kumar M100% (1)

- Dec Lab QuestionsDocument25 pagesDec Lab QuestionsPrathiksha Harish Medical Electronics EngineeringNo ratings yet

- EC8761-Advanced Communication Lab ManualDocument116 pagesEC8761-Advanced Communication Lab ManualPasupathi T100% (3)

- Question Bank Advanced ProcessorsDocument2 pagesQuestion Bank Advanced ProcessorsManish Narkhede67% (3)

- ST Veronica Giuliani For OFS PresentationDocument7 pagesST Veronica Giuliani For OFS Presentationleo jNo ratings yet

- AP7101-Advanced Digital Signal Processing Question BankDocument8 pagesAP7101-Advanced Digital Signal Processing Question BanksharmikbkNo ratings yet

- EC8462-Linear Integrated Circuits Lab ManualDocument85 pagesEC8462-Linear Integrated Circuits Lab ManualArul Perumal85% (13)

- Biomaterials Symposium 2007 Materials TomorrowDocument12 pagesBiomaterials Symposium 2007 Materials TomorrowMATHANKUMAR.SNo ratings yet

- Biomedical Engineering Unit - I Two Mark QuestionsDocument7 pagesBiomedical Engineering Unit - I Two Mark QuestionsMATHANKUMAR.SNo ratings yet

- ANALOG AND DIGITAL IC Short Question With AnswerDocument46 pagesANALOG AND DIGITAL IC Short Question With AnswerMATHANKUMAR.S100% (1)

- AWP Unit Wise Question BankDocument8 pagesAWP Unit Wise Question Bankganesh4u_p100% (1)

- Viva Questions For Advanced Communication LabDocument4 pagesViva Questions For Advanced Communication Labanittadevadas57% (7)

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)rajkumarsac100% (1)

- Digital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?Document11 pagesDigital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?yashuNo ratings yet

- Question Bank-16 MarksDocument2 pagesQuestion Bank-16 MarksBala913No ratings yet

- LDICA Digital NotesDocument263 pagesLDICA Digital NotesAbhishek Reddy Garlapati80% (5)

- Linear Integrated Circuits Lab Viva VoceDocument8 pagesLinear Integrated Circuits Lab Viva Voceselvi0412100% (12)

- Electronic Circuits I 2 Marks Question AnswersDocument13 pagesElectronic Circuits I 2 Marks Question Answersbala_smNo ratings yet

- WSN Unit-Wise Imp. QuestionsDocument4 pagesWSN Unit-Wise Imp. QuestionsMarkandeyaNGupta100% (1)

- Optical Networks QUESTION BANKDocument11 pagesOptical Networks QUESTION BANKS.J Angelin Praveena0% (1)

- Analog and Digital Ic'S Short Questions With AnswersDocument41 pagesAnalog and Digital Ic'S Short Questions With Answerspriya adhavanNo ratings yet

- DSP Important Viva QuestionsDocument3 pagesDSP Important Viva QuestionsDeepak Sahu100% (2)

- Design and test analog and digital circuitsDocument105 pagesDesign and test analog and digital circuitseshwari2000100% (1)

- EI2311-Biomedical Instrumentation Question BankDocument20 pagesEI2311-Biomedical Instrumentation Question BankrajapandiyaNo ratings yet

- Medical Optics Question Bank (B.e)Document6 pagesMedical Optics Question Bank (B.e)MATHANKUMAR.S100% (2)

- LINEAR INTEGRATED CIRCUIT - Question Bank (ECE, EIE & BME)Document7 pagesLINEAR INTEGRATED CIRCUIT - Question Bank (ECE, EIE & BME)MATHANKUMAR.SNo ratings yet

- 3.EC8791 - ERTS - 2 Mark Q&ADocument39 pages3.EC8791 - ERTS - 2 Mark Q&AVinothkumar Uruman88% (8)

- 15ecl48-VTU-raghudathesh-BJT MIXER PDFDocument2 pages15ecl48-VTU-raghudathesh-BJT MIXER PDFraghudatheshgp100% (1)

- Cad For Vlsi Circuits 2 PDFDocument2 pagesCad For Vlsi Circuits 2 PDFrajasekarkpr100% (1)

- VLSI Unit-IVDocument87 pagesVLSI Unit-IVUma Maheswari100% (2)

- Introduction To Electronics and Communication (BESCK104C/BESCK204C) - Analog and Digital Communication (Module 5)Document106 pagesIntroduction To Electronics and Communication (BESCK104C/BESCK204C) - Analog and Digital Communication (Module 5)Shrishail Bhat75% (4)

- EC8702 ADHOC & WSN PresentationDocument57 pagesEC8702 ADHOC & WSN PresentationDharani Kumar89% (27)

- Microwave & Optical Engineering Question BankDocument47 pagesMicrowave & Optical Engineering Question BankThiagu RajivNo ratings yet

- Medical Optics - 2 Marks With AnswerSDocument27 pagesMedical Optics - 2 Marks With AnswerSBharath V100% (3)

- Designing ASICs Question Bank GuideDocument4 pagesDesigning ASICs Question Bank GuideHarshit ChaudharyNo ratings yet

- CMOS Digital VLSI Design Periodical Test ReviewDocument4 pagesCMOS Digital VLSI Design Periodical Test ReviewDarwinNo ratings yet

- Microwave Viva QuestionsDocument28 pagesMicrowave Viva Questionsqwerty100% (2)

- 2 Marks Ldica NotesDocument8 pages2 Marks Ldica NotesRAJOLI GIRISAI MADHAV100% (2)

- VTU Advanced Communication LAB Manual 2020 - KLS VDIT HaliyalDocument69 pagesVTU Advanced Communication LAB Manual 2020 - KLS VDIT Haliyalkartik balojiNo ratings yet

- DTE LAB MANUAL - 2017 RegulationDocument90 pagesDTE LAB MANUAL - 2017 RegulationGiriprasath.D67% (3)

- PTSP 2marks QuestionsDocument4 pagesPTSP 2marks QuestionsmanikrishnaswamyNo ratings yet

- Question BankDocument37 pagesQuestion BankLiu Li100% (1)

- Anallysis and Design of Analog Integrated Circuits QuestionsDocument5 pagesAnallysis and Design of Analog Integrated Circuits QuestionsshankarNo ratings yet

- 6th Sem Manual 18ECL67 2021-22 FULLDocument87 pages6th Sem Manual 18ECL67 2021-22 FULLJames100% (2)

- Low Power Vlsi Question PaperDocument2 pagesLow Power Vlsi Question Paperustadkrishna100% (3)

- Analog & Digital Integrated CircuitsDocument11 pagesAnalog & Digital Integrated CircuitssakthikothandapaniNo ratings yet

- Ec2203 Digital ElectronicsDocument8 pagesEc2203 Digital ElectronicspappujayaNo ratings yet

- Digital Electronics QBDocument7 pagesDigital Electronics QBvinaytmkNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- DSD Question Bank PDFDocument11 pagesDSD Question Bank PDFSanjay SharmaNo ratings yet

- EE6301 DLC Question Bank Rejinpaul 2Document8 pagesEE6301 DLC Question Bank Rejinpaul 2aruljothiNo ratings yet

- Ec34 Question BankDocument6 pagesEc34 Question Bankkartheeswaran11No ratings yet

- A Novel Smart Billing System For Energy Consumption Through Wireless Network (EIE)Document6 pagesA Novel Smart Billing System For Energy Consumption Through Wireless Network (EIE)MATHANKUMAR.SNo ratings yet

- Profile - Mathankumar Subramaniam - AP / ELECTRICAL & ELECTRONICSDocument14 pagesProfile - Mathankumar Subramaniam - AP / ELECTRICAL & ELECTRONICSMATHANKUMAR.SNo ratings yet

- Adaptive Control Question Bank Without Answer KeyDocument5 pagesAdaptive Control Question Bank Without Answer KeyMATHANKUMAR.S100% (1)

- Electrical & Electronics Based Project: A Biosensor Based On Silver Enhanced Self Assembled RFID Antenna - BMEDocument4 pagesElectrical & Electronics Based Project: A Biosensor Based On Silver Enhanced Self Assembled RFID Antenna - BMEMATHANKUMAR.SNo ratings yet

- Biomedical Engineering Alumi Details (Vmkvec)Document3 pagesBiomedical Engineering Alumi Details (Vmkvec)MATHANKUMAR.SNo ratings yet

- Renewable Energy Resources in India (Conventional Vs Non-Conventional Energy)Document26 pagesRenewable Energy Resources in India (Conventional Vs Non-Conventional Energy)MATHANKUMAR.S100% (1)

- Biomedical Engineering Project: A Biosensor Based On Silver Enhanced Self Assembled Rfid Antenna.Document4 pagesBiomedical Engineering Project: A Biosensor Based On Silver Enhanced Self Assembled Rfid Antenna.MATHANKUMAR.SNo ratings yet

- Sim Controlled Speed Convernor System-A Network Based Traffic Control SystemDocument9 pagesSim Controlled Speed Convernor System-A Network Based Traffic Control SystemMATHANKUMAR.SNo ratings yet

- Electrical Engineering QUESTION BANKDocument7 pagesElectrical Engineering QUESTION BANKMATHANKUMAR.S100% (1)

- An in Vitro Diagnostic Assay's Determine by Using of Beer Lambert's LawDocument16 pagesAn in Vitro Diagnostic Assay's Determine by Using of Beer Lambert's LawMATHANKUMAR.SNo ratings yet

- Renewable Energy by MathanDocument30 pagesRenewable Energy by MathanMATHANKUMAR.SNo ratings yet

- Matlab Basic Questions Without AnswersDocument1 pageMatlab Basic Questions Without AnswersMATHANKUMAR.SNo ratings yet

- BioMedical Informatics Introduction and OverviewDocument34 pagesBioMedical Informatics Introduction and OverviewMATHANKUMAR.SNo ratings yet

- Telemedicine-Introduction: Telemedicine Is The Remote Communication of Information To Facilitate Clinical CareDocument8 pagesTelemedicine-Introduction: Telemedicine Is The Remote Communication of Information To Facilitate Clinical Caresuhail_ahmed018No ratings yet

- Non Teaching FacultyVacation Details (Department of Bme & Eie)Document1 pageNon Teaching FacultyVacation Details (Department of Bme & Eie)MATHANKUMAR.SNo ratings yet

- Fourth Year Course Medical InformaticsDocument28 pagesFourth Year Course Medical InformaticsMATHANKUMAR.SNo ratings yet

- Department Faculty Responsibility Details (BME) FinalDocument1 pageDepartment Faculty Responsibility Details (BME) FinalMATHANKUMAR.SNo ratings yet

- Department Faculty Responsibility Details (EIE) FinalDocument1 pageDepartment Faculty Responsibility Details (EIE) FinalMATHANKUMAR.SNo ratings yet

- Top Three Rankers in EIEDocument1 pageTop Three Rankers in EIEMATHANKUMAR.SNo ratings yet

- VMKV Engineering CollegeDocument6 pagesVMKV Engineering CollegeMATHANKUMAR.SNo ratings yet

- Top Three Rankers in BMEDocument1 pageTop Three Rankers in BMEMATHANKUMAR.SNo ratings yet

- VMKVEC Salem Call Center FacultiesDocument6 pagesVMKVEC Salem Call Center FacultiesMATHANKUMAR.SNo ratings yet

- New Bio Data Form Bio Medical Final YearDocument11 pagesNew Bio Data Form Bio Medical Final YearMATHANKUMAR.SNo ratings yet

- Assistive Technology For The Dumb: Abiya Francis Ashwani M.D Aswathi M.CDocument4 pagesAssistive Technology For The Dumb: Abiya Francis Ashwani M.D Aswathi M.CMATHANKUMAR.SNo ratings yet

- Breast Cancer (Research Paper)Document12 pagesBreast Cancer (Research Paper)Katrina Arnaiz100% (3)

- Sponsor Project List EEEDocument3 pagesSponsor Project List EEEMATHANKUMAR.SNo ratings yet

- Toeplitz MatricesDocument3 pagesToeplitz MatricesMATHANKUMAR.SNo ratings yet

- Ravikumar Gaurav (Events Details)Document6 pagesRavikumar Gaurav (Events Details)MATHANKUMAR.SNo ratings yet

- A Comparison of Fuel Cell Testing Protocols PDFDocument7 pagesA Comparison of Fuel Cell Testing Protocols PDFDimitrios TsiplakidesNo ratings yet

- Hope 03 21 22Document3 pagesHope 03 21 22Shaina AgravanteNo ratings yet

- ClarifierDocument2 pagesClarifierchagar_harshNo ratings yet

- Comparison of AdjectivesDocument2 pagesComparison of AdjectivesmallxNo ratings yet

- Camp ApplianceDocument1 pageCamp ApplianceflyzalNo ratings yet

- Equivalent Record Form: Department of Education MIMAROPA RegionDocument1 pageEquivalent Record Form: Department of Education MIMAROPA RegionEnerita AllegoNo ratings yet

- CANAVAN' and VESCOVI - 2004 - CMJ X SJ Evaluation of Power Prediction Equations Peak Vertical Jumping Power in WomenDocument6 pagesCANAVAN' and VESCOVI - 2004 - CMJ X SJ Evaluation of Power Prediction Equations Peak Vertical Jumping Power in WomenIsmenia HelenaNo ratings yet

- Impacts of DecarbonizationDocument2 pagesImpacts of DecarbonizationCM SoongNo ratings yet

- Lewis Carrol: Birth: DeathDocument21 pagesLewis Carrol: Birth: DeathmarialuvsjeffNo ratings yet

- English 2.2 FPT PolytechnicDocument10 pagesEnglish 2.2 FPT PolytechnicKieu Mai Trang (FPL HCM)0% (1)

- PublicReviewDraft2742 (1) (002)Document75 pagesPublicReviewDraft2742 (1) (002)dhruv.encontrolsNo ratings yet

- Linked ListDocument83 pagesLinked Listshahida18No ratings yet

- 2017 Grade 9 Math Challenge OralsDocument3 pages2017 Grade 9 Math Challenge OralsGracy Mae PanganibanNo ratings yet

- Din en 912-2001Document37 pagesDin en 912-2001Armenak BaghdasaryanNo ratings yet

- Eca Important QuestionsDocument3 pagesEca Important QuestionsSri KrishnaNo ratings yet

- Catalogue PDFDocument4 pagesCatalogue PDFShivam GuptaNo ratings yet

- Sri Lanka, CBSLDocument24 pagesSri Lanka, CBSLVyasIRMANo ratings yet

- Test 1 Grammar, Revised Ecpe HonorsDocument3 pagesTest 1 Grammar, Revised Ecpe HonorsAnna Chronopoulou100% (1)

- Communication & Collaboration: Lucy Borrego Leidy Hinojosa Scarlett DragustinovisDocument44 pagesCommunication & Collaboration: Lucy Borrego Leidy Hinojosa Scarlett DragustinovisTeacherlucy BorregoNo ratings yet

- Lect 1.2 Principles of Food Process DesignDocument43 pagesLect 1.2 Principles of Food Process Designmahmoud hassanNo ratings yet

- Assurance Audit of Prepaid ExpendituresDocument7 pagesAssurance Audit of Prepaid ExpendituresRatna Dwi YulintinaNo ratings yet

- Edtpa Lesson Plan 1Document3 pagesEdtpa Lesson Plan 1api-364684662No ratings yet

- New Wordpad DocumentDocument6 pagesNew Wordpad DocumentJonelle D'melloNo ratings yet

- Final Exam IN Sample QuestionsDocument27 pagesFinal Exam IN Sample QuestionsJI TEN100% (1)

- IELTS Writing Task 2/ IELTS EssayDocument2 pagesIELTS Writing Task 2/ IELTS EssayOlya HerasiyNo ratings yet

- Rigor Mortis and Lividity in Estimating Time of DeathDocument2 pagesRigor Mortis and Lividity in Estimating Time of DeathfunnyrokstarNo ratings yet