Professional Documents

Culture Documents

Spice Examples Orcad Winspice Fuller

Uploaded by

Mannan AbdulOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Spice Examples Orcad Winspice Fuller

Uploaded by

Mannan AbdulCopyright:

Available Formats

SPICE Examples

ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

SPICE Examples Using OrCAD PSPICE and WINSPICE

Dr. Lynn Fuller

Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Fax (585) 475-5041 Dr. Fullers Webpage: http://people.rit.edu/lffeee Email: Lynn.Fuller@rit.edu Dept Webpage: http://www.microe.rit.edu

Rochester Institute of Technology Microelectronic Engineering

3-20-2011 SPICE_Examples_OrCAD_WinSPICE_Fuller.ppt

Page 1

March 20, 2011 Dr. Lynn Fuller

SPICE Examples

OUTLINE

Introduction WinSpice OrCAD Pspice LT SPICE Simple Example Device Models Comparion of 1st, 2nd and 3rd Generation Models Family of Curves, Id-Vgs, Sub-Vt Verification of Resistor and Capacitor Values Ring Oscillator Gate Delay td Circuit Examples Inverter with Hysteresis RC Oscillator Two Phase Clock Op Amp Rochester Institute of Technology Diode Temperature Sensor Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 2

SPICE Examples

INTRODUCTION

SPICE (Simulation Program for Integrated Circuit Engineering) is a general-purpose circuit simulation program for non-linear DC, nonlinear transient, and linear AC analysis. Circuits may contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, transmission lines, switches, and several semiconductor devices: including diodes, BJTs, JFETs, MESFETs, and MOSFETs. Circuits with large numbers of all types of components can be simulated. SPICE input files and output files are simple text files (e.g. name.txt) Input files include a TITLE, circuit description NET LIST, analysis directives (COMMANDS), and lists of other text files to include (INC) such as model libraries (LIB) and an END command.

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 3

SPICE Examples

INTRODUCTION

PSpice Lite 9.2 is one of the OrCAD family of products, from Cadence Design Systems, Inc., offering a complete suite of electronic design tools. It is free and includes limited versions of OrCAD Capture, for schematic capture, PSpice for analog circuit simulation and Pspice A/D for mixed analog and digital circuit simulation. PSpice Lite 9.2 is limited to 64 nodes, 10 transistors, two operational amplifiers and 65 primitive digital devices. See page 35 (xxxv) of the PSpice Users Guide. LT SPICE is a free SPICE simulator with schematic capture from Linear Technology. It is quite similar to Pspice Lite but is not limited in the number of devices or nodes. Linear Technology (LT) is one of the industry leaders in analog and digital integrated circuits. Linear Technology provides a complete set of SPICE models for LT components. WINSPICE is a low cost fully capable SPICE simulator for windows computers. The full version is approximately $75. It does not include a schematic editor. (but is available from third party)

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 4

SPICE Examples

EXAMPLE OF SIMPLE SPICE INPUT FILE

DR FULLER - SIMPLE EXAMPLE TITLE * THE FIRST LINE IS THE TITLE * LINES THAT START WITH * ARE COMMENT LINES AND DO NOTHING * UPPER AND lower case text ARE TREATED THE SAME * CIRCUIT IS DESCRIBED BELOW (NET LIST) R1 1 0 2K ; resistor R1 between node 1 and zero has value 2000 ohms R2 2 1 3K V1 2 0 DC 5 ; Voltage source V1 is a DC source of 5 volts * * REQUESTED ANALYSIS (DIRECTIVES OR COMMANDS) .DC V1 0 5 .1 ; find all node voltages and branch currents for V1 starting at 0 and * incrementing by 0.1 volts ending at 5 volts .PLOT DC V(1) * *.INCLUDE File_name.txt ;(none for this example) * .END

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 5

SPICE Examples

CREATING THE INPUT FILE

The input file can be generated from a schematic capture program, or just typed in a text editor such as Notepad or WordPad Simple Resistor Divider R1 1 0 2K R2 2 1 3K V1 2 0 DC .DC V1 0 5 .1 .PLOT DC V(1) .END 2 5V V1

+ R1 2K

R2 3K

0

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 6

SPICE Examples

WINSPICE3

WinSpice3 is a general-purpose circuit simulation program for non-linear DC, nonlinear transient, and linear AC analyses. Circuits may contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, lossless and lossy transmission lines (two separate implementations), switches, uniform distributed RC lines, and the five most common semiconductor devices: diodes, BJTs, JFETs, MESFETs, and MOSFETs. It can be downloaded and installed onto personal computers at http://www.winspice.com . When the full version v1.05.01 is installed, it should be updated to v1.05.07, which is the latest version available for now. WinSpice basically Spice3F4 for Windows 32bit systems. However, it contains several enhancements over the original Berkeley Spice3F4. WinSpice iteself does not contain a schematic editor (capture/edit). However, 3rd part schematic editors can be linked to WinSpice. A schematic editor which uses WinSpice for its simulation engine is available at http://www.5spice.com/. These editors provide a convenient way to draw a schematic and create a net list.

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 7

SPICE Examples

RUNNING WINSPICE

Once WinSpice is installed click on your shortcut or start WinSpice from the start programs menu. A dialog box and WinSpice -> prompt should appear. Type source path_to_your_input_file.txt Press Enter SPICE will run

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 8

SPICE Examples

OrCAD PSpice Lite 9.2

PSpice Lite 9.2 is one of the OrCAD family of products offering a complete suite of electronic design tools. These products are available from Cadence Design Systems, Inc. PSpice Lite 9.2 includes limited versions of OrCAD Capture, for schematic capture, PSpice for analog circuit simulation and Pspice A/D for mixed analog and digital circuit simulation. PSpice Lite 9.2 is limited to 64 nodes, 10 transistors, two operational amplifiers and 65 primitive digital devices. See page 35 (xxxv) of the PSpice Users Guide.

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 9

SPICE Examples

BEFORE YOU START

It might be good to set up some folders for your SPICE projects

C:/SPICE Other Files

Models

I put a SPICE folder on my C:/ drive and created sub folders for projects, models and other files, etc.

Project1

Project N

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 10

SPICE Examples

START SCHEMATIC CAPTURE OrCAD PSpice Lite 9.2

Start >Programs>Orcad Family Release 9.2 Lite Edition>Capture Lite Edition

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 11

SPICE Examples

OPEN A NEW BLANK PROJECT OrCAD PSpice Lite 9.2 Select New>Project Give it a name Select Analog or Mixed A/D

Browse to the folder location you set up

Rochester Institute of Technology Microelectronic Engineering

Select create a blank project

Page 12

March 20, 2011 Dr. Lynn Fuller

SPICE Examples

CREATE SCHEMATIC OF THE CIRCUIT OrCAD PSpice Lite 9.2

Place Parts Place Wires Place Ground use 0/Source symbol Label Nodes Add Probes Change Names of Devices Change Device Properties Show Name and Value, etc.

Rochester Institute of Note: SPICE requires Technology to be labeled zero, either place a ground symbol labeled one node Microelectronic Engineering zero or use node label N1 icon alias = 0 (then you do not need a ground symbol) March 20, 2011 Dr. Lynn Fuller

Page 13

SPICE Examples

RC DIVIDER CIRCUIT

R1 20K

Calculate VC 3V

R2 10K

+

VC

Change the battery to a 3 volt step function and plot VC versus time. Change the battery to a sinusoidal voltage source and sketch VC versus frequency

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 14

SPICE Examples

DC SPICE ANALYSIS OrCAD PSpice Lite 9.2

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 15

SPICE Examples

TRANSIENT ANALYSIS OrCAD PSpice Lite 9.2

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 16

SPICE Examples

AC ANALYSIS OrCAD PSpice Lite 9.2

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 17

SPICE Examples

MOSFET, BJT AND DIODE MODELS

Orcad PSpice has many model libraries that can be included with a SPICE input file. You could also create your own models as a simple text file and include that file with a SPICE input file for either PSpice or WinSpice. In SPICE a transistor is defined by its name and associated properties and its model. Its name and associated properties is given in the input file net list. Its model is given in the included library or model file or pasted into the input file. For example:

* SPICE Input File M2 3 2 0 0 RITSUBN7 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 D1 5 6 RITMEMDIODE Q1 3 2 0 QRITNPN * *

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 18

SPICE Examples

MOSFET, BJT AND DIODE MODELS

* The Included Model File *2-15-2009 .MODEL RITSUBN7 NMOS (LEVEL=7 +VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=1.84E-7 NCH=1.45E17 NSUB=5.33E16 XT=8.66E-8 NSS=3E11 +VTH0=1.0 U0= 600 WINT=2.0E-7 LINT=1E-7 +NGATE=5E20 RSH=1082 JS=3.23E-8 JSW=3.23E-8 CJ=6.8E-4 MJ=0.5 PB=0.95 +CJSW=1.26E-10 MJSW=0.5 PBSW=0.95 PCLM=5 +CGSO=3.4E-10 CGDO=3.4E-10 CGBO=5.75E-10) * .model RITMEMDIODE D IS=3.02E-9 N=1 RS=207 +VJ=0.6 CJO=200e-12 M=0.5 BV=400 * .MODEL QRITNPN NPN (BF=416 IKF=.06678 ISE=6.734E-15 IS=6.734E-15 NE=1.259 +RC=1 RB=10 VA=109)

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 19

SPICE Examples

SIMULATION PROGRAM FOR INTEGRATED CIRCUIT ENGINEERING

MOSFET Device models used by SPICE (Simulation Program for Integrated Circuit Engineering) simulators can be divided into three classes: First Generation Models (Level 1, Level 2, Level 3 Models), Second Generation Models (BISM, HSPICE Level 28, BSIM2) and Third Generation Models (BSIM3, Level 7, Level 49, etc.) The newer generations can do a better job with short channel effects, local stress, transistors operating in the sub-threshold region, gate leakage (tunneling), noise calculations, temperature variations and the equations used are better with respect to convergence during circuit simulation.

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 20

SPICE Examples

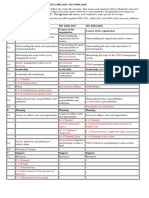

MOSFET SPICE MODEL LEVELS

1st Generation 2nd Generation 3rd Generation

note: PSpice does not recognize level 49, WinSpice does not recognize level 7

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 21

SPICE Examples

RIT MOSFET SPICE MODELS

*SPICE MODELS FOR RIT DEVICES - DR. LYNN FULLER 2-5-2010 *LOCATION DR.FULLER'S COMPUTER DESKTOP/SPICE/MODELS/FULLER_RIT_MOSFET_MODELS.txt *SEE: http://people.rit.edu/lffeee/CMOS.htm * *LIST OF DEVICES/MODELS INCLUDED IN THIS LIBRARY * * RITMEMDIODE DIODE MODEL FOR EMCR870 MEMS FABRICATION COURSE * RITPMOS7 LEVEL 7 MODEL FOR PMOSFET MADE IN RIT PMOS PROCESS * RITPMOS49 LEVEL 49 MODEL FOR PMOSFET MADE IN RIT PMOS PROCESS * RITSUBN1 LEVEL 1 MODEL FOR NMOSFET MADE IN RIT SUB-CMOS PROCESS * RITSUBP1 LEVEL 1 MODEL FOR PMOSFET MADE IN RIT SUB-CMOS PROCESS * RITSUBN3 LEVEL 3 MODEL FOR NMOSFET MADE IN RIT SUB-CMOS PROCESS * RITSUBP3 LEVEL 3 MODEL FOR PMOSFET MADE IN RIT SUB-CMOS PROCESS * RITSUBN7 LEVEL 7 MODEL FOR NMOSFET MADE IN RIT SUB-CMOS PROCESS * RITSUBP7 LEVEL 7 MODEL FOR PMOSFET MADE IN RIT SUB-CMOS PROCESS * RITSUBN49 LEVEL 49 MODEL FOR NMOSFET MADE IN RIT SUB-CMOS PROCESS * RITSUBP49 LEVEL 49 MODEL FOR PMOSFET MADE IN RIT SUB-CMOS PROCESS * CMOSN LEVEL 2 MODEL FOR NMOSFET ORBIT SEMICONDUCTOR * CMOSP LEVEL 2 MODEL FOR PMOSFET ORBIT SEMICONDUCTOR * EENMOS LEVEL=2 MODEL FOR NMOSFET USED IN EEEE481 ELECTRONICS I * QRITNPN BJT MODEL USED IN EMCR482 ELECTRONICS II * * note: Level 7 and Level 49 are the same except for two extra parameters in level 49 Rochester Institute of Technology * PSpice does not recognize level 49, WinSpice does not recognize level 7 Microelectronic Engineering *

March 20, 2011 Dr. Lynn Fuller

Page 22

SPICE Examples

LEVEL=1, RIT SUB-CMOS 150 PROCESS

* *2-15-2009 .MODEL RITSUBN1 NMOS (LEVEL=1 +VTO=1.0 LAMBDA= 0.031 PB=0.95 CGSO=3.4E-10 CGDO=3.4E-10 +CGBO=5.75E-10 RSH=1082 CJ=6.8e-4 MJ=0.5 CJSW=1.26e-10 +MJSW=0.5 JS=3.23e-8 TOX=150E-10 NSUB=1.45e17 NSS=3E11 +TPG=+1 XJ=0.18U LD=0.15U UO=363) * *2-15-2009 .MODEL RITSUBP1 PMOS (LEVEL=1 +VTO=-1.0 LAMBDA= 0.05 PB=0.94 CGSO=5.08E-10 CGDO=5.08E-10 +CGBO=5.75E-10 RSH=33.7 CJ=5.01e-4 MJ=0.5 CJSW=1.38e-10 +MJSW=0.5 JS=6.43e-8 TOX=150E-10 NSUB=7.23e16 NSS=1E11 +TPG=-1 XJ=0.28U LD=0.22U UO=463) *

*

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 23

SPICE Examples

LEVEL=3, RIT SUB-CMOS 150 PROCESS

* *1-15-2007 FROM DR. FULLER'S SPREAD SHEET .MODEL RITSUBN3 NMOS (LEVEL=3 TPG=1 TOX=1.5E-8 LD=2.95E-7 WD=3.00E-7 +UO= 263 VTO=0.5 THETA=0.046 RS=27 RD=27 DELTA=2.27 NSUB=1.45E17 +XJ=1.84E-7 VMAX=1.10E7 ETA=0.927 KAPPA=0.655 NFS=3E11 +CGSO=3.4E-10 CGDO=3.48E-10 CGBO=5.75E-10 XQC=0.4) * *1-17-2007 FROM DR. FULLER'S SPREAD SHEET .MODEL RITSUBP3 PMOS (LEVEL=3 TPG=-1 TOX=1.5E-8 LD=3.61E-7 WD=3E-7 +UO=275 VTO=-0.93 THETA=0.237 RS=33.7 RD=33.7 DELTA=2.35 NSUB=7.12E16 +XJ=2.26E-7 VMAX=7.02E6 ETA=0.897 KAPPA=4.481 NFS=3E11 +CGSO=4.15E-10 CGDO=4.15E-10 CGBO=5.75E-10 XQC=0.40) *

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 24

SPICE Examples

LEVEL=7, RIT SUB-CMOS 150 PROCESS

*1-15-2007 .MODEL RITSUBN7 NMOS (LEVEL=7 VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=1.84E-7 NCH=1.45E17 NSUB=5.33E16 XT=8.66E-8 NSS=3E11 +VTH0=1.0 U0= 650 WINT=2.0E-7 LINT=1.84E-7 +NGATE=5E20 RSH=1082 JS=3.23E-8 JSW=3.23E-8 CJ=6.8E-4 MJ=0.5 PB=0.95 +CJSW=1.26E-10 MJSW=0.5 PBSW=0.95 PCLM=5 +CGSO=3.4E-10 CGDO=3.4E-10 CGBO=5.75E-10) * *1-17-2007 .MODEL RITSUBP7 PMOS (LEVEL=7 VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=2.26E-7 NCH=7.12E16 NSUB=3.16E16 XT=8.66E-8 NSS=3E11 PCLM=5 +VTH0=-1.0 U0= 376.72 WINT=2.0E-7 LINT=2.26E-7 NGATE=5E20 +RSH=1347 JS=3.51E-8 JSW=3.51E-8 CJ=5.28E-4 MJ=0.5 PB=0.94 +CJSW=1.19E-10 MJSW=0.5 PBSW=0.94 +CGSO=4.5E-10 CGDO=4.5E-10 CGBO=5.75E-10) *

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 25

SPICE Examples

LEVEL=49, RIT SUB-CMOS 150 PROCESS

*1-15-2007 . .MODEL RITSUBN49 NMOS (LEVEL=49 +VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=1.84E-7 NCH=1.45E17 NSUB=5.33E16 XT=8.66E-8 NSS=3E11 +XWREF=2.0E-7 XLREF=2.95E-7 +VTH0=1.0 U0= 600 WINT=2.0E-7 LINT=1E-7 +NGATE=5E20 RSH=1082 JS=3.23E-8 JSW=3.23E-8 CJ=6.8E-4 MJ=0.5 PB=0.95 +CJSW=1.26E-10 MJSW=0.5 PBSW=0.95 PCLM=5 +CGSO=3.4E-10 CGDO=3.4E-10 CGBO=5.75E-10) *1-17-2007 .MODEL RITSUBP49 PMOS (LEVEL=49 +VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=2.26E-7 NCH=7.12E16 NSUB=3.16E16 XT=8.66E-8 NSS=3E11 PCLM=5 +XWREF= 2.0E-7 XLREF=3.61E-7 +VTH0=-1.0 U0= 376.72 WINT=2.0E-7 LINT=2.26E-7 NGATE=5E20 +RSH=1347 JS=3.51E-8 JSW=3.51E-8 CJ=5.28E-4 MJ=0.5 PB=0.94 +CJSW=1.19E-10 MJSW=0.5 PBSW=0.94 +CGS0=4.5E-10 CGD0=4.5E-10 CGB0=5.75E-10)

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 26

SPICE Examples

2.0 um MOSIS SCNA20 Process Level 2 Model

*3-23-2009 *From Dr. Pearson's VLSI Class *SPICE Level 2 Parameters for Supertex's (formerly Orbit Semiconductor's) *2.0um MOSIS SCNA20 Process (from N7CK production run) * .MODEL CMOSN NMOS LEVEL=2 PHI=0.7 TOX=4.08E-8 XJ=0.2 TPG=1 +VTO=0.8096 DELTA=4.586 LD=2.972E-7 KP=5.3532E-5 +UO=632.5 UEXP=0.1328 UCRIT=3.897E4 RSH=6.202 +GAMMA=0.5263 NSUB=5.977E15 NFS=5.925e11 VMAX=5.83E4 +LAMBDA=3.903E-2 CGDO=3.7731E-10 CGSO=3.7731E-10 +CGBO=3.4581E-10 CJ=1.3679E-4 MJ=0.63238 CJSW=5.1553E-10 +MJSW=0.26805 PB=0.4 *Weff=Wdrawn-Delta_W *The suggested Delta_W is 2.00E-9 * .MODEL CMOSP PMOS LEVEL=2 PHI=0.7 TOX=4.08E-8 XJ=0.2 TPG=-1 +VTO=-0.8483 DELTA=1.952 LD=3.431E-7 KP=1.779E-5 +UO=210.2 UEXP=0.4659 UCRIT=1.324E5 RSH=0.10960 +GAMMA=0.5263 NSUB=5.977E15 NFS=5.925e11 VMAX=5.83E4 +LAMBDA=6.372E-2 CGDO=4.3558E-10 CGSO=4.3558E-10 +CGBO=3.5957E-10 CJ=3.1646E-4 MJ=0.59954 CJSW=3.4394E-10 +MJSW=0.21153 PB=0.9 *Weff=Wdrawn-Delta_W *The suggested Delta_W is 5.72E-8 Rochester Institute of Technology

Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 27

SPICE Examples

RIT METAL GATE PMOS

*1-17-2010 .MODEL RITPMOS7 PMOS (LEVEL=7 VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=7.0E-8 XJ=2.76E-6 NCH=1.56E15 NSUB=1.56E15 XT=7.07E-7 NSS=3E11 PCLM=5 *+XWREF= -0.5E-6 XLREF=4.41E-6 +VTH0=-0.8 U0= 600 WINT=2.0E-7 LINT=2.26E-6 NGATE=5E20 +RSH=120 JS=3.35E-7 JSW=3.35E-7 CJ=1.8E-4 MJ=0.5 PB=0.88 +CJSW=4.97E-10 MJSW=0.5 PBSW=0.88 +CGS0=1.09E-10 CGD0=1.09E-10 CGB0=6.90E-10) * *1-17-2010 .MODEL RITPMOS49 PMOS (LEVEL=49 VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=7.0E-8 XJ=2.76E-6 NCH=1.56E15 NSUB=1.56E15 XT=7.07E-7 NSS=3E11 PCLM=5 +XWREF= -0.5E-6 XLREF=4.41E-6 +VTH0=-0.8 U0= 600 WINT=2.0E-7 LINT=2.26E-6 NGATE=5E20 +RSH=120 JS=3.35E-7 JSW=3.35E-7 CJ=1.8E-4 MJ=0.5 PB=0.88 +CJSW=4.97E-10 MJSW=0.5 PBSW=0.88 +CGS0=1.09E-10 CGD0=1.09E-10 CGB0=6.90E-10) *

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 28

SPICE Examples

OTHER DEVICE MODELS

*The following is the model for MbreakN .MODEL MbreskN NMOS (LEVEL = 1 VTO = 0 KP=20.000000E-06 GAMMA = 0 +LAMBDA = 0 IS = 10.000000E-15 JS = 0 PB = 0.8 PBSW = 0.8 +CJ = 0 CJSW = 0 CGSO = 0 CGDO = 0 CGBO = 0 +TOX = 0 XJ = 0 UCRIT= 10.000000E+03 DIOMOD=1 VFB=0 LETA=0 +WETA = 0 U0 = 0 TEMP= 0 VDD = 0 XPART = 0 ) PHI = 0.6

* * Diode Model from MEMS Fabrication EMCR870 .model RITMEMDIODE D IS=3.02E-9 N=1 RS=207 +VJ=0.6 CJO=200e-12 M=0.5 BV=400 * * From Electronics I EEEE481 .model EENMOS NMOS LEVEL=2 +VTO=0.7 KP=25E-6 LAMBDA=0.02 GAMMA=0.9 TOX=90E-9 NSUB=3.7E15 * * From Electronics II EEEE482 BJT Model .MODEL QRITNPN NPN (BF=416 IKF=.06678 ISE=6.734E-15 IS=6.734E-15 NE=1.259 RC=1 RB=10 VA=109)

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 29

SPICE Examples

IMPORTING THE INCLUDE FILES INTO LTSPICE

To Import the model file: 1. Copy down the previous slide into a txt file using Notepad/Wordpad 2. Save your model file as either a .txt file or a .inc file somewhere on your computer. 3. In LTSPICE, add a SPICE Directive. This can be done either by pressing the T button or clicking on the text button and selecting the radio button that says SPICE directive 4. Type in .inc in the textbox. 5. Click the OK button and place the directive somewhere on the circuit schematic. 6. Right-Click on the text you just placed and click the browse button. 7. Navigate to your saved model file, open it, and click the OK button again. Your models are now loaded into your circuit. To use the imported file, add the device, right click on its name (usually the nameInstitute of Technology and change it to the name used in the Rochester on bottom), included file Microelectronic Engineering (RITMEMDIODE for example)

March 20, 2011 Dr. Lynn Fuller

Page 30

SPICE Examples

SIMULATIONS USING 1st GENERATION MODELS

1st Generation - Level 1 Model

1st Generation - Level 2 Model

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 31

SPICE Examples

SIMULATIONS USING 3rd GENERATION MODELS

3rd Generation - Level 7 Model

Measured

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 32

SPICE Examples

MEASURED COMPARED TO SIMULATION

Level 7

Level 1

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 33

SPICE Examples

MEASURED Ids Vgs and gm

Measured Level = 1

gm Id-Vgs

gm

Level = 1

Level = 7

Id-Vgs

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 34

SPICE Examples

SIMULATION of Sub-Threshold Ids-Vgs Curve

Measured

Level = 1

Level = 7

Measured

Rochester Institute of Technology Microelectronic Engineering March 20, 2011 Dr. Lynn Fuller

Page 35

SPICE Examples

ALD1103

From Data Sheets From Simulation Given model on left with L=10u and W=1000u

Note: not a very good match. Increase L?

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 36

SPICE Examples

CONCLUSION FROM DC MODEL COMPARISON Third generation MOSFET models such as Level 7 for OrCAD PSPICE or Level 49 models for WinSpice give better results than any of the 1st or 2nd generation models. These models are different for different processes (such as RITs Sub-CMOS 150 or RITs Adv-CMOS 150 processes)

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 37

SPICE Examples

SIMULATION OF MOSFET IDS-VDS FAMILY

FAMILY OF CURVES FOR RIT SUB-CMOS NMOSFET, Dr. Lynn Fuller, 1-15-2007 *LINE ABOVE IS TITLE *START WIN SPICE AND ENTER LOCATION AND NAME OF INPUT FILE *THIS FILE IS FAMILYN.TXT *EXAMPLE: winspice> source c:/spice/familyn.txt *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW .INCLUDE E:\SPICE\WINSPICE\RIT_MICROE_MODELS.TXT *CIRCUIT DESCRIPTION *VOLTAGE SOURCES V1 1 0 DC 5 V2 2 0 DC 1 V3 3 0 DC 2 V4 4 0 DC 3 V5 5 0 DC 4 V6 6 0 DC 5 *TRANSISTORS M1 7 2 0 0 RITSUBN3 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M2 8 3 0 0 RITSUBN3 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M3 9 4 0 0 RITSUBN3 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M4 10 5 0 0 RITSUBN3 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M5 11 6 0 0 RITSUBN3 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 *CURRENT METERS (VOLTAGE SOURCES OF VALUE = ZERO) VD1 1 7 DC 0 VD2 1 8 DC 0 VD3 1 9 DC 0 VD4 1 10 DC 0 VD5 1 11 DC 0 *REQUESTED ANALYSIS .OP .DC V1 0 5 .1 .PRINT DC I(VD1) I(VD2) I(VD3) I(VD4) I(VD5) Rochester Institute of Technology .PLOT DC I(VD1) I(VD2) I(VD3) I(VD4) Engineering Microelectronic I(VD5) .END

March 20, 2011 Dr. Lynn Fuller

Page 38

SPICE Examples

ANOTHER WAY TO GET A FAMILY OF CURVES

nmos family of curves .incl Fuller_RIT_MOSFET_MODELS.txt * m1 2 1 0 0 cmosn W= 10u L= 5u vd 2 0 dc 5 vg 1 0 dc 5 ************************ ***dc sweep analysis**** .dc vd 0 5 10m vg 0 5 .5 ************************ .end

Vd = 0.1 + Vg=1

0 1

M1

+ -

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 39

SPICE Examples

SPICE SIMULATION OF MOSFET ID VS. VGS

IDS VS. VGS FOR RIT SUB-CMOS NMOSFET, Dr. Lynn Fuller, 1-15-2007 *LINE ABOVE IS TITLE * *START WIN SPICE AND ENTER LOCATION AND NAME OF INPUT FILE *THIS FILE IS ID-VD-N.TXT *EXAMPLE: winspice> source c:/spice/ID-VD-N.txt * *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW .INCLUDE E:\SPICE\WINSPICE\RIT_MICROE_MODELS.TXT * *CIRCUIT DESCRIPTION * *VOLTAGE SOURCES V1 1 0 DC 0.1 V2 2 0 DC 1 * *TRANSISTORS M1 7 2 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 * 1 *CURRENT METERS (VOLTAGE SOURCES OF VALUE = ZERO) * VD1 1 7 DC 0 * VD1=0 + *REQUESTED ANALYSIS * .OP 7 .DC V2 0 5 .025 .PRINT DC I(VD1) V1 = 0.1 .PLOT DC I(VD1) DERIV(I(VD1)) M1 2 + .END

Rochester Institute of Technology Microelectronic Engineering

+ V2=1 0

March 20, 2011 Dr. Lynn Fuller

Page 40

SPICE Examples

NMOS INVERTER WITH RESISTER LOAD

INVERTER USING RESISTOR LOAD FOR RIT SUB-CMOS NMOSFET, Dr. Lynn Fuller, 1-15-2007 1 *LINE ABOVE IS TITLE * *START WIN SPICE AND ENTER LOCATION AND NAME OF INPUT FILE R=10K *THIS FILE IS INVERTER.TXT *EXAMPLE: winspice> source c:/spice/INVERTER.txt * V1 7 *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW 0to-5 .INCLUDE E:\SPICE\WINSPICE\RIT_MICROE_MODELS.TXT M1 + 2 * *VOLTAGE SOURCES + * V2=1 V1 1 0 DC 5 0 V2 2 0 DC 1 * *TRANSISTORS M1 7 2 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 +ps=44e-6 nrd=0.025 nrs=0.025 * *RESISTORS R1 1 7 10000 * *REQUESTED ANALYSIS .OP .DC V2 0 5 .1 Rochester Institute of Technology .PLOT DC V(7) Microelectronic Engineering .END

March 20, 2011 Dr. Lynn Fuller

Page 41

SPICE Examples

PMOS INVERTER WITH PMOS LOAD

INVERTER USING RIT PMOSFET, Dr. Lynn Fuller, 2-11-2007 *LINE ABOVE IS TITLE * *START WIN SPICE AND ENTER LOCATION AND NAME OF INPUT FILE *THIS FILE IS PMOS_INVERTER.TXT *EXAMPLE: winspice> source c:/spice/PMOS_INVERTER.txt * *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW .INCLUDE E:\SPICE\WINSPICE\RIT_MICROE_MODELS.TXT * *CIRCUIT DESCRIPTION * *VOLTAGE SOURCES V1 1 0 DC -10 V2 2 0 DC 0 * *TRANSISTORS Gain=1 M1 7 2 0 0 RITPMOS49 L=20U W=60U M2 1 1 7 0 RITPMOS49 L=60U W=20U * *REQUESTED ANALYSIS .OP .DC V2 0 -10 -0.1 Gain=2 .PLOT DC V(7) * Rochester Institute of Technology .END Microelectronic Engineering

Wd/Ld 0.5 Gain = Wu/Lu M2 Wu/Lu 7 M1 Wd/Ld

V1=-10 2 + V2=0 + to -10 -

Gain=3

March 20, 2011 Dr. Lynn Fuller

Page 42

SPICE Examples

CMOS THEORETICAL INVERTER VOUT VS VIN

VOUT

+V

VIN +V VOUT Idd Slope = Gain VIN VO Imax Voh

Idd

VoL CMOS VIN

0 0

ViL Vih Vinv

+V

margin=ViL-VoL 0 noiseInstitute of Technology Rochester Microelectronic Engineering 1 noise margin=VoH-ViH

March 20, 2011 Dr. Lynn Fuller

Page 43

SPICE Examples

INVERTER LAYOUT WITH PADS

INV/NOR4

W = 40 m Ldrawn = 2.5m Lpoly = 1.5m Rochester Institute of Technology Microelectronic Engineering Leff = 1.0 m

March 20, 2011 Dr. Lynn Fuller

Page 44

SPICE Examples

DC SIMULATION OF INVERTER VOUT & I VS VIN

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 45

SPICE Examples

MEASURED CMOS INVERTER VOUT & I VS VIN

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 46

SPICE Examples

RING OSCILLATOR, td, THEORY

Seven stage ring oscillator with two output buffers td = T / 2 N td = gate delay N = number of stages T = period of oscillation

Vout

Buffer

Vout

T = period of oscillation

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 47

SPICE Examples

MEASURED RING OSCILLATOR OUTPUT

73 Stage Ring at 5V

Rochester Institute of Technology Microelectronic Engineering

td = 104.8ns / 2(73) = 0.718 ns

March 20, 2011 Dr. Lynn Fuller

Page 48

SPICE Examples

SPICE LEVEL-1 MOSFET MODEL

G CGSO S COX CGDO D

p+ RS CBS CGBO ID RD

p+ CBD

B

Rochester Institute of Technology Microelectronic Engineering

where ID is a dependent current source using simple long channel equations.

Page 49

March 20, 2011 Dr. Lynn Fuller

SPICE Examples

AC MODEL FOR MOSFETS

The parameters that effect the AC response of a MOSFET are the resistance and capacitance values. RS,RS RSH CGSO,CGDO CGBO CJ CJSW MJ MJSW Source/Drain Series Resistance, ohms Sheet Resistance of Drain/Source, ohms Zero Bias Gate-Source/Drain Capacitance, F/m of width Zero Bias Gate-Substrate Capacitance, F/m of length DS Bottom Junction Capacitance, F/m2 DS Side Wall Junction Capacitance, F/m of perimeter Junction Grading Coefficient, 0.5 Side Wall Grading Coefficient, 0.5

These are combined with the transistors L, W Length and Width AS,AD Area of the Source/Drain PS,PD Perimeter of the Source/Drain NRS,NRD Number of squares Contact to Channel

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 50

SPICE Examples

RING OSCILLATOR LAYOUTS

17 Stage Un-buffered Output L/W=2/30 Buffered Output

L/W 8/16

4/16

2/16

73 Stage

37 Stage

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 51

SPICE Examples

MOSFETS IN THE INVERTER OF 73 RING OSCILLATOR nmosfet pmosfet

73 Stage Ring Oscillator

Rochester Institute of Technology Microelectronic Engineering March 20, 2011 Dr. Lynn Fuller

Page 52

SPICE Examples

FIND DIMENSIONS OF THE TRANSISTORS

NMOS L W AD AS PD PS NRS NRD 2u 12u 12ux12u=144p 12ux12u=144p 2x(12u+12u)=48u 2x(12u+12u)=48u 1 1 PMOS 2u 30u 12ux30u=360p 12ux30u=360p 2x(12u+30u)=84u 2x(12u+30u)=84u 0.3 0.3

73 Stage

Use Ctrl Click on all NMOS on OrCad Schematic Use Ctrl Click on all PMOS on OrCad Schematic Rochester Institute of Technology Microelectronic Engineering Then Enter Dimensions

March 20, 2011 Dr. Lynn Fuller

Page 53

SPICE Examples

LEVEL = 7

*2-15-2009 .MODEL RITSUBN7 NMOS (LEVEL=7 +VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=1.84E-7 NCH=1.45E17 NSUB=5.33E16 XT=8.66E-8 NSS=3E11 +VTH0=1.0 U0= 600 WINT=2.0E-7 LINT=1E-7 +NGATE=5E20 RSH=50 JS=3.23E-8 JSW=3.23E-8 CJ=6.8E-4 MJ=0.5 PB=0.95 +CJSW=1.26E-10 MJSW=0.5 PBSW=0.95 PCLM=5 +CGSO=3.4E-10 CGDO=3.4E-10 CGBO=5.75E-10) * *2-17-2009 .MODEL RITSUBP7 PMOS (LEVEL=7 +VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=2.26E-7 NCH=7.12E16 NSUB=3.16E16 XT=8.66E-8 NSS=3E11 PCLM=5 +VTH0=-1.0 U0= 376.72 WINT=2.0E-7 LINT=2.26E-7 NGATE=5E20 +RSH=50 JS=3.51E-8 JSW=3.51E-8 CJ=5.28E-4 MJ=0.5 PB=0.94 +CJSW=1.19E-10 MJSW=0.5 PBSW=0.94 +CGSO=4.5E-10 CGDO=4.5E-10 CGBO=5.75E-10)

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 54

SPICE Examples

SIMULATED OUTPUT AT 10 VOLTS

Three Stage Ring Oscillator with Transistor Parameters for 73 Stage Ring Oscillator and Supply of 10 volts

Rochester Institute of Technology Microelectronic Engineering

td = T / 2N = 3.5nsec / 2 / 3 td = 0.583 nsec

Page 55

March 20, 2011 Dr. Lynn Fuller

SPICE Examples

SIMULATED OUTPUT AT 5 VOLTS

Three Stage Ring Oscillator with Transistor Parameters for 73 Stage Ring Oscillator and Supply of 5 volts

Rochester Institute of Technology Measured td = 0.718 nsec @ 5 V Microelectronic Engineering

td = T / 2N = 5.5nsec / 2 / 3 td = 0.92 nsec

Page 56

March 20, 2011 Dr. Lynn Fuller

SPICE Examples

CONCLUSION

Since the measured and the simulated gate delays, td are close to correct, then the SPICE model must be close to correct. The inverter gate delay depends on the values of the internal capacitors and resistances of the transistor. Specifically: RS, RS, RSH CGSO, CGDO, CGBO CJ, CJSW These are combined with the transistors L, W Length and Width AS,AD Area of the Source/Drain PS,PD Perimeter of the Source/Drain NRS,NRD Number of squares Contact to Channel

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 57

SPICE Examples

INVERTER WITH HYSTERESIS

INVERTER WITH HYSTERESIS USING FOR RIT SUB-CMOS NMOSFET, Dr. Lynn Fuller, 1-15-2007 1 *LINE ABOVE IS TITLE * *START WIN SPICE AND ENTER LOCATION AND NAME OF INPUT FILE R=10K *THIS FILE IS HYSTERESIS.TXT Vout *EXAMPLE: winspice> source c:/spice/Hysteresis.txt 3 * M2 + V1 5V *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW M3 .INCLUDE E:\SPICE\WINSPICE\RIT_MICROE_MODELS.TXT 2 * 7 *VOLTAGE SOURCES V2=0-5 + V1 1 0 DC 5 M1 Or 5-0 V2 2 0 DC 0 * *TRANSISTORS M1 7 2 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M2 3 2 7 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M3 1 3 7 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 * Sweep Vin 5 to 0V Sweep Vin 0 to 5V *RESISTORS R1 1 3 10000 * *REQUESTED ANALYSIS .OP .DC V2 5 0 -.1 *.DC V2 0 5 .1 Rochester Institute of Technology .PLOT DC V(3) Microelectronic Engineering .END

March 20, 2011 Dr. Lynn Fuller

Page 58

SPICE Examples

REPLACE RESISTOR WITH LONG MOSFET

1 M4 Vout M2 M3 2 V2=0-5 + Or 5-0 7 M1

3 + V1 - 5V

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 59

SPICE Examples

RC OSCILLATOR USING INVERTER WITH HYSTERESIS

1 M4 R1 + M2 V1 5V 2 C1 7 M3 M1 M6 M8 3 4 5 Vout M5 M7

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 60

SPICE Examples

SPICE INPUT FILE FOR RC OSCILLATOR

INVERTER WITH HYSTERESIS USING FOR RIT SUB-CMOS NMOSFET, Dr. Lynn Fuller, 1-15-2007 *START WIN SPICE AND ENTER LOCATION AND NAME OF INPUT FILE *THIS FILE IS ID-VD-N.TXT *EXAMPLE: winspice> source c:/spice/Hysteresis.txt * *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW .INCLUDE G:\SPICE\WINSPICE\RIT_MICROE_MODELS.TXT * *VOLTAGE SOURCES V1 1 0 DC 6 *TRANSISTORS M1 7 2 0 0 RITSUBN49 L=2U W=64U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M2 3 2 7 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M3 1 3 7 0 RITSUBN49 L=2U W=64U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M6 4 3 0 0 RITSUBN49 L=2U W=64U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M8 5 4 0 0 RITSUBN49 L=2U W=128U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 * *RESISTOR AND CAPACITOR R1 3 2 100000 C1 2 0 50E-12 * *Replace load for inverters with long transistor with gate tied up to drain M4 1 1 3 0 RITSUBN49 L=32U W=4U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M5 1 1 4 0 RITSUBN49 L=64U W=8U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M7 1 1 5 0 RITSUBN49 L=64U W=8U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 *REQUESTED ANALYSIS .IC V(2) 0 Rochester .TRAN 1US 50US Institute of Technology Microelectronic v(5) V(7) .PLOT TRAN V(3) V(2)Engineering v(4) .END

March 20, 2011 Dr. Lynn Fuller

Page 61

SPICE Examples

OUTPUT FOR RC OSCILLATOR

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 62

SPICE Examples

ALL NMOS TRANSISTOR VERSION

1 M4 3 M7 + V1 9V C1 2 7 M3 M1 M6 M8 M2 4 M5

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 63

SPICE Examples

ALL TRANSISTOR VERSION

RC Oscillator, INVERTER WITH HYSTERESIS USING FOR RIT SUB-CMOS NMOSFET, Dr. Lynn Fuller, 1-25-2007 *START WIN SPICE AND ENTER LOCATION AND NAME OF INPUT FILE *THIS FILE IS RC2_OSCILLATOR.TXT * *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW .INCLUDE E:\SPICE\WINSPICE\RIT_MICROE_MODELS.TXT * *VOLTAGE SOURCES V1 1 0 DC 9 * *TRANSISTORS M1 7 2 0 0 RITSUBN49 L=2U W=64U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M2 3 2 7 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M3 1 3 7 0 RITSUBN49 L=2U W=64U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M4 1 1 3 0 RITSUBN49 L=32U W=8U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M5 1 1 4 0 RITSUBN49 L=64U W=8U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M6 4 3 0 0 RITSUBN49 L=2U W=128U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M7 3 3 2 0 RITSUBN49 L=128U W=4U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 M8 3 2 2 0 RITSUBN49 L=64U W=4U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=0.025 nrs=0.025 * *CAPACITOR C1 2 0 30E-12 * *REQUESTED ANALYSIS .IC V(2) 0 Rochester .TRAN 5US 400US Institute of Technology Microelectronic Engineering .PLOT TRAN V(3) V(2) V(7) v(4) .END

March 20, 2011 Dr. Lynn Fuller

Page 64

SPICE Examples

RC OSCILLATOR

30 pF 90 pF

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 65

SPICE Examples

TWO-PHASE CLOCK GENERATORS

A 0 0 1 1 B 0 1 0 1 C 1 0 0 0

CLOCK t1 CLOCKBAR

t2 Q

1 2

R 0 0 1 1

S 0 1 0 1

Q Qn-1 1 0

INDETERMINATE

t3

CLOCK CLOCK BAR t1

t1 t2 t3 t3

1 2

Rochester Institute of Technology Microelectronic Engineering

=

Page 66

March 20, 2011 Dr. Lynn Fuller

SPICE Examples

TWO PHASE CLOCK VERSION ONE

1 8 VOUT1 + V1 5V 2 + V2 CLOCK M11 10 M13 M15 11 M17 9 VOUT2

M12 M1 M3 3 M2 M4

M14 M5 4 M6

M16 M7 5 M8 6

M18 M9 7

M10

0

Rochester Institute of Technology Microelectronic Engineering

Substrate of all NMOS go to ground, node 0 Substrate of all PMOS go to +5V, node 1

March 20, 2011 Dr. Lynn Fuller

Page 67

SPICE Examples

WINSPICE INPUT FILE

TWO PHASE CLOCK USING RIT SUB-CMOS MOSFETS, Dr. Lynn Fuller, 4-3-2009 *LINE ABOVE IS TITLE * *START WIN SPICE AND ENTER> SOURCE "LOCATION AND NAME OF INPUT FILE" *THIS FILE IS TWOPHASECLOCK1.TXT *EXAMPLE: winspice> source c:/spice/ID-VD-N.txt * *THE TRANSISTOR MODELS ARE IN THE FILE NAMED BELOW .INCLUDE c:\Documents and Settings\lffeee\Desktop\SPICE\WINSPICE_Examples\RIT_PSPICE_MODELS.TXT * *CIRCUIT DESCRIPTION *VOLTAGE SOURCES V1 1 0 DC 5 V2 2 0 PULSE (0 5 0 1NS 1NS 10NS 20NS) * *PMOS M1 1 2 3 1 RITSUBP49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M3 1 3 4 1 RITSUBP49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M5 1 4 5 1 RITSUBP49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M7 1 5 6 Rochester Institute ofL=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 1 RITSUBP40 Technology M9 1 6 7 Microelectronic Engineering W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 1 RITSUBP49 L=2U

March 20, 2011 Dr. Lynn Fuller

Page 68

SPICE Examples

WINSPICE INPUT FILE

M11 10 2 8 1 RITSUBP49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M13 1 9 10 1 RITSUBP49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M15 11 8 9 1 RITSUBP49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M17 1 9 11 1 RITSUBP49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 * *NMOS M2 3 2 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M4 4 3 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M6 5 4 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M8 6 5 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M10 7 6 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M12 8 2 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M14 8 9 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M16 9 8 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 M18 9 7 0 0 RITSUBN49 L=2U W=16U ad=96e-12 as=96e-12 pd=44e-6 ps=44e-6 nrd=1.0 nrs=1.0 * *REQUESTED ANALYSIS .OP .TRAN 1N 100N .PLOT TRAN V(8) V(9) V(2) .END

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 69

SPICE Examples

WINSPICE SIMULATION

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 70

SPICE Examples

TWO PHASE NON OVERLAPPING CLOCK Clock

1 2

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 71

SPICE Examples

VERSION 2 OF TWO PHASE NON OVERLAPPING CLOCK

CLOCK t1 CLOCKBAR

1 VOUT1 8 M11 10 M13 M5 3 M12 M14 M4 M6 4 M16 M18 M15 11

t2

1

t3

2

M17 9 VOUT2

M3

M9 2 + V2 CLOCK Rochester Institute of Technology + Microelectronic Engineering

M7

M1 7 M2 Page 72

V1 5V

5 M10 M8

0

March 20, 2011 Dr. Lynn Fuller

SPICE Examples

WINSPICE SIMULATION FOR VERSION TWO

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 73

SPICE Examples

WINSPICE SIMULATION FOR VERSION TWO + BUFFERS

CLOCK t1 CLOCKBAR S t3 R t2

1 2

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 74

SPICE Examples

BASIC TWO STAGE OPERATIONAL AMPLIFIER

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 75

SPICE Examples

SPICE ANALYSIS OF OP AMP VERSION 2

.incl rit_sub_param.txt m1 8 9 7 6 cmosn w=9u l=5u nrd=1 nrs=1 ad=45p pd=28u as=45p ps=28u m2 1 10 7 6 cmosn w=9u l=5u nrd=1 nrs=1 ad=45p pd=28u as=45p ps=28u m3 8 8 4 4 cmosp w=21u l=5u nrd=1 nrs=1 ad=102p pd=50u as=102p ps=50u m4 1 8 4 4 cmosp w=21u l=5u nrd=1 nrs=1 ad=102p pd=50u as=102p ps=50u m5 7 5 6 6 cmosn w=40u l=5u nrd=1 nrs=1 ad=205p pd=90u as=205p ps=90u m6 2 1 4 4 cmosp w=190u l=5u nrd=1 nrs=1 ad=950p pd=400u as=950p ps=400u m7 2 5 6 6 cmosn w=190u l=5u nrd=1 nrs=1 ad=950p pd=400u as=950p ps=400u m8 5 5 6 6 cmosn w=40u l=5u nrd=1 nrs=1 ad=205p pd=90u as=205p ps=90u vdd 4 0 3 vss 6 0 -3 cprobe 2 0 30p Rprobe 2 0 1meg cc 1 2 0.6p mr1 20 20 4 4 cmosp w=6u l=10u nrd=1 nrs=1 ad=200p pd=60u as=200p ps=60u mr2 5 5 20 4 cmosp w=6u l=10u nrd=1 nrs=1 ad=200p pd=60u as=200p ps=60u *************** ************* ***dc open loop gain********* vi1 9 0 0 13.5kV/V gain vi2 10 0 0 *.dc vi2 -0.002 0.002 1u .dc vi2 -1 1 0.1m *****open loop frequency characteristics***** *vi1 9 0 0 *vi2 10 0 dc 0 ac 1u Rochester Institute of Technology *.ac dec 100 10 1g Microelectronic Engineering .end

March 20, 2011 Dr. Lynn Fuller

Page 76

SPICE Examples

SIGNAL CONDITIONING FOR TEMPERATURE SENSOR

R1 20K

p

3.3V

+

0.2 < Vout < 0.7V

Gnd

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 77

SPICE Examples

REFERENCES

1. 2. 3. 4. 5. 6. 7. 8. MOSFET Modeling with SPICE, Daniel Foty, 1997, Prentice Hall, ISBN-0-13-227935-5 Operation and Modeling of the MOS Transistor, 2nd Edition, Yannis Tsividis, 1999, McGraw-Hill, ISBN-0-07-065523-5 UTMOST III Modeling Manual-Vol.1. Ch. 5. From Silvaco International. ATHENA USERS Manual, From Silvaco International. ATLAS USERS Manual, From Silvaco International. Device Electronics for Integrated Circuits, Richard Muller and Theodore Kamins, with Mansun Chan, 3rd Edition, John Wiley, 2003, ISBN 0-471-59398-2 ICCAP Manual, Hewlet Packard PSpice Users Guide.

Rochester Institute of Technology Microelectronic Engineering

March 20, 2011 Dr. Lynn Fuller

Page 78

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Introduction To Control Systems:ObjectivesDocument34 pagesIntroduction To Control Systems:ObjectivesMannan AbdulNo ratings yet

- Advertisement 17 2015Document9 pagesAdvertisement 17 2015Mannan AbdulNo ratings yet

- B.ed Prospectus 2012Document9 pagesB.ed Prospectus 2012Mannan AbdulNo ratings yet

- Clipper ClamperDocument6 pagesClipper ClamperMannan AbdulNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Business Analyst JobDocument9 pagesBusiness Analyst JobEdmond KeraNo ratings yet

- S1200CPU LAxesGrpCtrl DOC v11 enDocument62 pagesS1200CPU LAxesGrpCtrl DOC v11 enDavid JimenezNo ratings yet

- Theories & Practices in Local GovernanceDocument21 pagesTheories & Practices in Local GovernanceLindsey MarieNo ratings yet

- Content:: 2. Components of Real Time Operating SystemDocument8 pagesContent:: 2. Components of Real Time Operating SystemKing amarNo ratings yet

- Pre-Feasibility Study: A M I N G O N EDocument25 pagesPre-Feasibility Study: A M I N G O N ESULTANMEHBOOB0% (1)

- Mphasis Data 10.4.19Document5 pagesMphasis Data 10.4.19Vyshnavi ThottempudiNo ratings yet

- 2G Flexi EdgeDocument137 pages2G Flexi EdgeBaleanu SilviuNo ratings yet

- Mamoolat e YoumiaDocument49 pagesMamoolat e YoumiaSheraz Ali RajNo ratings yet

- A Benchmark of Dual Constellations GNSS Solutions For Vehicle Localization in Container TerminalsDocument7 pagesA Benchmark of Dual Constellations GNSS Solutions For Vehicle Localization in Container TerminalsjfrasconNo ratings yet

- Games That Pushed The LimitsDocument25 pagesGames That Pushed The LimitsbigeazyeNo ratings yet

- What Are The Three Ways That Computer Buses Can Be Used To Communicate With Memory and I/O?Document1 pageWhat Are The Three Ways That Computer Buses Can Be Used To Communicate With Memory and I/O?Safa MNo ratings yet

- Control Engineering - IntroductionDocument26 pagesControl Engineering - IntroductionNithin GowdaNo ratings yet

- DSD ImpDocument3 pagesDSD Impvenkiscribd444No ratings yet

- 1.8 Introduction To Networks - Network SecurityDocument3 pages1.8 Introduction To Networks - Network SecurityCristian MoralesNo ratings yet

- Ip Profiling SytemDocument72 pagesIp Profiling Sytemjohnraymart colasitoNo ratings yet

- FLAC2 DDocument180 pagesFLAC2 DMohamed A. El-BadawiNo ratings yet

- Operating Instructions Converter 801Document26 pagesOperating Instructions Converter 801Vu Duc TuNo ratings yet

- Manual Casio PCR-T48sDocument2 pagesManual Casio PCR-T48sJOSE MENDOZANo ratings yet

- Serial Number Word 2010Document1 pageSerial Number Word 2010Akhmad Yusuf SulaimanNo ratings yet

- 4hana 1909Document60 pages4hana 1909ddharNo ratings yet

- CyberPower OLS6000-10000ERT6U User ManualDocument42 pagesCyberPower OLS6000-10000ERT6U User ManualKhách Sạn Hoàng Phố100% (2)

- Spectra System PumpsDocument2 pagesSpectra System PumpsAna JurkeviciuteNo ratings yet

- Fuzzy Self Tuning of PID ControllersDocument10 pagesFuzzy Self Tuning of PID ControllersSeveriano Jaramillo QuintanarNo ratings yet

- Annex SL 9001 14001 45001 Management System MapDocument3 pagesAnnex SL 9001 14001 45001 Management System MapPramod AthiyarathuNo ratings yet

- Military Briefing W3S0005 Student HandoutDocument14 pagesMilitary Briefing W3S0005 Student HandoutorcaNo ratings yet

- Epicor University - Advanced Business Process Management Course PDFDocument54 pagesEpicor University - Advanced Business Process Management Course PDFgvdaniel stpNo ratings yet

- How To Use 6211Document23 pagesHow To Use 6211ahmed4665No ratings yet

- Graphs: Shortest Paths, Job Scheduling Problem, Huffman CodeDocument25 pagesGraphs: Shortest Paths, Job Scheduling Problem, Huffman CodeVikalp Panseriya100% (1)

- PKDocument6 pagesPKJoamoc More CervantesNo ratings yet

- Chapter 3 CPU Schedulling (Lect)Document45 pagesChapter 3 CPU Schedulling (Lect)Nasis DerejeNo ratings yet