Professional Documents

Culture Documents

DELL Inspiron N4020

Uploaded by

Deddy SuyantoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DELL Inspiron N4020

Uploaded by

Deddy SuyantoCopyright:

Available Formats

5

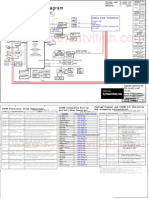

DJ1 Montevina UMA Schematics Document uFCPGA Mobile Penryn

C

Intel GM45+ICH9M 2010-02-10 REV : A00

DY : Nopop Component

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size A3 Date:

5 4 3 2

Document Number

Cover Page

Sheet

1

Rev

DJ1 Montevina UMA

W ednesday, February 24, 2010 1 of 88

A00

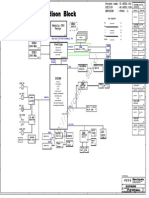

DJ1 Montevina UMA Block Diagram

D

CPU DC/DC

TPS51620

INPUTS

+PWR_SRC

47

Clock Generator SLG8SP513VTR

7

Intel Mobile CPU Penryn Socket P

8,9

Project code : 91.4EK01.001 PCB P/N : 48.4EK06.0SA Revision : 09275-SA

OUTPUTS

+VCC_CORE

SYSTEM DC/DC

TPS51218

INPUTS

+PWR_SRC

49

D

OUTPUTS

+1.05V_VCCP

SYSTEM DC/DC

TPS51125

46

FSB 800/1066MHz

INPUTS

+PWR_SRC

OUTPUTS

+5V_ALW2 +3.3V_RTC_LDO +5V_ALW +3.3V_ALW +15V_ALW

CRT

55

RGB CRT

Intel GM45

AGTL + CPU I/F DDR Memory I/F External Graphics

10,11,12,13,14,15

DDRIII 800/1066 Channel A

DDRIII 800/1066 DDRIII 800/1066

Slot 0

18

SYSTEM DC/DC

TPS51116

INPUTS OUTPUTS

+1.5V_SUS +0.75V_DDR_VTT +V_DDR_REF +PWR_SRC

50

DDRIII 800/1066 Channel B

Slot 1

19

LCD

C

54

LVDS(Dual Channel)

MAXIM CHARGER

BQ24745

INPUTS OUTPUTS

+PWR_SRC

C

DMIx4

C-LINK

10/100 NIC

Atheros AR8132

+DC_IN +PBATT

RJ45 CONN

26

SYSTEM DC/DC

Switches

42

I/O Board Connector

Intel ICH9-M

CardReader

SD/MMC/MS/ MS Pro/xD

70

SATA

PCIE x 2

26

Mini-Card

802.11a/b/g

INPUTS

+1.5V_SUS +5V_ALW +3.3V_ALW

OUTPUTS

+1.5V_RUN +5V_RUN +3.3V_RUN

PCIE USB2.0 USB 2.0/1.1 ports (12) PCI Express ports (8) High Definition Audio SATA ports (4) LPC I/F USB 2.0

USB 2.0 x 1

Realtek RTS5138

32

Left Side: USB x 1

75

PCB LAYER

L1: Top L2: VCC

USB 2.0 x 1

CAMERA

L3: Signal

54

ACPI 1.1

L4: Signal

USB 2.0 x 1

MIC IN

60

Internal Analog MIC

60

Azalia CODEC

IDT 92HD79B1

30

AZALIA

PCI/PCI BRIDGE

Bluetooth

L5: GND

72

L6: Bottom

20,21,22,23

LPC Bus

USB 2.0 x 2

HP1

60

Right Side: USB x 2

63

KBC

SPI

SATA

SATA

NUVOTON

NPCE781BA0DX

37

2CH SPEAKER HDD

59 60

DJ1

ODD

59

Flash ROM 2MB 62

Touch PAD

67

Int. KB

67

Thermal

EMC2102

39 25 Title Size A3 Date: Document Number

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Rev

Fan 58

5 4 3 2

DJ1 Montevina UMA

W ednesday, February 24, 2010 Sheet

1

A00

of 88

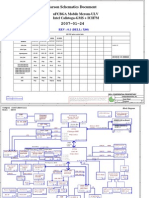

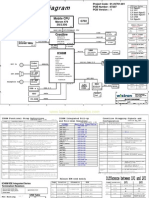

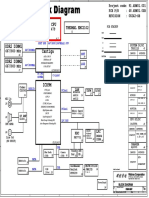

DJ1 Montevina UMA Power Block Diagram

D D

Adapter

+PWR_SRC TPS51125 Charger BQ24745

+VCC_CORE 47 +1.05V_VCCP 49

+V_DDR_REF +0.75V_DDR_VTT

TPS51620

TPS51218

TPS51116

Battery

C

+VCHGR

50

50

+1.5V_SUS 50

FSD8880

+15V_ALW

46

+3.3V_RTC_LDO 46

+5V_ALW2

46

+5V_ALW

46

+3.3V_ALW

46

+1.5V_RUN 42

G547F2P81U

SI4800

G547F2P81U

FDS8880

PA102

+5V_USB1 63

B

+5V_RUN 42

+5V_USB2 63

+3.3V_RUN 42

+3.3V_LAN

B

G9091 G5285T11U

+3.3V_CRT_LDO 15 +LCDVDD 54

+3.3V_RUN_CARD +1.8V_NB_S0

RTS5159

RT9198

RTL8103T

+1.2V_LOM

32

15

Power Shape

Regulator LDO Switch

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size A3 Date:

5 4 3 2

Document Number

Power Block Diagram

Sheet

1

Rev

DJ1 Montevina UMA

W ednesday, February 24, 2010 3 of 88

A00

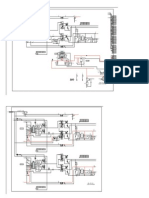

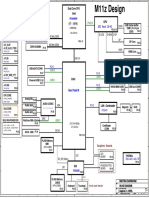

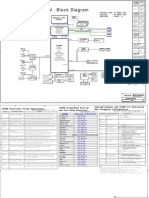

ICH SMBus Block Diagram

+3.3V_ALW +3.3V_RUN +3.3V_RUN SRN4K7J-8-GP

KBC SMBus Block Diagram

+5V_RUN

SRN4K7J-8-GP

ICH

1

DIMM 1

ICH_SMBCLK ICH_SMBDATA SCL SDA PSDAT1 PSCLK1 TPDATA TPCLK +KBC_PWR

SMBCLK SMBDATA

SMB_CLK SMB_DATA

SMBus Address:A0

2N7002SPT

DIMM 2

ICH_SMBCLK ICH_SMBDATA

SCL SDA

SRN4K7J-8-GP

SMBus Address:A4

SCL1 BAT_SCL BAT_SDA

ICH_SMBCLK ICH_SMBDATA

Clock Generator

SCLK SDATA

SDA1

SMBus address:D2

KBC NPCE781BA0DX

+KBC_PWR

ICH_SMBCLK ICH_SMBDATA

SMB_CLK

SMB_DATA SRN4K7J-8-GP

+3.3V_RUN

GPIO61/SCL2 GPIO62/SDA2

KBC_SCL1 2N7002DW-1-GP KBC_SDA1

+3.3V_RUN

SRN2K2J-1-GP

3

DDC1CLK DDC1DATA

LDDC_CLK LDDC_DATA

LCD CONN

+5V_CRT_RUN

+3.3V_RUN

+3.3V_RUN SRN2K2J-1-GP

VGA

DDC2CLK DDC2DATA GMCH_DDCCLK GMCH_DDCDATA

2N7002DW-1-GP

Minicard WLAN

SRN10KJ-5-GP

TouchPad Conn.

TPDATA TPCLK TPDATA TPCLK

1

SRN100J-3-GP PBAT_SMBCLK1 PBAT_SMBDAT1

Battery Conn.

CLK_SMB DAT_SMB

SMBus address:16

BQ24745

SCL SDA

SMBus address:12

+3.3V_RUN

2

SRN4K7J-8-GP

Thermal

THERM_SCL THERM_SDA SCL SDA

SMBus address:7A

SRN2K2J-1-GP

DDC_CLK_CON DDC_DATA_CON

CRT CONN

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size A2 Date:

D

Document Number

SMBUS Block Diagram

Sheet 4 of

E

DJ1 Montevina UMA

Rev

A00

88

Wednesday, February 24, 2010

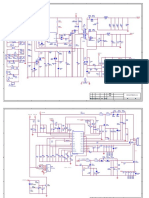

Thermal Block Diagram

1

Audio Block Diagram

1

SPKR_PORT_D_L-/L+ SPKR_PORT_D_R-/R+

2CH SPEAKERS

DP1

H_THERMDA SC470P50V3JN-2GP

CPU

THRMDA HP1_PORT_B_L HP1_PORT_B_R THRMDC

HP OUT

2

DN1

H_THERMDC

Codec 92HD79B1

Thermal EMC2102

DP2 EMC2102_DP2 PMBS3904-1-GP SC470P50V3JN-2GP DN2 EMC2102_DN2

HP0_PORT_A_L HP0_PORT_A_R VREFOUT_A_OR_F

MIC IN

Put between CPU and NB

DP3

EMC2102_DP3 PMBS3904-1-GP SC470P50V3JN-2GP

DN3

EMC2102_DN3

HW T8 sensor

PORTC_L PORTC_R VREFOUT_C

Analog MIC

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

A B C D

Thermal/Audio Block Diagram

DJ1 Montevina UMA

Sheet

E

Rev

A00

5 of 88

Wednesday, February 24, 2010

ICH9M Functional Strap Definitions

Signal

HDA_SDOUT

1

Usage/When Sampled

XOR Chain Entrance / PCI Express* Port Config 1 bit 1 (Port 1-4), Rising Edge of PWROK PCI Express Port Config 1 bit 0 (Port 1-4), Rising Edge of PWROK. PCI Express Port Config 2 bit 2 (Port 5-6), Rising Edge of PWROK Reserved, Rising Edge of PWROK ESI Strap (Server Only), Rising Edge of PWROK.

ICH9 EDS 642879 Comment

Rev.2.3

ICH9 Integrated pull-up and pull-down Resistors

ICH9 EDS 642879 Rev.2.3

Cantiga chipset and ICH9M I/O controller Hub strapping configuration

Montevina Platform Design guide 355648 Rev.2.3

Pin Name

CFG2:0

Allows entrance to XOR Chain testing when TP3 pulled low at rising edge of PWROK. When TP3 not pulled low at rising edge of PWROK, sets bit 1 of RPC.PC (Chipset Config Registers: Offset 224h).This signal has a weak internal pull-down. This signal has a weak internal pull-down. Sets bit 0 of RPC.PC (Chipset Config Registers: Offset 224h) This signal has a weak internal pull-up. Sets bit 2 of RPC.PC2 (Chipset Config Registers:Offset 0224h) when sampled low. This signal has a weak internal pull-down. NOTE: This signal should not be pulled high Tying this strap low configures DMI for ESIcompatible operation. This signal has a weak internal pull-up. NOTE: ESI compatible mode is for server platforms only. This signal should not be pulled low for desktop and mobile. Sampled low: this indicates that the system is strapped to the top-block swap mode (IntelR ICH9 inverts A16 for all cycles targeting BIOS space). The status of this strap is readable via the Top Swap bit (Chipset Config Registers:Offset 3414h: bit 0). Note that software will not be able to clear the Top-Swap bit until the system is rebooted without GNT3# being pulled down. Controllable via Boot BIOS Destination bit (Chipset Config Registers:Offset 3410h:bit 11). This strap is used in conjunction with Boot BIOS Destination Selection 0 strap. Bit11 (GNT0#) 0 1 1 0 Bit 10 Boot BIOS (SPI_CS1#) Destination 1 SPI 0 PCI 1 LPC 0 Reserved

SIGNAL

CL_CLK[1:0] CL_DATA[1:0] CL_RST0# DPRSLPVR/GPIO16 HDA_BIT_CLK HDA_DOCK_EN#/GPIO33 HDA_RST# HDA_SDIN[3:0] HDA_SDOUT HDA_SYNC

GNT0#, GNT[3:1]#/ GPIO[55,53,51]

Resistor Type/Value

PULL-UP 20K PULL-UP 20K PULL-UP 10K PULL-DOWN 20K PULL-DOWN 20K PULL-UP 20K PULL-DOWN 20K PULL-DOWN 20K PULL-DOWN 20K PULL-DOWN 20K PULL-UP 20K

Strap Description

FSB Frequency

Configuration

000 = FSB1066 010 = FSB800 011 = FSB667 Others = Reserved 0 = DMI x2 1 = DMI x4 (Default) 0 = The iTPM Host Interface is enabled (Note 2) 1 = The iTPM Host Interface is disabled (default) 0 = Intel Management Engine Crypto Transport Layer Security (TLS) cipher suite with no confidentiality 1 = Intel Management Engine Crypto TLS cipher suite with confidentiality (default) 0 = Reverse Lanes, 15->0, 14->1 etc. 1 = Normal operation (default): Lane Numbered in Order

1

HDA_SYNC

CFG5

DMI x2 Select

GNT2#/ GPIO53 GPIO20 GNT1#/ GPIO51

CFG6

ITPM Host Interface

CFG7

Intel Management engine crypto strap

CFG9

PCIE Graphics Lane

GPIO20 GPIO49 LAD[3:0]# / FHW[3:0]# LAN_RXD[2:0] LDRQ0 LDRQ1 / GPIO23 PME# PWRBTN# SATALED#

SPI_CS1# / GPIO58 (Desktop Only) / CLGPIO6 (Digital Office Only)

PULL-DOWN 20K PULL-UP 20K PULL-UP 20K PULL-UP 20K PULL-UP 20K PULL-UP 20K PULL-UP 20K PULL-UP 20K PULL-UP 15K PULL-UP 20K

CFG19 DMI Lane Reversal CFG13 CFG16 XOR FSB Dynamic ODT CFG12 CFG10

GNT3#/ GPIO55

Top-Block Swap override. Rising Edge of PWROK.

PCIE Loopback enable 0 = Enable (Note 3) 1 = Disable (Default) ALLZ 0 =ALLZ mode enabled (Note 3) 1 = Disable (Default) 0 = XOR mode enabled (Note 3) 1 = Disable (Default) 0 = Dynamic ODT Disabled 1 = Dynamic ODT Enabled (Default) 0 = Normal operation (Default): Lane Numbered in Order 1 = Reverse Lanes DMI x4 mode [MCH->ICH]: (3->0, 2->1, 1->2 and 0->3) DMI x2 mode [MCH->ICH]: (3->0, 2->1)

2

GNT0#

Boot BIOS Destination Selection 1, Rising Edge of PWROK.

SPI_MOSI SPI_MISO SPKR TACH[3:0] TP3 USB[11:0][P,N]

PULL-DOWN 20K PULL-UP 20K

CFG20

SPI_CS1#/ GPIO58

Boot BIOS Destination Controllable via Boot BIOS Destination Selection 0, bit (Chipset Config Registers:Offset 3410h:bit 10). Rising Edge of CLPWROK. This strap is used in conjunction with Boot BIOS Destination Selection 1 strap. Bit11 (GNT0#) 0 1 1 0 Bit 10 Boot BIOS (SPI_CS1#) Destination 1 SPI 0 PCI 1 LPC 0 Reserved

PULL-DOWN 20K PULL-UP 20K PULL-UP 20K PULL-DOWN 15K

SDVO _CTRLDATA (Note4) L_DDC_DATA

Digital Display Port 0 = Only digital DisplayPort (SDVO/DP/HDMI) or (SDVO/DP/HDMI) PCIe is operational (default) Concurrent with PCIe 1 = Digital DisplayPort (SDVO/DP/HDMI) and PCIe are operating simultaneously via the PEG port SDVO Present 0 = No SDVO/HDMI/DP interface disabled (default) 1 = SDVO/HDMI/DP interface enabled 0 = LFP Disabled (Default) 1 = LFP Card Present; PCIE disabled 0 = Digital display (HDMI/DP) device absent (default) 1 = Digital display (HDMI/DP) Device Present

3

PCIE Routing

LANE1 LANE2 LANE3

USB Pair 0 1 2 3 4 5 6 7 8 9 10 11

Local Flat Panel (LFP) Present Digital Display Present

SATALED#

PCI Express Lane Reversal (Lanes 1-4). Rising Edge of PWROK.

Signal has weak internal pull-up. Sets bit 27 of MPC.LR (Device 28: Function 0: Offset D8) Sampled high: this indicates that the system is strapped to the No Reboot mode (ICH9 will disable the TCO Timer system reboot feature). The status of this strap is readable via the NO REBOOT bit (Chipset Config Registers:Offset 3410h:bit 5).

MiniCard WLAN LAN

Device USB0 (I/O Board) USB1 (I/O Board 17") USB2 USB3 BLUETOOTH RESERVED WLAN RESERVED RESERVED RESERVED Card Reader CAMERA

C

SPKR

No Reboot, Rising Edge of PWROK.

USB Table

DDPC _CTRLDATA (Note4) CFG4:3 CFG8 CFG11 CFG14 CFG15 CFG17 CFG18 NOTE:

Reserved

TP3

XOR Chain Entrance. Rising Edge of PWROK.

This signal should not be pull low unless using XOR Chain testing. Sampled low: the Flash Descriptor Security will be overridden. Sampled high: the security measures will be in effect. This strap should only be enabled in manufacturing environments. The signal is required to be high for mobile applications. Sampled low: the Integrated TPM will be disabled. Sampled high: the MCH TPM enable strap is sampled low and the TPM Disable bit is clear, the Integrated TPM will be enabled. NOTE: This signal is required to be floating or pulled low for desktop applications.

GPIO33 / HDA_DOCK_ Flash Descriptor Security Override Strap. EN# Rising Edge of PWROK. (Mobile Only)

4

1. All strap signals are sampled with respect to the leading edge of the GMCH Power OK (PWROK) signal. 2. iTPM can be disabled by a Soft-Strap option in the Flash-descriptor section of the Firmware. This Soft-Strap is activated only after enabling iTPM via CFG6. 3. Only one of the CFG10/CFG12/CFG13 straps can be enabled at any time. 4. DDPC_CTRL_DATA & SDVO_CTRL_DATA straps should both be high to enable Display Port.

DJ1

4

GPIO49

DMI Termination Voltage. Rising Edge of CLPWROK. Integrated TPM Enable. Rising Edge of CLPWROK.

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

SPI_MOSI (Moble Only)

Table of Content

Sheet

E

Rev

DJ1 Montevina UMA

6 of 88

A00

Wednesday, February 24, 2010

SSID = CLOCK

3D3V_S0_CK505 +1.05V_VCCP R704 C702 SC1U10V3KX-3GP 1D05V_CK505_IO 1D05V_CK505_IO MINI1_CLKREQ# R702 1

2 10KR2J-3-GP

+3.3V_RUN

2

C704 SCD1U16V2KX-3GP C705 SCD1U16V2KX-3GP C706 SCD1U16V2KX-3GP C707 SCD1U16V2KX-3GP C708 SCD1U16V2KX-3GP Do Not Stuff C709 SCD1U16V2KX-3GP

CLK_XTAL_IN X701 CLK_XTAL_OUT

D

1 1

C710 SC15P50V2JN-2-GP

X-14D31818M-37GP

C711

4 16 9 46 62 23

U701

VDD_IO VDD_PLL3_IO VDD_SRC_IO VDD_SRC_IO VDD_SRC_IO VDD_CPU_IO

VDD_REF VDD_48 VDD_PCI VDD_SRC VDD_CPU VDD_PLL3

SC15P50V2JN-2-GP

19 27 43 52 33 56

CPUT0 CPUC0 CPUT1 CPUC1 SRCT8/CPU2_ITPT SRCC8/CPU2_ITPC SRCT7/CR#_F SRCC7/CR#_E SRCT6 SRCC6

61 60 58 57 54 53 51 50 48 47 41 42 40 39 37 38 34 35 31 32 28 29 24 25 20 21

CLK_CPU_BCLK CLK_CPU_BCLK# CLK_MCH_BCLK CLK_MCH_BCLK#

CLK_CPU_BCLK 8 CLK_CPU_BCLK# 8 CLK_MCH_BCLK 10 CLK_MCH_BCLK# 10

+3.3V_RUN R706 C713 SC1U10V3KX-3GP

3D3V_S0_CK505 32 CLK_48M_CARD R705 1

2 22R2J-2-GP 1

R701 2 22R2J-2-GP FSA

3 2 17

XN XOUT USB_48/FSA

2

C715 SCD1U16V2KX-3GP C716 SCD1U16V2KX-3GP C701 SCD1U16V2KX-3GP C717 SCD1U16V2KX-3GP C714 SC10U6D3V5KX-1GP C718 SCD1U16V2KX-3GP Do Not Stuff C719 Do Not Stuff 22 CLK_48M_ICH

DY

1 C712

22 22 H_STP_PCI# H_STP_CPU#

2 DYDo Not Stuff 45 44 PC_STOP# CPU_STOP#

CLK_PCIE_LAN CLK_PCIE_LAN# CLK_PCIE_ICH CLK_PCIE_ICH#

CLK_PCIE_LAN 76 CLK_PCIE_LAN# 76 CLK_PCIE_ICH 21 CLK_PCIE_ICH# 21

18,19,22,76 ICH_SMBCLK 18,19,22,76 ICH_SMBDATA 22 CK_PWRGD

7 6 63

SCLK SDATA CKPW RGD/PW RDW N#

SRCT10 SRCC10 SRCT1/CR#_H SRCC1/CR#_G SRCT9 SRCC9 SRCT4 SRCC4 SRCT3/CR#_C SRCC3/CR#_D SRCT2/SATAT SRCC2/SATAC

MINI1_CLKREQ# CLK_PCIE_MINI1 CLK_PCIE_MINI1# CLK_MCH_3GPLL CLK_MCH_3GPLL#

76

C

22 CLKSATAREQ# 11 CLKREQ#_B 58 PCLK_FWH 37 21 PCLK_KBC CLK_PCI_ICH

R707 1 R708 2 R709 1 R710 1

2 475R2F-L1-GP 1 Do Not Stuff

CLKSATAREQ# CLKREQ#_1 PCI2_TME 27_SEL ITP_EN

DY

2 33R2J-2-GP 2 33R2J-2-GP

8 10 11 12 13 14

PCI0/CR#_A PCI1/CR#_B PCI2/TME PCI3 PCI4/GCLK_SEL PCIF0/ITP_EN

CLK_PCIE_MINI1 76 CLK_PCIE_MINI1# 76 CLK_MCH_3GPLL 11 CLK_MCH_3GPLL# 11

CLK_PCIE_SATA CLK_PCIE_SATA# MCH_SSCDREFCLK MCH_SSCDREFCLK# CLK_MCH_DREFCLK CLK_MCH_DREFCLK#

22

CLK_14M_ICH C720 Do Not Stuff C721 Do Not Stuff

R711 1 C722 Do Not Stuff

2 33R2J-2-GP

FSB FSC

64 5 55

CLK_PCIE_SATA 20 CLK_PCIE_SATA# 20 MCH_SSCDREFCLK 11 MCH_SSCDREFCLK# 11 CLK_MCH_DREFCLK 11 CLK_MCH_DREFCLK# 11

FSB/TEST_MODE REF0/FSC/TEST_SEL NC#55 VSS_IO VSS_SRC VSS_SRC VSS_SRC VSS_CPU VSS_PLL3 VSS_48 VSS_PCI VSS_REF SRCT1/LCDT_100/27M_NSS SRCC1/LCDT_100/27M_SS SRCT0/DOT96T SRCC0/DOT96C

DY

DY

DY

GND 65

18 15 1

22 30 36 49 59 26

SLG8SP513VTR-GP

Main = 71.08513.003(SLG) Second = 71.09356.00W(ICS)

B B

3D3V_S0_CK505

3D3V_S0_CK505

27_SEL R713 10KR2J-3-GP

R712 10KR2J-3-GP

ITP_EN 0 1

Output SRC8 CPU_ITP

2

PCI2_TME

PCI2_TME

Output Overclocking of CPU and SRC allowed Overclocking of CPU and SRC not allowed

1

ITP_EN R715 Do Not Stuff

R714 10KR2J-3-GP

0

R716 Do Not Stuff

DY

2

DY

2

27_SEL 0 1

PIN20/21 96M 100M

PIN24/25 100M 27M

SEL2 SEL1 SEL0 FSC FSB FSA 1 0 0 0 0 0 0 1 1 0

5

CPU

100M 133M 166M 200M 266M

FSB

X 533M 667M 800M 1067M

8 8 8

CPU_BSEL2 CPU_BSEL1 CPU_BSEL0

R717 1 R718 1 R719 1 R720 1 R721 1 R722 1

2 10KR2J-3-GP 2 Do Not Stuff 2 2K2R2J-2-GP 2 1KR2J-1-GP 2 1KR2J-1-GP 2 1KR2J-1-GP

FSC FSB FSA DJ1

A

1 1 1 0 0

Wistron Corporation

MCH_CLKSEL0 11 MCH_CLKSEL1 11 MCH_CLKSEL2 11 Title Size Document Number Custom Date: 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C.

Clock Generator SLG8SP513VTR

DJ1 Montevina UMA

Sheet

1

Rev

A00

of 88

Friday, February 26, 2010

SSID = CPU

CPU1A 1 OF 4

D

1 ADS# BNR# BPRI# H1 E2 G5 H5 F21 E1 F1 D20 CPU_IERR# B3 H4 C1 F3 F4 G3 G2 G6 E4 AD4 AD3 AD1 AC4 AC2 AC1 AC5 AA6 AB3 AB5 AB6 C20

H_CPURST# H_RS#0 H_RS#1 H_RS#2

TP801 H_ADS# H_BNR# H_BPRI# 10 10 10

D

10

H_A#[35..3]

H_A#[35..3]

H_A#3 H_A#4 H_A#5 H_A#6 H_A#7 H_A#8 H_A#9 H_A#10 H_A#11 H_A#12 H_A#13 H_A#14 H_A#15 H_A#16 H_REQ#0 H_REQ#1 H_REQ#2 H_REQ#3 H_REQ#4 H_A#17 H_A#18 H_A#19 H_A#20 H_A#21 H_A#22 H_A#23 H_A#24 H_A#25 H_A#26 H_A#27 H_A#28 H_A#29 H_A#30 H_A#31 H_A#32 H_A#33 H_A#34 H_A#35

10 H_ADSTB#0 10 H_REQ#[4..0]

J4 L5 L4 K5 M3 N2 J1 N3 P5 P2 L2 P4 P1 R1 M1 K3 H2 K2 J3 L1 Y2 U5 R3 W6 U4 Y5 U1 R4 T5 T3 W2 W5 Y4 U2 V4 W3 AA4 AB2 AA3 V1 A6 A5 C4 D5 C6 B4 A3

A3# A4# A5# A6# A7# A8# A9# A10# A11# A12# A13# A14# A15# A16# ADSTB0# REQ0# REQ1# REQ2# REQ3# REQ4# A17# A18# A19# A20# A21# A22# A23# A24# A25# A26# A27# A28# A29# A30# A31# A32# A33# A34# A35# ADSTB1# A20M# FERR# IGNNE# STPCLK# LINT0 LINT1 SMI#

XDP/ITP SIGNALS

BPM0# BPM1# BPM2# BPM3# PRDY# PREQ# TCK TDI TDO TMS TRST# DBR#

H_THERMDC ITP_BPM#5 ITP_TCK ITP_TDI ITP_TDO ITP_TMS ITP_TRST# ITP_DBRESET# R803 1 R804 1

H_THERMDA, H_THERMDC routing together, Trace width / Spacing = 10 / 10 mil

DATA GRP2

ADDR GROUP 0 ADDR GROUP 1

CONTROL

DEFER# DRDY# DBSY# BR0# IERR# INIT# LOCK# RESET# RS0# RS1# RS2# TRDY# HIT# HITM#

H_DEFER# 10 H_DRDY# 10 H_DBSY# 10 H_BREQ#0 10 R802 1 H_DINV#[3..0] +1.05V_VCCP H_DSTBN#[3..0] H_DSTBP#[3..0] H_D#[63..0] H_DINV#[3..0] H_DSTBN#[3..0] H_DSTBP#[3..0] H_D#[63..0] 10 10 10 10

2 56R2J-4-GP H_INIT# 20

H_LOCK# 10 H_CPURST# 10 H_RS#[2..0] 10

H_TRDY# H_HIT# H_HITM#

10 10 10 CPU1B 2 OF 4 H_THERMDA C849 Do Not Stuff H_D#0 H_D#1 H_D#2 H_D#3 H_D#4 H_D#5 H_D#6 H_D#7 H_D#8 H_D#9 H_D#10 H_D#11 H_D#12 H_D#13 H_D#14 H_D#15

DY

THERMAL

PROCHOT# THRMDA THRMDC THERMTRIP# D21 A24 B25 C7

DY

2 Do Not Stuff 2 56R2J-4-GP

CPU_PROCHOT# +1.05V_VCCP H_THERMDA 39 H_THERMDC 39 H_THRMTRIP# 11,20,37,42

47 10 10 10 H_DSTBN#0 H_DSTBP#0 H_DINV#0

10 20 20 20 20 20 20 20

H_ADSTB#1 H_A20M# H_FERR# H_IGNNE# H_STPCLK# H_INTR H_NMI H_SMI# TP802 TP803 TP804 TP805 TP806 TP807 TP808 TP809 TP810 TP811 TP812 RSVD_CPU_1 RSVD_CPU_2 RSVD_CPU_3 RSVD_CPU_4 RSVD_CPU_5 RSVD_CPU_6 RSVD_CPU_7 RSVD_CPU_8 RSVD_CPU_9 RSVD_CPU_10 RSVD_CPU_11

H_THERMDA H_THERMDC

E22 F24 E26 G22 F23 G25 E25 E23 K24 G24 J24 J23 H22 F26 K22 H23 J26 H26 H25 N22 K25 P26 R23 L23 M24 L22 M23 P25 P23 P22 T24 R24 L25 T25 N25 L26 M26 N24 AD26 C23 D25 C24 AF26 AF1 A26 B22 B23 C21

D0# D1# D2# D3# D4# D5# D6# D7# D8# D9# D10# D11# D12# D13# D14# D15# DSTBN0# DSTBP0# DINV0# D16# D17# D18# D19# D20# D21# D22# D23# D24# D25# D26# D27# D28# D29# D30# D31# DSTBN1# DSTBP1# DINV1# GTLREF TEST1 TEST2 TEST3 TEST4 TEST5 TEST6 BSEL0 BSEL1 BSEL2

D32# D33# D34# D35# D36# D37# D38# D39# D40# D41# D42# D43# D44# D45# D46# D47# DSTBN2# DSTBP2# DINV2# D48# D49# D50# D51# D52# D53# D54# D55# D56# D57# D58# D59# D60# D61# D62# D63# DSTBN3# DSTBP3# DINV3# COMP0 COMP1 COMP2 COMP3 DPRSTP# DPSLP# DPW R# PW RGOOD SLP# PSI#

Y22 AB24 V24 V26 V23 T22 U25 U23 Y25 W 22 Y23 W 24 W 25 AA23 AA24 AB25 Y26 AA26 U22 AE24 AD24 AA21 AB22 AB21 AC26 AD20 AE22 AF23 AC25 AE21 AD21 AC22 AD23 AF22 AC23 AE25 AF24 AC20 R26 U26 AA1 Y1 E5 B5 D24 D6 D7 AE6

H_D#32 H_D#33 H_D#34 H_D#35 H_D#36 H_D#37 H_D#38 H_D#39 H_D#40 H_D#41 H_D#42 H_D#43 H_D#44 H_D#45 H_D#46 H_D#47 H_DSTBN#2 10 H_DSTBP#2 10 H_DINV#2 10 H_D#48 H_D#49 H_D#50 H_D#51 H_D#52 H_D#53 H_D#54 H_D#55 H_D#56 H_D#57 H_D#58 H_D#59 H_D#60 H_D#61 H_D#62 H_D#63 H_DSTBN#3 10 H_DSTBP#3 10 H_DINV#3 10 COMP0 COMP1 COMP2 COMP3 R807 R809 R811 R814

DATA GRP0

R805 1

DY

2 Do Not Stuff

+1.05V_VCCP CLK_CPU_BCLK 7 CLK_CPU_BCLK# 7

HCLK

M4 N5 T2 V3 B2 C3 D2 D22 D3 F6 B1

RSVD#M4 RSVD#N5 RSVD#T2 RSVD#V3 RSVD#B2 RSVD#C3 TEST7 RSVD#D2 RSVD#D22 RSVD#D3 RSVD#F6

RESERVED

+1.05V_VCCP

R806 1KR2F-3-GP

DATA GRP3

BCLK0 BCLK1

A22 A21

H_THRMTRIP# should connect to ICH9 and MCH without T-ing.

H_D#16 H_D#17 H_D#18 H_D#19 H_D#20 H_D#21 H_D#22 H_D#23 H_D#24 H_D#25 H_D#26 H_D#27 H_D#28 H_D#29 H_D#30 H_D#31 H_DSTBN#1 H_DSTBP#1 H_DINV#1 R808 1 R810 1 R813 1 R815 1

KEY_NC

BGA479-SKT6-GPU7

62.10079.001

R812 2KR2F-3-GP

ICH ICH

DATA GRP1

10 10 10 CPU_GTLREF0 C801 SC1KP50V2KX-1GP

DY DY DY DY

2 Do Not Stuff 2 Do Not Stuff 2 Do Not Stuff 2 Do Not Stuff

TEST1 TEST2 CPU_TEST3 CPU_TEST5

MISC

1 1 1 1

2 2 2 2

27D4R2F-L1-GP 54D9R2F-L1-GP 27D4R2F-L1-GP 54D9R2F-L1-GP

+1.05V_VCCP

7 7 7

CPU_BSEL0 CPU_BSEL1 CPU_BSEL2

H_DPRSTP# 11,20,47 H_DPSLP# 20 H_DPWR# 10 H_PWRGOOD 20,42 H_CPUSLP# 10 PSI# 47

ITP_TMS ITP_TDI ITP_BPM#5 ITP_TDO

R816 1 R817 1 R818 1 R801 1

2 51R2F-2-GP 2 51R2F-2-GP 2 51R2F-2-GP

Layout notes Z= 55 Ohm 0.5" MAX for CPU_GTLREF0

BGA479-SKT6-GPU7

62.10079.001

DY

2 Do Not Stuff

Layout Note: Comp0, 2 connect with Zo=27.4 ohm, make trace length shorter than 0.5". Comp1, 3 connect with Zo=55 ohm, make trace length shorter than 0.5".

DJ1

A

+3.3V_RUN

A

ITP_DBRESET#

R825 1

DY

2 Do Not Stuff

TP813 ITP_TCK ITP_TRST# R819 1 R820 1

2 51R2F-2-GP 2 51R2F-2-GP

H_CPURST#

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

All place within 2" to CPU

CPU-FSB(1/2)

Sheet

1

Rev

DJ1 Montevina UMA

8 of 88

A00

Friday, February 26, 2010

SSID = CPU

+VCC_CORE C907 SC22U6D3V5MX-2GP C909 SC22U6D3V5MX-2GP C902 Do Not Stuff C901 Do Not Stuff C920 Do Not Stuff C903 Do Not Stuff C904 Do Not Stuff C905 Do Not Stuff C906 Do Not Stuff C908 Do Not Stuff CPU1D 4 OF 4

DY

+VCC_CORE +VCC_CORE

DY

DY

DY

DY

DY

DY

DY

C910 SC10U6D3V5KX-1GP

CPU1C3 OF 4

+VCC_CORE

A7 A9 A10 A12 A13 A15 A17 A18 A20 B7 B9 B10 B12 B14 B15 B17 B18 B20 C9 C10 C12 C13 C15 C17 C18 D9 D10 D12 D14 D15 D17 D18 E7 E9 E10 E12 E13 E15 E17 E18 E20 F7 F9 F10 F12 F14 F15 F17 F18 F20 AA7 AA9 AA10 AA12 AA13 AA15 AA17 AA18 AA20 AB9 AC10 AB10 AB12 AB14 AB15 AB17 AB18

VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

SCD1U10V2KX-5GP

VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCP VCCA VCCA VID0 VID1 VID2 VID3 VID4 VID5 VID6 VCCSENSE VSSSENSE

AB20 AB7 AC7 AC9 AC12 AC13 AC15 AC17 AC18 AD7 AD9 AD10 AD12 AD14 AD15 AD17 AD18 AE9 AE10 AE12 AE13 AE15 AE17 AE18 AE20 AF9 AF10 AF12 AF14 AF15 AF17 AF18 AF20 G21 V6 J6 K6 M6 J21 K21 M21 N21 N6 R21 R6 T21 T6 V21 W 21 B26 C26 AD6 AF5 AE5 AF4 AE3 AF3 AE2 AF7 AE7

CPU_VID0 CPU_VID1 CPU_VID2 CPU_VID3 CPU_VID4 CPU_VID5 CPU_VID6 CPU_VID[6..0]

+VCC_CORE C923 SC22U6D3V5MX-2GP C926 SC22U6D3V5MX-2GP C927 SC22U6D3V5MX-2GP C930 SC22U6D3V5MX-2GP C931 SC22U6D3V5MX-2GP C924 SC10U6D3V5KX-1GP C928 SC10U6D3V5KX-1GP C925 Do Not Stuff C929 Do Not Stuff

DY

DY

C932 SC22U6D3V5MX-2GP

DY

DY

DY

DY

DY

DY

C919 SC10U6D3V5KX-1GP

+1.05V_VCCP C934 SCD1U16V2KX-3GP C935 SCD1U10V2KX-5GP C936 SCD1U16V2KX-3GP C938 SCD1U10V2KX-5GP C937 SC1U6D3V2KX-GP TC901 Do Not Stuff

DY

2

layout note: "+1.5V_VCCA" as short as possible

+1.5V_VCCA

+1.5V_RUN

1 R901 2 Do Not Stuff

47

C939 SCD01U16V2KX-3GP PG902

C940 SC10U6D3V5KX-1GP

Layout Note: Place as close as possible to the CPU VCCA pin.

1 R902 2 100R2F-L1-GP-U

2 Do Not Stuff

+VCC_CORE VCC_SENSE 47 VSS_SENSE 47

VCC_SENSE and VSS_SENSE lines should be of equal length.

BGA479-SKT6-GPU7

PG901

A4 A8 A11 A14 A16 A19 A23 AF2 B6 B8 B11 B13 B16 B19 B21 B24 C5 C8 C11 C14 C16 C19 C2 C22 C25 D1 D4 D8 D11 D13 D16 D19 D23 D26 E3 E6 E8 E11 E14 E16 E19 E21 E24 F5 F8 F11 F13 F16 F19 F2 F22 F25 G4 G1 G23 G26 H3 H6 H21 H24 J2 J5 J22 J25 K1 K4 K23 K26 L3 L6 L21 L24 M2 M5 M22 M25 N1 N4 N23 N26 P3

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

62.10079.001

1 R903 2 100R2F-L1-GP-U

2 Do Not Stuff

BGA479-SKT6-GPU7

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

P6 P21 P24 R2 R5 R22 R25 T1 T4 T23 T26 U3 U6 U21 U24 V2 V5 V22 V25 W1 W4 W 23 W 26 Y3 Y6 Y21 Y24 AA2 AA5 AA8 AA11 AA14 AA16 AA19 AA22 AA25 AB1 AB4 AB8 AB11 AB13 AB16 AB19 AB23 AB26 AC3 AC6 AC8 AC11 AC14 AC16 AC19 AC21 AC24 AD2 AD5 AD8 AD11 AD13 AD16 AD19 AD22 AD25 AE1 AE4 AE8 AE11 AE14 AE16 AE19 AE23 AE26 A2 AF6 AF8 AF11 AF13 AF16 AF19 AF21 A25 AF25

C921 SC22U6D3V5MX-2GP

C915 SC22U6D3V5MX-2GP

C918 SC22U6D3V5MX-2GP

C917 SC10U6D3V5KX-1GP

C911 Do Not Stuff

C912 Do Not Stuff

C913 Do Not Stuff

C914 Do Not Stuff

C916 Do Not Stuff

C922 Do Not Stuff

C933

NCTF PIN

CPU_GND1 TP902

B

CPU_GND2 CPU_GND3

TP901 TP903

CPU_GND4

TP904

62.10079.001

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

5 4 3 2

CPU-Power(2/2)

Sheet

1

Rev

DJ1 Montevina UMA

9 of 88

A00

Friday, February 26, 2010

SSID = MCH

NB1A 8 H_D#[63..0] H_D#[63..0] H_D#0 H_D#1 H_D#2 H_D#3 H_D#4 H_D#5 H_D#6 H_D#7 H_D#8 H_D#9 H_D#10 H_D#11 H_D#12 H_D#13 H_D#14 H_D#15 H_D#16 H_D#17 H_D#18 H_D#19 H_D#20 H_D#21 H_D#22 H_D#23 H_D#24 H_D#25 H_D#26 H_D#27 H_D#28 H_D#29 H_D#30 H_D#31 H_D#32 H_D#33 H_D#34 H_D#35 H_D#36 H_D#37 H_D#38 H_D#39 H_D#40 H_D#41 H_D#42 H_D#43 H_D#44 H_D#45 H_D#46 H_D#47 H_D#48 H_D#49 H_D#50 H_D#51 H_D#52 H_D#53 H_D#54 H_D#55 H_D#56 H_D#57 H_D#58 H_D#59 H_D#60 H_D#61 H_D#62 H_D#63

1 OF 10

H_A#[35..3]

+1.05V_VCCP

H_SWING routing Trace width and Spacing use 10 / 20 mil H_SWING Resistors and Capacitors close MCH 500 mil ( MAX )

1

R1002 221R2F-2-GP

H_SWING

C1002 SCD1U10V2KX-5GP

R1001 100R2F-L1-GP-U

H_RCOMP routing Trace width and Spacing use 10 / 20 mil

B

1 R1003

2 H_RCOMP 24D9R2F-L-GP

Place R1001 near to the chip ( < 0.5")

F2 G8 F8 E6 G2 H6 H2 F6 D4 H3 M9 M11 J1 J2 N12 J6 P2 L2 R2 N9 L6 M5 J3 N2 R1 N5 N6 P13 N8 L7 N10 M3 Y3 AD14 Y6 Y10 Y12 Y14 Y7 W2 AA8 Y9 AA13 AA9 AA11 AD11 AD10 AD13 AE12 AE9 AA2 AD8 AA3 AD3 AD7 AE14 AF3 AC1 AE3 AC3 AE11 AE8 AG2 AD6

H_D#_0 H_D#_1 H_D#_2 H_D#_3 H_D#_4 H_D#_5 H_D#_6 H_D#_7 H_D#_8 H_D#_9 H_D#_10 H_D#_11 H_D#_12 H_D#_13 H_D#_14 H_D#_15 H_D#_16 H_D#_17 H_D#_18 H_D#_19 H_D#_20 H_D#_21 H_D#_22 H_D#_23 H_D#_24 H_D#_25 H_D#_26 H_D#_27 H_D#_28 H_D#_29 H_D#_30 H_D#_31 H_D#_32 H_D#_33 H_D#_34 H_D#_35 H_D#_36 H_D#_37 H_D#_38 H_D#_39 H_D#_40 H_D#_41 H_D#_42 H_D#_43 H_D#_44 H_D#_45 H_D#_46 H_D#_47 H_D#_48 H_D#_49 H_D#_50 H_D#_51 H_D#_52 H_D#_53 H_D#_54 H_D#_55 H_D#_56 H_D#_57 H_D#_58 H_D#_59 H_D#_60 H_D#_61 H_D#_62 H_D#_63

H_A#_3 H_A#_4 H_A#_5 H_A#_6 H_A#_7 H_A#_8 H_A#_9 H_A#_10 H_A#_11 H_A#_12 H_A#_13 H_A#_14 H_A#_15 H_A#_16 H_A#_17 H_A#_18 H_A#_19 H_A#_20 H_A#_21 H_A#_22 H_A#_23 H_A#_24 H_A#_25 H_A#_26 H_A#_27 H_A#_28 H_A#_29 H_A#_30 H_A#_31 H_A#_32 H_A#_33 H_A#_34 H_A#_35 H_ADS# H_ADSTB#_0 H_ADSTB#_1 H_BNR# H_BPRI# H_BREQ# H_DEFER# H_DBSY# HPLL_CLK HPLL_CLK# H_DPW R# H_DRDY# H_HIT# H_HITM# H_LOCK# H_TRDY#

A14 C15 F16 H13 C18 M16 J13 P16 R16 N17 M13 E17 P17 F17 G20 B19 J16 E20 H16 J20 L17 A17 B17 L16 C21 J17 H20 B18 K17 B20 F21 K21 L20 H12 B16 G17 A9 F11 G12 E9 B10 AH7 AH6 J11 F9 H9 E12 H11 C9

H_A#3 H_A#4 H_A#5 H_A#6 H_A#7 H_A#8 H_A#9 H_A#10 H_A#11 H_A#12 H_A#13 H_A#14 H_A#15 H_A#16 H_A#17 H_A#18 H_A#19 H_A#20 H_A#21 H_A#22 H_A#23 H_A#24 H_A#25 H_A#26 H_A#27 H_A#28 H_A#29 H_A#30 H_A#31 H_A#32 H_A#33 H_A#34 H_A#35

H_A#[35..3]

H_ADS# 8 H_ADSTB#0 8 H_ADSTB#1 8 H_BNR# 8 H_BPRI# 8 H_BREQ#0 8 H_DEFER# 8 H_DBSY# 8 CLK_MCH_BCLK 7 CLK_MCH_BCLK# 7 H_DPWR# 8 H_DRDY# 8 H_HIT# 8 H_HITM# 8 H_LOCK# 8 H_TRDY# 8

HOST

H_DINV#[3..0]

H_DINV#_0 H_DINV#_1 H_DINV#_2 H_DINV#_3 H_DSTBN#_0 H_DSTBN#_1 H_DSTBN#_2 H_DSTBN#_3 H_DSTBP#_0 H_DSTBP#_1 H_DSTBP#_2 H_DSTBP#_3 H_REQ#_0 H_REQ#_1 H_REQ#_2 H_REQ#_3 H_REQ#_4 H_RS#_0 H_RS#_1 H_RS#_2

J8 L3 Y13 Y1 L10 M7 AA5 AE6 L9 M8 AA6 AE5 B15 K13 F13 B13 B14 B6 F12 C8

H_DINV#0 H_DINV#1 H_DINV#2 H_DINV#3 H_DSTBN#[3..0] H_DSTBN#0 H_DSTBN#1 H_DSTBN#2 H_DSTBN#3 H_DSTBP#[3..0] H_DSTBP#0 H_DSTBP#1 H_DSTBP#2 H_DSTBP#3 H_REQ#[4..0] H_REQ#0 H_REQ#1 H_REQ#2 H_REQ#3 H_REQ#4 H_RS#[2..0] H_RS#0 H_RS#1 H_RS#2

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

H_REQ#[4..0]

+1.05V_VCCP

H_SWING H_RCOMP H_CPURST# H_CPUSLP#

C5 E3 C12 E11 A11 B11

H_SW ING H_RCOMP H_CPURST# H_CPUSLP# H_AVREF H_DVREF

CANTIGA-GM-GP-U-NF

2

8 R1004 8 1KR2F-3-GP

H_RS#[2..0]

H_AVREF

R1005 2KR2F-3-GP

1 2

DY

C1001 Do Not Stuff

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

5 4 3 2

Cantiga-Host(1/6)

Sheet

1

Rev

DJ1 Montevina UMA

10 of 88

A00

Friday, February 26, 2010

+1.5V_SUS

SSID = MCH *

D

NB1B

2 OF 10

DDR CLK/ CONTROL/COMPENSATION

is current setting CFG Strap CFG 5 CFG 6 CFG 7 CFG 9 CFG 10 CFG 12 CFG 13 CFG 16 Low DMI X 2 ITPM enable TLS cipher suite with no confidentiality PCIE GFX lane reversed PCIE loopback enable ALLZ mode enable XOR mode enable

FSB dynamic ODT disable

High

C1105 Do Not Stuff

C1106 Do Not Stuff

CFG 19 DMI Lane Reserved CFG 20 SDVO concurrent with PCIE SDVO_CTRLDATA L_DDC_DATA DDPC_CTRLDATA

C

* ITPM disable * TLS cipher suite with * confidentiality PCIE GFX lane numbered in oder * PCIE loopback disable * ALLZ mode disable * XOR mode disable * FSB Dynamic ODT enable *

DMI X 4

C1104 SC2D2U6D3V3KX-GP

C1101 SCD01U16V2KX-3GP

B31 B2 M1 AY21

SA_CKE_0 SA_CKE_1 SB_CKE_0 SB_CKE_1 SA_CS#_0 SA_CS#_1 SB_CS#_0 SB_CS#_1 SA_ODT_0 SA_ODT_1 SB_ODT_0 SB_ODT_1 SM_RCOMP SM_RCOMP# SM_RCOMP_VOH SM_RCOMP_VOL SM_VREF SM_PWROK SM_REXT SM_DRAMRST#

BC28 AY28 AY36 BB36 BA17 AY16 AV16 AR13 BD17 AY17 BF15 AY13 BG22 BH21 BF28 BH28 AV42 AR36 BF17 BC36 B38 A38 E41 F41 F43 E43

M_RCOMPP M_RCOMPN SM_RCOMP_VOH SM_RCOMP_VOL CANTIGA_SM_VREF SM_PW ROK SM_REXT DDR3_DRAMRST# CLK_MCH_DREFCLK CLK_MCH_DREFCLK# MCH_SSCDREFCLK MCH_SSCDREFCLK# CLK_MCH_3GPLL CLK_MCH_3GPLL#

M_CKE0 M_CKE1 M_CKE2 M_CKE3 M_CS#0 M_CS#1 M_CS#2 M_CS#3 M_ODT0 M_ODT1 M_ODT2 M_ODT3

18 18 19 19 18 18 19 19 18 18 19 19

C1102 SC2D2U6D3V3KX-GP

R1104 3K01R2F-3-GP

RESERVED#B31 RESERVED#B2 RESERVED#M1 RESERVED#AY21

R1105 80D6R2F-L-GP

SM_RCOMP_VOL

M36 N36 R33 T33 AH9 AH10 AH12 AH13 K12 AL34 AK34 AN35 AM35 T24

RESERVED#M36 RESERVED#N36 RESERVED#R33 RESERVED#T33 RESERVED#AH9 RESERVED#AH10 RESERVED#AH12 RESERVED#AH13 RESERVED#K12 RESERVED#AL34 RESERVED#AK34 RESERVED#AN35 RESERVED#AM35 RESERVED#T24

SA_CK_0 SA_CK_1 SB_CK_0 SB_CK_1 SA_CK#_0 SA_CK#_1 SB_CK#_0 SB_CK#_1

AP24 AT21 AV24 AU20 AR24 AR21 AU24 AV20

M_CLK_DDR0 M_CLK_DDR1 M_CLK_DDR2 M_CLK_DDR3 M_CLK_DDR#0 M_CLK_DDR#1 M_CLK_DDR#2 M_CLK_DDR#3

18 18 19 19 18 18 19 19

2

+1.5V_SUS R1102 1KR2F-3-GP

C1103 SCD01U16V2KX-3GP

R1103 80D6R2F-L-GP

SM_RCOMP_VOH

Normal operation Only PCIE or SDVO is operational

* Reverse DMI lanes PCIE and SDVO are * operatiing simultaneously via the PEG port * * *

SDVO interface enable LFP card present SDVO/iHDMI/DP interface enabled

BG23 BF23 BH18 BF18

RESERVED#BG23 RESERVED#BF23 RESERVED#BH18 RESERVED#BF18

+V_DDR_REF

DDR3_DRAMRST# SM_PW ROK 41

18,19 R1108

1 1 2 R1109 499R2F-2-GP

Do Not Stuff

SDVO interface disable LFP disable SDVO/iHDMI/DP interface disabled

DPLL_REF_CLK DPLL_REF_CLK# DPLL_REF_SSCLK DPLL_REF_SSCLK# PEG_CLK PEG_CLK#

CLK_MCH_DREFCLK 7 CLK_MCH_DREFCLK# 7 MCH_SSCDREFCLK 7 MCH_SSCDREFCLK# 7 CLK_MCH_3GPLL 7 CLK_MCH_3GPLL# 7

DY

2

DY

2

+3.3V_RUN

CLK

RSVD RSVD

R1106 1KR2F-3-GP

R1112 1 R1113 1

DY DY

RN1102

2 Do Not Stuff 2 Do Not Stuff 1 2

CFG19 CFG20

FSB setting

7 7 7 MCH_CLKSEL0 MCH_CLKSEL1 MCH_CLKSEL2 TP1102 TP1103

DMI_RXN_0 DMI_RXN_1 DMI_RXN_2 DMI_RXN_3 T25 R25 P25 P20 P24 C25 N24 M24 E21 C23 C24 N21 P21 T21 R20 M20 L21 H21 P29 R28 T28 CFG_0 CFG_1 CFG_2 CFG_3 CFG_4 CFG_5 CFG_6 CFG_7 CFG_8 CFG_9 CFG_10 CFG_11 CFG_12 CFG_13 CFG_14 CFG_15 CFG_16 CFG_17 CFG_18 CFG_19 CFG_20 DMI_RXP_0 DMI_RXP_1 DMI_RXP_2 DMI_RXP_3

AE41 AE37 AE47 AH39 AE40 AE38 AE48 AH40 AE35 AE43 AE46 AH42 AD35 AE44 AF46 AH43

DMI_ITXN0_MRXN0 DMI_ITXN1_MRXN1 DMI_ITXN2_MRXN2 DMI_ITXN3_MRXN3 DMI_ITXP0_MRXP0 DMI_ITXP1_MRXP1 DMI_ITXP2_MRXP2 DMI_ITXP3_MRXP3 DMI_IRXN0_MTXN0 DMI_IRXN1_MTXN1 DMI_IRXN2_MTXN2 DMI_IRXN3_MTXN3 DMI_IRXP0_MTXP0 DMI_IRXP1_MTXP1 DMI_IRXP2_MTXP2 DMI_IRXP3_MTXP3

DMI_ITXN0_MRXN0 DMI_ITXN1_MRXN1 DMI_ITXN2_MRXN2 DMI_ITXN3_MRXN3 DMI_ITXP0_MRXP0 DMI_ITXP1_MRXP1 DMI_ITXP2_MRXP2 DMI_ITXP3_MRXP3 DMI_IRXN0_MTXN0 DMI_IRXN1_MTXN1 DMI_IRXN2_MTXN2 DMI_IRXN3_MTXN3 DMI_IRXP0_MTXP0 DMI_IRXP1_MTXP1 DMI_IRXP2_MTXP2 DMI_IRXP3_MTXP3

21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21

4 3

PM_EXTTS#0 PM_EXTTS#1

DMI CFG

CFG3 CFG4

SRN10KJ-5-GP CFG9 CFG10

DMI_TXN_0 DMI_TXN_1 DMI_TXN_2 DMI_TXN_3 DMI_TXP_0 DMI_TXP_1 DMI_TXP_2 DMI_TXP_3

+1.05V_VCCP

+3.3V_RUN

TP1104 TP1105 TP1101 R1118 1

B

R1119 1

DY DY

2 Do Not Stuff 2 Do Not Stuff

CFG9 CFG10 CFG19 CFG20

GRAPHICS VID

CFG14 CFG15 CFG16 CFG17

R1122 56R2J-4-GP

DY

2

R1123 Do Not Stuff

B

22,37 PM_PW ROK 21,37,58,76 PLT_RST#

PW ROK_R RSTIN#

GFX_VR_EN

C34

+1.05V_VCCP

DY

ME

8,20,37,42

H_THRMTRIP#

22,47 DPRSLPVR

BG48 BF48 BD48 BC48 BH47 BG47 BE47 BH46 BF46 BG45 BH44 BH43 BH6 BH5 BG4 BH3 BF3 BH2 BG2 BE2 BG1 BF1 BD1 BC1 F1 A47

NC#BG48 NC#BF48 NC#BD48 NC#BC48 NC#BH47 NC#BG47 NC#BE47 NC#BH46 NC#BF46 NC#BG45 NC#BH44 NC#BH43 NC#BH6 NC#BH5 NC#BG4 NC#BH3 NC#BF3 NC#BH2 NC#BG2 NC#BE2 NC#BG1 NC#BF1 NC#BD1 NC#BC1 NC#F1 NC#A47 CANTIGA-GM-GP-U-NF

C1108 SCD1U10V2KX-5GP

CL_CLK CL_DATA CL_PWROK CL_RST# CL_VREF

AH37 AH36 AN36 AJ35 AH34

MCH_CLVREF

CL_CLK0 22 CL_DATA0 22 M_PW ROK 22 CL_RST#0 22

R1126 1KR2F-3-GP

+3.3V_RUN R1129 CLKREQ#_B

MCH_CLVREF ~= 0.35V

DDPC_CTRLCLK DDPC_CTRLDATA SDVO_CTRLCLK SDVO_CTRLDATA CLKREQ# ICH_SYNC# TSATN# N28 M28 G36 E36 K36 H36 B12

10KR2J-3-GP R1128 499R2F-2-GP

MISC

GMCH_HDMI_DATA

TP1106 CLKREQ#_B 7 MCH_ICH_SYNC# 22

TSATN#

A

DJ1

HDA

HDA_BCLK HDA_RST# HDA_SDI HDA_SDO HDA_SYNC

B28 B30 B29 C29 A28

Title Size Document Number Custom Date:

R1124 1

DY

2 Do Not Stuff

CFG16

22 PM_SYNC# 8,20,47 H_DPRSTP# 18 PM_EXTTS#0 19 PM_EXTTS#1 1 R1125 2 Do Not Stuff 1 2 100R2J-2-GP R1127 C1107 Do Not Stuff

R29 B7 N33 P32 AT40 AT11 T20 R32

PM_SYNC# PM_DPRSTP# PM_EXT_TS#_0 PM_EXT_TS#_1 PWROK RSTIN# THERMTRIP# DPRSLPVR

GFX_VID_0 GFX_VID_1 GFX_VID_2 GFX_VID_3 GFX_VID_4

B33 B32 G33 F33 E33

TSATN#_KBC TSATN#

TSATN#_KBC 37

C B

DY

Q1101 Do Not Stuff

PM NC NC

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C.

Cantiga-DMI/CFG(2/6)

DJ1 Montevina UMA

Sheet

1

Rev

A00

of 88

Friday, February 26, 2010

11

SSID = MCH

18 M_A_DQ[63..0]

M_A_DQ[63..0] M_A_DQ0 M_A_DQ1 M_A_DQ2 M_A_DQ3 M_A_DQ4 M_A_DQ5 M_A_DQ6 M_A_DQ7 M_A_DQ8 M_A_DQ9 M_A_DQ10 M_A_DQ11 M_A_DQ12 M_A_DQ13 M_A_DQ14 M_A_DQ15 M_A_DQ16 M_A_DQ17 M_A_DQ18 M_A_DQ19 M_A_DQ20 M_A_DQ21 M_A_DQ22 M_A_DQ23 M_A_DQ24 M_A_DQ25 M_A_DQ26 M_A_DQ27 M_A_DQ28 M_A_DQ29 M_A_DQ30 M_A_DQ31 M_A_DQ32 M_A_DQ33 M_A_DQ34 M_A_DQ35 M_A_DQ36 M_A_DQ37 M_A_DQ38 M_A_DQ39 M_A_DQ40 M_A_DQ41 M_A_DQ42 M_A_DQ43 M_A_DQ44 M_A_DQ45 M_A_DQ46 M_A_DQ47 M_A_DQ48 M_A_DQ49 M_A_DQ50 M_A_DQ51 M_A_DQ52 M_A_DQ53 M_A_DQ54 M_A_DQ55 M_A_DQ56 M_A_DQ57 M_A_DQ58 M_A_DQ59 M_A_DQ60 M_A_DQ61 M_A_DQ62 M_A_DQ63

NB1D

4 OF 10

AJ38 AJ41 AN38 AM38 AJ36 AJ40 AM44 AM42 AN43 AN44 AU40 AT38 AN41 AN39 AU44 AU42 AV39 AY44 BA40 BD43 AV41 AY43 BB41 BC40 AY37 BD38 AV37 AT36 AY38 BB38 AV36 AW 36 BD13 AU11 BC11 BA12 AU13 AV13 BD12 BC12 BB9 BA9 AU10 AV9 BA11 BD9 AY8 BA6 AV5 AV7 AT9 AN8 AU5 AU6 AT5 AN10 AM11 AM5 AJ9 AJ8 AN12 AM13 AJ11 AJ12

SA_DQ_0 SA_DQ_1 SA_DQ_2 SA_DQ_3 SA_DQ_4 SA_DQ_5 SA_DQ_6 SA_DQ_7 SA_DQ_8 SA_DQ_9 SA_DQ_10 SA_DQ_11 SA_DQ_12 SA_DQ_13 SA_DQ_14 SA_DQ_15 SA_DQ_16 SA_DQ_17 SA_DQ_18 SA_DQ_19 SA_DQ_20 SA_DQ_21 SA_DQ_22 SA_DQ_23 SA_DQ_24 SA_DQ_25 SA_DQ_26 SA_DQ_27 SA_DQ_28 SA_DQ_29 SA_DQ_30 SA_DQ_31 SA_DQ_32 SA_DQ_33 SA_DQ_34 SA_DQ_35 SA_DQ_36 SA_DQ_37 SA_DQ_38 SA_DQ_39 SA_DQ_40 SA_DQ_41 SA_DQ_42 SA_DQ_43 SA_DQ_44 SA_DQ_45 SA_DQ_46 SA_DQ_47 SA_DQ_48 SA_DQ_49 SA_DQ_50 SA_DQ_51 SA_DQ_52 SA_DQ_53 SA_DQ_54 SA_DQ_55 SA_DQ_56 SA_DQ_57 SA_DQ_58 SA_DQ_59 SA_DQ_60 SA_DQ_61 SA_DQ_62 SA_DQ_63

SA_BS_0 SA_BS_1 SA_BS_2 SA_RAS# SA_CAS# SA_W E#

BD21 BG18 AT25 BB20 BD20 AY20

19 M_B_DQ[63..0] M_A_BS0 18 M_A_BS1 18 M_A_BS2 18 M_A_RAS# 18 M_A_CAS# 18 M_A_WE# 18

M_B_DQ[63..0] M_B_DQ0 M_B_DQ1 M_B_DQ2 M_B_DQ3 M_B_DQ4 M_B_DQ5 M_B_DQ6 M_B_DQ7 M_B_DQ8 M_B_DQ9 M_B_DQ10 M_B_DQ11 M_B_DQ12 M_B_DQ13 M_B_DQ14 M_B_DQ15 M_B_DQ16 M_B_DQ17 M_B_DQ18 M_B_DQ19 M_B_DQ20 M_B_DQ21 M_B_DQ22 M_B_DQ23 M_B_DQ24 M_B_DQ25 M_B_DQ26 M_B_DQ27 M_B_DQ28 M_B_DQ29 M_B_DQ30 M_B_DQ31 M_B_DQ32 M_B_DQ33 M_B_DQ34 M_B_DQ35 M_B_DQ36 M_B_DQ37 M_B_DQ38 M_B_DQ39 M_B_DQ40 M_B_DQ41 M_B_DQ42 M_B_DQ43 M_B_DQ44 M_B_DQ45 M_B_DQ46 M_B_DQ47 M_B_DQ48 M_B_DQ49 M_B_DQ50 M_B_DQ51 M_B_DQ52 M_B_DQ53 M_B_DQ54 M_B_DQ55 M_B_DQ56 M_B_DQ57 M_B_DQ58 M_B_DQ59 M_B_DQ60 M_B_DQ61 M_B_DQ62 M_B_DQ63

NB1E

5 OF 10

M_A_DM[7..0]

M_A_DQS[7..0] M_A_DQS0 M_A_DQS1 M_A_DQS2 M_A_DQS3 M_A_DQS4 M_A_DQS5 M_A_DQS6 M_A_DQS7 M_A_DQS#0 M_A_DQS#1 M_A_DQS#2 M_A_DQS#3 M_A_DQS#4 M_A_DQS#5 M_A_DQS#6 M_A_DQS#7 M_A_A0 M_A_A1 M_A_A2 M_A_A3 M_A_A4 M_A_A5 M_A_A6 M_A_A7 M_A_A8 M_A_A9 M_A_A10 M_A_A11 M_A_A12 M_A_A13 M_A_A14

SYSTEM

DDR

DDR

SA_MA_0 SA_MA_1 SA_MA_2 SA_MA_3 SA_MA_4 SA_MA_5 SA_MA_6 SA_MA_7 SA_MA_8 SA_MA_9 SA_MA_10 SA_MA_11 SA_MA_12 SA_MA_13 SA_MA_14

BA21 BC24 BG24 BH24 BG25 BA24 BD24 BG27 BF25 AW 24 BC21 BG26 BH26 BH17 AY25

M_A_A[14..0]

18

SYSTEM

SA_DQS_0 SA_DQS_1 SA_DQS_2 SA_DQS_3 SA_DQS_4 SA_DQS_5 SA_DQS_6 SA_DQS_7 SA_DQS#_0 SA_DQS#_1 SA_DQS#_2 SA_DQS#_3 SA_DQS#_4 SA_DQS#_5 SA_DQS#_6 SA_DQS#_7

AJ44 AT44 BA43 BC37 AW 12 BC8 AU8 AM7 AJ43 AT43 BA44 BD37 AY12 BD8 AU9 AM8

M_A_DQS[7..0]

18

SA_DM_0 SA_DM_1 SA_DM_2 SA_DM_3 SA_DM_4 SA_DM_5 SA_DM_6 SA_DM_7

AM37 AT41 AY41 AU39 BB12 AY6 AT7 AJ5

M_A_DM0 M_A_DM1 M_A_DM2 M_A_DM3 M_A_DM4 M_A_DM5 M_A_DM6 M_A_DM7

M_A_DM[7..0]

18

M_A_DQS#[7..0]

M_A_DQS#[7..0]

18

M_A_A[14..0]

AK47 AH46 AP47 AP46 AJ46 AJ48 AM48 AP48 AU47 AU46 BA48 AY48 AT47 AR47 BA47 BC47 BC46 BC44 BG43 BF43 BE45 BC41 BF40 BF41 BG38 BF38 BH35 BG35 BH40 BG39 BG34 BH34 BH14 BG12 BH11 BG8 BH12 BF11 BF8 BG7 BC5 BC6 AY3 AY1 BF6 BF5 BA1 BD3 AV2 AU3 AR3 AN2 AY2 AV1 AP3 AR1 AL1 AL2 AJ1 AH1 AM2 AM3 AH3 AJ3

SB_DQ_0 SB_DQ_1 SB_DQ_2 SB_DQ_3 SB_DQ_4 SB_DQ_5 SB_DQ_6 SB_DQ_7 SB_DQ_8 SB_DQ_9 SB_DQ_10 SB_DQ_11 SB_DQ_12 SB_DQ_13 SB_DQ_14 SB_DQ_15 SB_DQ_16 SB_DQ_17 SB_DQ_18 SB_DQ_19 SB_DQ_20 SB_DQ_21 SB_DQ_22 SB_DQ_23 SB_DQ_24 SB_DQ_25 SB_DQ_26 SB_DQ_27 SB_DQ_28 SB_DQ_29 SB_DQ_30 SB_DQ_31 SB_DQ_32 SB_DQ_33 SB_DQ_34 SB_DQ_35 SB_DQ_36 SB_DQ_37 SB_DQ_38 SB_DQ_39 SB_DQ_40 SB_DQ_41 SB_DQ_42 SB_DQ_43 SB_DQ_44 SB_DQ_45 SB_DQ_46 SB_DQ_47 SB_DQ_48 SB_DQ_49 SB_DQ_50 SB_DQ_51 SB_DQ_52 SB_DQ_53 SB_DQ_54 SB_DQ_55 SB_DQ_56 SB_DQ_57 SB_DQ_58 SB_DQ_59 SB_DQ_60 SB_DQ_61 SB_DQ_62 SB_DQ_63

SB_BS_0 SB_BS_1 SB_BS_2 SB_RAS# SB_CAS# SB_W E#

BC16 BB17 BB33 AU17 BG16 BF14

M_B_BS0 19 M_B_BS1 19 M_B_BS2 19 M_B_RAS# 19 M_B_CAS# 19 M_B_WE# 19

M_B_DM[7..0]

SB_DM_0 SB_DM_1 SB_DM_2 SB_DM_3 SB_DM_4 SB_DM_5 SB_DM_6 SB_DM_7 SB_DQS_0 SB_DQS_1 SB_DQS_2 SB_DQS_3 SB_DQS_4 SB_DQS_5 SB_DQS_6 SB_DQS_7 SB_DQS#_0 SB_DQS#_1 SB_DQS#_2 SB_DQS#_3 SB_DQS#_4 SB_DQS#_5 SB_DQS#_6 SB_DQS#_7 SB_MA_0 SB_MA_1 SB_MA_2 SB_MA_3 SB_MA_4 SB_MA_5 SB_MA_6 SB_MA_7 SB_MA_8 SB_MA_9 SB_MA_10 SB_MA_11 SB_MA_12 SB_MA_13 SB_MA_14

AM47 AY47 BD40 BF35 BG11 BA3 AP1 AK2 AL47 AV48 BG41 BG37 BH9 BB2 AU1 AN6 AL46 AV47 BH41 BH37 BG9 BC2 AT2 AN5 AV17 BA25 BC25 AU25 AW 25 BB28 AU28 AW 28 AT33 BD33 BB16 AW 33 AY33 BH15 AU33

M_B_DM0 M_B_DM1 M_B_DM2 M_B_DM3 M_B_DM4 M_B_DM5 M_B_DM6 M_B_DM7 M_B_DQS[7..0] M_B_DQS0 M_B_DQS1 M_B_DQS2 M_B_DQS3 M_B_DQS4 M_B_DQS5 M_B_DQS6 M_B_DQS7 M_B_DQS#0 M_B_DQS#1 M_B_DQS#2 M_B_DQS#3 M_B_DQS#4 M_B_DQS#5 M_B_DQS#6 M_B_DQS#7 M_B_A0 M_B_A1 M_B_A2 M_B_A3 M_B_A4 M_B_A5 M_B_A6 M_B_A7 M_B_A8 M_B_A9 M_B_A10 M_B_A11 M_B_A12 M_B_A13 M_B_A14

M_B_DM[7..0]

19

M_B_DQS[7..0]

19

MEMORY

MEMORY

M_B_DQS#[7..0]

M_B_DQS#[7..0]

19

C

M_B_A[14..0]

M_B_A[14..0]

19

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

5 4 3 2

Cantiga-DDR(3/6)

Sheet

1

Rev

DJ1 Montevina UMA

12 of 88

A00

Friday, February 26, 2010

SSID = MCH

NB1I AU48 AR48 AL48 BB47 AW47 AN47 AJ47 AF47 AD47 AB47 Y47 T47 N47 L47 G47 BD46 BA46 AY46 AV46 AR46 AM46 V46 R46 P46 H46 F46 BF44 AH44 AD44 AA44 Y44 U44 T44 M44 F44 BC43 AV43 AU43 AM43 J43 C43 BG42 AY42 AT42 AN42 AJ42 AE42 N42 L42 BD41 AU41 AM41 AH41 AD41 AA41 Y41 U41 T41 M41 G41 B41 BG40 BB40 AV40 AN40 H40 E40 AT39 AM39 AJ39 AE39 N39 L39 B39 BH38 BC38 BA38 AU38 AH38 AD38 AA38 Y38 U38 T38 J38 F38 C38 BF37 BB37 AW37 AT37 AN37 AJ37 H37 C37 BG36 BD36 AK15 AU36 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS 9 OF 10 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS AM36 AE36 P36 L36 J36 F36 B36 AH35 AA35 Y35 U35 T35 BF34 AM34 AJ34 AF34 AE34 W34 B34 A34 BG33 BC33 BA33 AV33 AR33 AL33 AH33 AB33 P33 L33 H33 N32 K32 F32 C32 A31 AN29 T29 N29 K29 H29 F29 A29 BG28 BD28 BA28 AV28 AT28 AR28 AJ28 AG28 AE28 AB28 Y28 P28 K28 H28 F28 C28 BF26 AH26 AF26 AB26 AA26 C26 B26 BH25 BD25 BB25 AV25 AR25 AJ25 AC25 Y25 N25 L25 J25 G25 E25 BF24 AD12 AY24 AT24 AJ24 AH24 AF24 AB24 R24 L24 K24 J24 G24 F24 E24 BH23 AG23 Y23 B23 A23 AJ6 BG21 L12 AW21 AU21 AP21 AN21 AH21 AF21 AB21 R21 M21 J21 G21 BC20 BA20 AW20 AT20 AJ20 AG20 Y20 N20 K20 F20 C20 A20 BG19 A18 BG17 BC17 AW17 AT17 R17 M17 H17 C17 BA16 AU16 AN16 N16 K16 G16 E16 BG15 AC15 W15 A15 BG14 AA14 C14 BG13 BC13 BA13 AN13 AJ13 AE13 N13 L13 G13 E13 BF12 AV12 AT12 AM12 AA12 J12 A12 BD11 BB11 AY11 AN11 AH11 Y11 N11 G11 C11 BG10 AV10 AT10 AJ10 AE10 AA10 M10 BF9 BC9 AN9 AM9 AD9 G9 B9 BH8 BB8 AV8 AT8 NB1J VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS 10 OF 10 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS AH8 Y8 L8 E8 B8 AY7 AU7 AN7 AJ7 AE7 AA7 N7 J7 BG6 BD6 AV6 AT6 AM6 M6 C6 BA5 AH5 AD5 Y5 L5 J5 H5 F5 BE4 BC3 AV3 AL3 R3 P3 F3 BA2 AW2 AU2 AR2 AP2 AJ2 AH2 AF2 AE2 AD2 AC2 Y2 M2 K2 AM1 AA1 P1 H1 U24 U28 U25 U29 AF32 AB32 V32 AJ30 AM29 AF29 AB29 U26 U23 AL20 V20 AC19 AL17 AJ17 AA17 U17 BH48 BH1 A48 C1 A3 E1 D2 C3 B4 A5 A6 A43 A44 B45 C46 D47 B47 A46 F48 E48 C48 B48 GMCH_GND1 GMCH_GND2 GMCH_GND3 GMCH_GND4 +1.05V_VCCP 2 54 LBKLT_CTL 37 GMCH_BL_ON RN1302 +3.3V_RUN +3.3V_RUN RN1301 1 2 4 3 SRN2K2J-1-GP LDDC_CLK LDDC_DATA 54 54 4 3 1 2 SRN10KJ-5-GP LDDC_CLK LDDC_DATA L_CTRL_CLK L_CTRL_DATA L32 G32 M32 M33 K33 J33 M29 C44 B43 E37 E38 C41 C40 B37 A37 H47 E46 G40 A40 H48 D45 F40 B40 A41 H38 G37 J37 B42 G38 F37 K37 NB1C 3 OF 10 R1303 49D9R2F-GP 1

L_BKLT_CTRL L_BKLT_EN L_CTRL_CLK L_CTRL_DATA L_DDC_CLK L_DDC_DATA L_VDD_EN LVDS_IBG LVDS_VBG LVDS_VREFH LVDS_VREFL LVDSA_CLK# LVDSA_CLK LVDSB_CLK# LVDSB_CLK LVDSA_DATA#_0 LVDSA_DATA#_1 LVDSA_DATA#_2 LVDSA_DATA#_3 LVDSA_DATA_0 LVDSA_DATA_1 LVDSA_DATA_2 LVDSA_DATA_3 LVDSB_DATA#_0 LVDSB_DATA#_1 LVDSB_DATA#_2 LVDSB_DATA#_3 LVDSB_DATA_0 LVDSB_DATA_1 LVDSB_DATA_2 LVDSB_DATA_3

Place R1303 close to MCH within 500 mils.

PEG_COMPI PEG_COMPO PEG_RX#_0 PEG_RX#_1 PEG_RX#_2 PEG_RX#_3 PEG_RX#_4 PEG_RX#_5 PEG_RX#_6 PEG_RX#_7 PEG_RX#_8 PEG_RX#_9 PEG_RX#_10 PEG_RX#_11 PEG_RX#_12 PEG_RX#_13 PEG_RX#_14 PEG_RX#_15 PEG_RX_0 PEG_RX_1 PEG_RX_2 PEG_RX_3 PEG_RX_4 PEG_RX_5 PEG_RX_6 PEG_RX_7 PEG_RX_8 PEG_RX_9 PEG_RX_10 PEG_RX_11 PEG_RX_12 PEG_RX_13 PEG_RX_14 PEG_RX_15 PEG_TX#_0 PEG_TX#_1 PEG_TX#_2 PEG_TX#_3 PEG_TX#_4 PEG_TX#_5 PEG_TX#_6 PEG_TX#_7 PEG_TX#_8 PEG_TX#_9 PEG_TX#_10 PEG_TX#_11 PEG_TX#_12 PEG_TX#_13 PEG_TX#_14 PEG_TX#_15 PEG_TX_0 PEG_TX_1 PEG_TX_2 PEG_TX_3 PEG_TX_4 PEG_TX_5 PEG_TX_6 PEG_TX_7 PEG_TX_8 PEG_TX_9 PEG_TX_10 PEG_TX_11 PEG_TX_12 PEG_TX_13 PEG_TX_14 PEG_TX_15

T37 T36 H44 J46 L44 L40 N41 P48 N44 T43 U43 Y43 Y48 Y36 AA43 AD37 AC47 AD39 H43 J44 L43 L41 N40 P47 N43 T42 U42 Y42 W47 Y37 AA42 AD36 AC48 AD40 J41 M46 M47 M40 M42 R48 N38 T40 U37 U40 Y40 AA46 AA37 AA40 AD43 AC46 J42 L46 M48 M39 M43 R47 N37 T39 U36 U39 Y39 Y46 AA36 AA39 AD42 AD46

PEG_CMP

54 LCDVDD_EN 2 R1302 1 2K37R2F-GPTP1302

LIBG LVDS_VBG 1 Do Not Stuff

54 VGA_TXACLK54 VGA_TXACLK+

LVDS

54 VGA_TXAOUT054 VGA_TXAOUT154 VGA_TXAOUT254 VGA_TXAOUT0+ 54 VGA_TXAOUT1+ 54 VGA_TXAOUT2+

VSS

VSS

R1301 1 R1305 1 R1306 1

2 75R2F-2-GP 2 75R2F-2-GP 2 75R2F-2-GP

TV_DACA TV_DACB TV_DACC

F25 H25 K25 H24

TVA_DAC TVB_DAC TVC_DAC TV_RTN

PCI-EXPRESS

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_NCTF VSS_SCB VSS_SCB VSS_SCB VSS_SCB VSS_SCB NC#E1 NC#D2 NC#C3 NC#B4 NC#A5 NC#A6 NC#A43 NC#A44 NC#B45 NC#C46 NC#D47 NC#B47 NC#A46 NC#F48 NC#E48 NC#C48 NC#B48

GRAPHICS

TV

C31 E32

TV_DCONSEL_0 TV_DCONSEL_1

55 55 55

M_BLUE M_GREEN M_RED

M_BLUE M_GREEN M_RED 1 R1307 1 R1308 1 R1309 2 150R2F-1-GP 2 150R2F-1-GP

E28 G28 J28 2 150R2F-1-GP G29 H32 J32 J29 E29 L29

CRT_BLUE CRT_GREEN CRT_RED

VSS NCTF

VGA

CRT_IRTN CRT_DDC_CLK CRT_DDC_DATA CRT_HSYNC CRT_TVO_IREF CRT_VSYNC

CRT_IREF routing Trace width use 20 mil.

55 GMCH_HSYNC 55 GMCH_VSYNC

33R2J-2-GP 1 R1310 1K02R2F-1-GP1 R1311 33R2J-2-GP 1 R1312

2 2 2

GMCH_DDCCLK GMCH_DDCDATA GMCH_HS CRT_IREF GMCH_VS

VSS SCB

TP1303 TP1304 TP1301 TP1305

NCTF PIN

CANTIGA-GM-GP-U-NF

+3.3V_RUN RN1303 3 4 +3.3V_RUN SRN2K2J-1-GP 2 1

NC

U1301 GMCH_DDCDATA 4 5 55 DDC_CLK_CON DDC_CLK_CON 6 3 2 1 2N7002EDW-GP GMCH_DDCCLK DDC_DATA_CON DDC_DATA_CON 55

CANTIGA-GM-GP-U-NF CANTIGA-GM-GP-U-NF

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

5 4 3 2

Cantiga-GND/LVDS/VGA(4/6)

DJ1 Montevina UMA

Sheet

1

Rev

A00

of 88

Friday, February 26, 2010

13

SSID = MCH

NB1F +1.05V_VCCP C1427 SC10U6D3V5KX-1GP +1.05V_VCCP +1.5V_SUS NB1G 7 OF 10 6 OF 10

Close to (G)MCH

POWER

On the edge

AP33 AN33 BH32 BG32 BF32 BD32 BC32 BB32 BA32 AY32 AW 32 AV32 AU32 AT32 AR32 AP32 AN32 BH31 BG31 BF31 BG30 BH29 BG29 BF29 BD29 BC29 BB29 BA29 AY29 AW 29 AV29 AU29 AT29 AR29 AP29 BA36 BB24 BD16 BB21 AW 16 AW 13 AT13

VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM VCC_SM

VCC GFX NCTF

+1.05V_VCCP

VCC_SM/NC VCC_SM/NC VCC_SM/NC VCC_SM/NC VCC_SM/NC VCC_SM/NC VCC_SM/NC

VCC SM LF

Y26 AE25 AB25 AA25 AE24 AC24 AA24 Y24 AE23 AC23 AB23 AA23 AJ21 AG21 AE21 AC21 AA21 Y21 AH20 AF20 AE20 AC20 AB20 AA20 T17 T16 AM15 AL15 AE15 AJ15 AH15 AG15 AF15 AB15 AA15 Y15 V15 U15 AN14 AM14 U14 T14

VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG VCC_AXG

+1.05V_VCCP +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP

VCCA_MPLL VCCD_HPLL VCCA_PEG_PLL VCCD_PEG_PLL VCC_AXF VCCD_TVDAC VCC_SM VCC_SM_CK VCCA_PEG_BG VCC_HV

139.2mA 157.2mA 50mA 50mA 321.35mA 35mA 3000mA 124mA 414uA 105.3mA

VCC NCTF

VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF VCC_AXG_NCTF

W 28 V28 W 26 V26 W 25 V25 W 24 V24 W 23 V23 AM21 AL21 AK21 W 21 V21 U21 AM20 AK20 W 20 U20 AM19 AL19 AK19 AJ19 AH19 AG19 AF19 AE19 AB19 AA19 Y19 W 19 V19 U19 AM17 AK17 AH17 AG17 AF17 AE17 AC17 AB17 Y17 W 17 V17 AM16 AL16 AK16 AJ16 AH16 AG16 AF16 AE16 AC16 AB16 AA16 Y16 W 16 V16 U16

SC1U6D3V2KX-GP C1408 2 1

AG34 AC34 AB34 AA34 Y34 V34 U34 AM33 AK33 AJ33 AG33 AF33 AE33 AC33 AA33 Y33 W 33 V33 U33 AH28 AF28 AC28 AA28 AJ26 AG26 AE26 AC26 AH25 AG25 AF25 AG24 AJ23 AH23 AF23 T32

VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

C1405 SC1U6D3V2KX-GP

C1402 SCD1U10V2KX-5GP

C1403 SC1U6D3V2KX-GP

3060mA

POWER

Coupling CAP

1

C1414 SCD1U10V2KX-5GP C1412 SC10U6D3V5KX-1GP C1411 SCD1U10V2KX-5GP

DY

2

Coupling CAP

VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

C1424 SC10U6D3V5KX-1GP

C1425 SCD1U16V2KX-3GP

C1423 SCD1U16V2KX-3GP

C1413 SC1U10V3KX-3GP

TC1401 Do Not Stuff

VCC SM

C1426 SCD1U16V2KX-3GP

VCC CORE

3000mA

SC22U6D3V5MX-2GP C1415

SC22U6D3V5MX-2GP C1416

+1.05V_VCCP

Supply +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP +1.05V_VCCP

Signal Group VCC VTT VCC_PEG VCC_DMI VCCA_SM VCCA_SM_CK VCCA_HPLL

Imax 3060mA 852mA 1782mA 456mA 720mA 26mA 24mA

+1.5V_RUN +1.8V_SUS +1.8V_SUS +1.5V_RUN +3.3V_RUN

VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF VCC_NCTF

AM32 AL32 AK32 AJ32 AH32 AG32 AE32 AC32 AA32 Y32 W 32 U32 AM30 AL30 AK30 AH30 AG30 AF30 AE30 AC30 AB30 AA30 Y30 W 30 V30 U30 AL29 AK29 AJ29 AH29 AG29 AE29 AC29 AA29 Y29 W 29 V29 AL28 AK28 AL26 AK26 AK25 AK24 AK23

C1429 SCD1U16V2KX-3GP 2 1

C1428 SC4D7U6D3V5KX-3GP 2 1

C1430 SCD1U10V2KX-5GP

VCC GFX

C1401 SCD22U10V2KX-1GP

C1419 SCD22U10V2KX-1GP

C1420 SCD47U6D3V2KX-GP

C1421 SC1U10V3KX-3GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C1422 SC1U10V3KX-3GP

C1417 2 1

C1418 2 1

8700mA

VCC_SM_LF VCC_SM_LF VCC_SM_LF VCC_SM_LF VCC_SM_LF VCC_SM_LF VCC_SM_LF AV44 SM_LF1_GMCH BA37 SM_LF2_GMCH AM40 SM_LF3_GMCH AV21 SM_LF4_GMCH AY5 SM_LF5_GMCH AM10 SM_LF6_GMCH BB13 SM_LF7_GMCH

1 2

CANTIGA-GM-GP-U-NF

DJ1

TP1401 TP1402

VCC_AXG_SENSE VSS_AXG_SENSE

AJ14 AH14

VCC_AXG_SENSE VSS_AXG_SENSE

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

CANTIGA-GM-GP-U-NF

Cantiga-Power(5/6)

DJ1 Montevina UMA

Sheet

1

Rev

A00

of 88

Wednesday, February 24, 2010

14

+1.05V_VCCP R1502 C1502 SCD1U16V2KX-3GP C1503 SCD1U16V2KX-3GP

SSID = MCH

2 1

M_VCCA_DPLLA

Do Not Stuff

C1505 SCD01U16V2KX-3GP

DY

2

C1504 Do Not Stuff

+3.3V_CRT_LDO

R1503

2 1

Do Not Stuff

3D3V_CRTDAC_S0

+1.05V_VCCP NB1H 8 OF 10 C1508 SC1U10V3KX-3GP C1509 SC1U10V3KX-3GP C1510 SC1U10V3KX-3GP C1507 SCD1U16V2KX-3GP EC1501 SC1U10V3KX-3GP TC1501 Do Not Stuff

1

C1506 SCD1U10V2KX-5GP

R1504 C1511 SCD1U16V2KX-3GP C1512 SCD1U16V2KX-3GP

2 1

Do Not Stuff

M_VCCA_DPLLB

+3.3V_CRT_LDO C1513 Do Not Stuff

DY

2

C1514 SCD01U16V2KX-3GP

R1505

VCCA_DAC_BG VSSA_DAC_BG

CRT

2 1

Do Not Stuff

M_VCCA_DAC_BG

B27 A26 A25 B25

VCCA_CRT_DAC VCCA_CRT_DAC

SC1U6D3V2KX-GP 1 2

852mA

M_VCCA_DPLLB M_VCCA_HPLL M_VCCA_MPLL

L48 AD1 AE1 J48 J47

VCCA_DPLLB

C1516 SC4D7U6D3V3KX-GP

C1517 SCD1U10V2KX-5GP +1.5V_RUN R1508

VSSA_LVDS

A LVDS

120ohm 100MHz

L1502 1 2 BLM18PG121SN1D-GP

VCCA_MPLL 139.2mA VCCA_LVDS 13.2mA

PLL

VCCA_HPLL 24mA

M_VCCA_HPLL

G9091-180T11U-GP

C1518 SC1KP50V2KX-1GP

74.09091.G3F

2 1

Do Not Stuff C1519 SCD1U10V2KX-5GP

VCCA_PEG_BG

AD48

VCCA_PEG_BG

R1509 1D05V_VCC_AXF C1522 SC1U10V3KX-3GP

+1.05V_VCCP

414uA

A PEG

Do Not Stuff 2 1

L1501 1 2 BLM18PG121SN1D-GP

1 1

2

C

C1521

DY

SCD1U10V2KX-5GP

C1520

120ohm 100MHz

+1.05V_VCCP R1510 C1524 SC22U6D3V5MX-2GP

1D05V_RUN_PEGPLL 1D05V_SM C1525 SC4D7U6D3V3KX-GP C1526 SC1U10V3KX-3GP

AA48 AR20 AP20 AN20 AR17 AP17 AN17 AT16 AR16 AP16

VCCA_PEG_PLL 50mA VCCA_SM VCCA_SM VCCA_SM VCCA_SM VCCA_SM VCCA_SM VCCA_SM VCCA_SM VCCA_SM

M_VCCA_MPLL

Do Not Stuff

2

TC1502 Do Not Stuff C1501 Do Not Stuff Do Not Stuff

DY

DY

POWER

A SM

1D8V_VCC_SM_CK

DY C1523 Stuff Do Not

R1511

+1.5V_SUS

1 2

SCD1U10V2KX-5GP

2

Do Not Stuff

+1.05V_VCCP L1503 SC10U6D3V5KX-1GP 2 1

+1.05V_VCCP R1513 1D05V_RUN_PEGPLL

C1534 Do Not Stuff

2 1

Do Not Stuff

C1530 SC22U6D3V5MX-2GP

1D05V_SM_CK C1531 SCD1U10V2KX-5GP

1 1

1 2 BLM18BB221SN1D-GP

C1532 2 1

R1512 1R3F-GP C1535 SC10U6D3V3MX-GP

C1529 SCD1U10V2KX-5GP

C1533

321.35mA

220ohm 100MHz

DY

C1537

L1504 C1540 SCD01U16V2KX-3GP

+1.5V_RUN

SM CK

Do Not Stuff

C1538 Do Not Stuff

124mA

R1515

1 1 2 1

PBY160808T-181Y-GP 1D5VRUN_QDAC

2

Do Not Stuff

VCC_SM_CK VCC_SM_CK VCC_SM_CK VCC_SM_CK

BF21 BH20 BG20 BF20

1D8V_TXLVDS_S3

C1536 SC1KP50V2KX-1GP

+3.3V_CRT_LDO

+3.3V_TV_DAC

AP28 AN28 AP25 AN25 AN24 AM28 AM26 AM25 AL25 AM24 AL24 AM23 AL23

DY

2

DY

VCCA_SM_CK VCCA_SM_CK VCCA_SM_CK VCCA_SM_CK VCCA_SM_CK VCCA_SM_CK_NCTF VCCA_SM_CK_NCTF VCCA_SM_CK_NCTF VCCA_SM_CK_NCTF VCCA_SM_CK_NCTF VCCA_SM_CK_NCTF VCCA_SM_CK_NCTF VCCA_SM_CK_NCTF

AXF

VCC_AXF VCC_AXF VCC_AXF

B22 B21 A21

A CK

R1514

+1.8V_NB_S0

2

Do Not Stuff +3.3V_RUN R1523 +3.3V_VCC_HV

B

C1539 SC22U6D3V5MX-2GP

2

Do Not Stuff +3.3V_VCC_HV

C1559 2 1

C1560 SCD01U16V2KX-3GP

SCD1U10V2KX-5GP

+1.05V_VCCP

HDA

Do Not Stuff

VCC_HDA

A32

VCC_HDA 50mA

C1544 SC10U6D3V5KX-1GP

C1545 SC10U6D3V5KX-1GP

C1543 SC4D7U6D3V3KX-GP

M25

1D5VRUN_QDAC 1D05V_RUN_HPLL 1D05V_RUN_PEGPLL

VCCD_TVDAC 35mA VCCD_QDAC 2mA VCCD_HPLL 157.2mA VCCD_PEG_PLL 50mA VCCD_LVDS VCCD_LVDS

D TV/CRT

+1.05V_VCCP +5V_RUN

R1520

L28 AF1 AA47 M38 L37

456mA

DMI

2

Do Not Stuff

VCC_DMI VCC_DMI VCC_DMI VCC_DMI

AH48 AF48 AH47 AG47

1D05V_VCC_DMI

C1546 SC10U6D3V5KX-1GP

VCC_PEG VCC_PEG VCC_PEG VCC_PEG VCC_PEG

PEG

1782mA

V48 U48 V47 U47 U46

R1501

+1.05V_VCCP

SCD1U10V2KX-5GP 2 1

C1548

U1502

VTTLF

LVDS

C1549 SC1U10V3KX-3GP

C1547 SCD1U10V2KX-5GP

2

Do Not Stuff

C1551 SCD47U6D3V2KX-GP

C1552 SCD47U6D3V2KX-GP

R1521

C1553 SCD47U6D3V2KX-GP

+3.3V_CRT_LDO

1 2 3 4 5 1

EN GND VIN VOUT NC#5

60.31mA

VTTLF VTTLF VTTLF

A8 L1 AB2

VTTLF1 VTTLF2 VTTLF3

C1550 SCD1U10V2KX-5GP

A

DJ1

+1.8V_NB_S0

CANTIGA-GM-GP-U-NF R1522 1

74.09091.H3F Second = 74.09198.07F Reserved for CRT ripple

5

C1554 G9091-330T12U-GP SC10U6D3V5KX-1GP

2

Do Not Stuff

1D8V_SUS_DLVDS

1 2

1 2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size Document Number Custom Date:

1

C1555 SCD1U10V2KX-5GP

2

Do Not Stuff

VCC_HDA

Cantiga-Power/Filter(6/6)

DJ1 Montevina UMA

Sheet

1

VCCD_TVDAC

C1542 SCD1U10V2KX-5GP

R1516

105.3mA

TV

C1541 SCD1U10V2KX-5GP

+1.5V_RUN

B24 A24

118.8mA VCC_TX_LVDS

VCC_HV VCC_HV VCC_HV

K47 C35 B35 A35

HV

VCCA_TV_DAC VCCA_TV_DAC

Rev

A00

of 88

Wednesday, February 24, 2010

15

C1558

1D8V_TXLVDS_S3

1 2 3 4 5

VIN GND EN NC#4 VOUT

SC1U6D3V2KX-GP 1 2

VTT

+1.05V_VCCP

C1515 SCD1U10V2KX-5GP M_VCCA_DPLLA

F47

VCCA_DPLLA

VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT VTT

U13 T13 U12 T12 U11 T11 U10 T10 U9 T9 U8 T8 U7 T7 U6 T6 U5 T5 V3 U3 V2 U2 T2 V1 U1

DY

NB:180mA

+3.3V_RUN

I=300mA

U1501

+1.8V_NB_S0

C1557

64.8mA 37.5mA 79mA

720mA

(Blanking)

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size A3 Date:

5 4 3 2

Document Number

Reserved

Sheet

1

Rev

DJ1 Montevina UMA

W ednesday, February 24, 2010 16 of 88

A00

(Blanking)

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Size A3 Date:

5 4 3 2

Document Number

Reserved

Sheet

1

Rev

DJ1 Montevina UMA

W ednesday, February 24, 2010 17 of 88

A00

M_A_DM[7..0] 12 M_A_DQS#[7..0] 12 M_A_DQS[7..0] 12 NP1 NP2 110 113 115 114 121 73 74 101 103 102 104 11 28 46 63 136 153 170 187 200 202 198 199 197 201 77 122 125 75 76 81 82 87 88 93 94 99 100 105 106 111 112 117 118 123 124 2 3 8 9 13 14 19 20 25 26 31 32 37 38 43 44 48 49 54 55 60 61 65 66 71 72 127 128 133 134 138 139 144 145 150 151 155 156 161 162 167 168 172 173 178 179 184 185 189 190 195 196 205 206 SA0_DIM0 SA1_DIM0 C1801 SCD1U10V2KX-5GP +1.5V_SUS

C

DM1 M_A_A0 M_A_A1 M_A_A2 M_A_A3 M_A_A4 M_A_A5 M_A_A6 M_A_A7 M_A_A8 M_A_A9 M_A_A10 M_A_A11 M_A_A12 M_A_A13 M_A_A14 M_A_A15 98 97 96 95 92 91 90 86 89 85 107 84 83 119 80 78 79 109 108 M_A_DQ0 M_A_DQ1 M_A_DQ2 M_A_DQ3 M_A_DQ4 M_A_DQ5 M_A_DQ6 M_A_DQ7 M_A_DQ8 M_A_DQ9 M_A_DQ10 M_A_DQ11 M_A_DQ12 M_A_DQ13 M_A_DQ14 M_A_DQ15 M_A_DQ16 M_A_DQ17 M_A_DQ18 M_A_DQ19 M_A_DQ20 M_A_DQ21 M_A_DQ22 M_A_DQ23 M_A_DQ24 M_A_DQ25 M_A_DQ26 M_A_DQ27 M_A_DQ28 M_A_DQ29 M_A_DQ30 M_A_DQ31 M_A_DQ32 M_A_DQ33 M_A_DQ34 M_A_DQ35 M_A_DQ36 M_A_DQ37 M_A_DQ38 M_A_DQ39 M_A_DQ40 M_A_DQ41 M_A_DQ42 M_A_DQ43 M_A_DQ44 M_A_DQ45 M_A_DQ46 M_A_DQ47 M_A_DQ48 M_A_DQ49 M_A_DQ50 M_A_DQ51 M_A_DQ52 M_A_DQ53 M_A_DQ54 M_A_DQ55 M_A_DQ56 M_A_DQ57 M_A_DQ58 M_A_DQ59 M_A_DQ60 M_A_DQ61 M_A_DQ62 M_A_DQ63 M_A_DQS#0 M_A_DQS#1 M_A_DQS#2 M_A_DQS#3 M_A_DQS#4 M_A_DQS#5 M_A_DQS#6 M_A_DQS#7 M_A_DQS0 M_A_DQS1 M_A_DQS2 M_A_DQS3 M_A_DQS4 M_A_DQS5 M_A_DQS6 M_A_DQS7 11 11 +0.75V_DDR_VTT

A

M_A_A[14..0] 12

TP1801 12 M_A_BS2

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10/AP A11 A12 A13 A14 A15 A16/BA2 BA0 BA1 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 DQS0# DQS1# DQS2# DQS3# DQS4# DQS5# DQS6# DQS7# DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 ODT0 ODT1 VREF_CA VREF_DQ RESET# VTT1 VTT2 DDR3-204P-41-GP-U 62.10017.N41

NP1 NP2 RAS# WE# CAS# CS0# CS1# CKE0 CKE1 CK0 CK0# CK1 CK1# DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 SDA SCL EVENT# VDDSPD SA0 SA1 NC#1 NC#2 NC#/TEST VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDD9 VDD10 VDD11 VDD12 VDD13 VDD14 VDD15 VDD16 VDD17 VDD18 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

M_A_RAS# 12 M_A_WE# 12 M_A_CAS# 12 M_CS#0 11 M_CS#1 11 M_CKE0 11 M_CKE1 11

SA0_DIM0 SA1_DIM0 1 1

Note: If SA0 DIM0 = 0, SA1_DIM0 = 0 SO-DIMMA SPD Address is 0xA0 SO-DIMMA TS Address is 0x30

D

R1802 10KR2J-3-GP 2 2

R1803 10KR2J-3-GP

If SA0 DIM0 = 1, SA1_DIM0 = 0 SO-DIMMA SPD Address is 0xA2 SO-DIMMA TS Address is 0x32

M_CLK_DDR0 11 M_CLK_DDR#0 11 M_CLK_DDR1 11 M_CLK_DDR#1 11 M_A_DM0 M_A_DM1 M_A_DM2 M_A_DM3 M_A_DM4 M_A_DM5 M_A_DM6 M_A_DM7 ICH_SMBDATA 7,19,22,76 ICH_SMBCLK 7,19,22,76 PM_EXTTS#0 11 +3.3V_RUN

12 M_A_BS0 12 M_A_BS1 12 M_A_DQ[63..0]

+V_DDR_REF 1

R1806 2 M_VREF_CA_DIMM0 1 1 C1812 SC2D2U6D3V3KX-GP

SCD1U10V2KX-5GP

Layout Note: Place these Caps near SO-DIMMA.

Do Not Stuff C1811

+V_DDR_REF

R1807 1 2 Do Not Stuff M_VREF_DQ_DIMM0 1 1 C1818 SC2D2U6D3V3KX-GP

C1817 SCD1U10V2KX-5GP

5 7 15 17 4 6 16 18 21 23 33 35 22 24 34 36 39 41 51 53 40 42 50 52 57 59 67 69 56 58 68 70 129 131 141 143 130 132 140 142 147 149 157 159 146 148 158 160 163 165 175 177 164 166 174 176 181 183 191 193 180 182 192 194 10 27 45 62 135 152 169 186 12 29 47 64 137 154 171 188 116 120

DY

2 2

C1802 Do Not Stuff

SODIMM A DECOUPLING

+1.5V_SUS

C1816 SCD1U10V2KX-5GP

DY

TC1801 C1803 Do Not Stuff C1813 SCD1U16V2KX-3GP SC10U10V5ZY-1GP

C1804 SC10U10V5ZY-1GP SC10U10V5ZY-1GP

C1805 SC10U10V5ZY-1GP

C1806 SC10U10V5ZY-1GP

C1807 SC10U10V5ZY-1GP SC10U10V5ZY-1GP

C1808 SC10U10V5ZY-1GP

C1814 SCD1U16V2KX-3GP

C1815 C1815 SCD1U16V2KX-3GP SCD1U16V2KX-3GP

Place between DM1 and DM2.

+0.75V_DDR_VTT

C1819 SC10U10V5ZY-1GP

C1824 Do Not Stuff

DY

M_ODT0 M_ODT1 M_VREF_CA_DIMM0 M_VREF_DQ_DIMM0

Place these caps close to VTT1 and VTT2.

1 1 1

126 1 30 203 204

11,19 DDR3_DRAMRST# +0.75V_DDR_VTT

DJ1

C1820 C1821 C1822 C1823 SC1U6D3V2KX-GP SC1U6D3V2KX-GP SC1U6D3V2KX-GP SC1U6D3V2KX-GP

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title

H =5.2mm

DDR3-SODIMM1

Size Date:

5 4 3 2

Document Number

Rev

DJ1 Montevina UMA

Friday, February 26, 2010

1

A00

of 88

Sheet

18

DM2 M_B_A0 M_B_A1 M_B_A2 M_B_A3 M_B_A4 M_B_A5 M_B_A6 M_B_A7 M_B_A8 M_B_A9 M_B_A10 M_B_A11 M_B_A12 M_B_A13 M_B_A14 M_B_A15 98 97 96 95 92 91 90 86 89 85 107 84 83 119 80 78 79 109 108 M_B_DQ0 M_B_DQ1 M_B_DQ2 M_B_DQ3 M_B_DQ4 M_B_DQ5 M_B_DQ6 M_B_DQ7 M_B_DQ8 M_B_DQ9 M_B_DQ10 M_B_DQ11 M_B_DQ12 M_B_DQ13 M_B_DQ14 M_B_DQ15 M_B_DQ16 M_B_DQ17 M_B_DQ18 M_B_DQ19 M_B_DQ20 M_B_DQ21 M_B_DQ22 M_B_DQ23 M_B_DQ24 M_B_DQ25 M_B_DQ26 M_B_DQ27 M_B_DQ28 M_B_DQ29 M_B_DQ30 M_B_DQ31 M_B_DQ32 M_B_DQ33 M_B_DQ34 M_B_DQ35 M_B_DQ36 M_B_DQ37 M_B_DQ38 M_B_DQ39 M_B_DQ40 M_B_DQ41 M_B_DQ42 M_B_DQ43 M_B_DQ44 M_B_DQ45 M_B_DQ46 M_B_DQ47 M_B_DQ48 M_B_DQ49 M_B_DQ50 M_B_DQ51 M_B_DQ52 M_B_DQ53 M_B_DQ54 M_B_DQ55 M_B_DQ56 M_B_DQ57 M_B_DQ58 M_B_DQ59 M_B_DQ60 M_B_DQ61 M_B_DQ62 M_B_DQ63 M_B_DQS#0 M_B_DQS#1 M_B_DQS#2 M_B_DQS#3 M_B_DQS#4 M_B_DQS#5 M_B_DQS#6 M_B_DQS#7 2 Do Not Stuff M_VREF_DQ_DIMM1 C1914 SC2D2U6D3V3KX-GP M_B_DQS0 M_B_DQS1 M_B_DQS2 M_B_DQS3 M_B_DQS4 M_B_DQS5 M_B_DQS6 M_B_DQS7 11 11 M_ODT2 M_ODT3 M_VREF_CA_DIMM1 M_VREF_DQ_DIMM1 +0.75V_DDR_VTT 11,18 DDR3_DRAMRST# 1 1 5 7 15 17 4 6 16 18 21 23 33 35 22 24 34 36 39 41 51 53 40 42 50 52 57 59 67 69 56 58 68 70 129 131 141 143 130 132 140 142 147 149 157 159 146 148 158 160 163 165 175 177 164 166 174 176 181 183 191 193 180 182 192 194 10 27 45 62 135 152 169 186 12 29 47 64 137 154 171 188 116 120 126 1 30 203 204 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10/AP A11 A12 A13 A14 A15 A16/BA2 BA0 BA1 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 DQS0# DQS1# DQS2# DQS3# DQS4# DQS5# DQS6# DQS7# DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 ODT0 ODT1 VREF_CA VREF_DQ RESET# VTT1 VTT2 DDR3-204P-40-GP-U 62.10017.N11 NP1 NP2 RAS# WE# CAS# CS0# CS1# CKE0 CKE1 CK0 CK0# CK1 CK1# DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 SDA SCL EVENT# VDDSPD SA0 SA1 NC#1 NC#2 NC#/TEST VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDD9 VDD10 VDD11 VDD12 VDD13 VDD14 VDD15 VDD16 VDD17 VDD18 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS NP1 NP2 110 113 115 114 121 73 74 101 103 102 104 11 28 46 63 136 153 170 187 200 202 198 199 1 197 201 77 122 125 75 76 81 82 87 88 93 94 99 100 105 106 111 112 117 118 123 124 2 3 8 9 13 14 19 20 25 26 31 32 37 38 43 44 48 49 54 55 60 61 65 66 71 72 127 128 133 134 138 139 144 145 150 151 155 156 161 162 167 168 172 173 178 179 184 185 189 190 195 196 205 206 SA0_DIM1 SA1_DIM1 C1901 SCD1U10V2KX-5GP +1.5V_SUS 1 M_B_DM0 M_B_DM1 M_B_DM2 M_B_DM3 M_B_DM4 M_B_DM5 M_B_DM6 M_B_DM7 ICH_SMBDATA 7,18,22,76 ICH_SMBCLK 7,18,22,76 PM_EXTTS#1 11 +3.3V_RUN M_B_RAS# 12 M_B_WE# 12 M_B_CAS# 12 M_CS#2 11 M_CS#3 11 M_CKE2 11 M_CKE3 11 M_CLK_DDR2 11 M_CLK_DDR#2 11 M_CLK_DDR3 11 M_CLK_DDR#3 11 M_B_DM[7..0] 12 M_B_DQS#[7..0] 12 M_B_DQS[7..0] 12 M_B_A[14..0] 12 2 SA1_DIM1

D

+3.3V_RUN

1 R1901 10KR2J-3-GP SA0_DIM1 1 R1902 10KR2J-3-GP 2

TP1901 12 M_B_BS2

12 M_B_BS0 12 M_B_BS1 12 M_B_DQ[63..0]

DY

2 2

C1902 Do Not Stuff

Note: SO-DIMMB SPD Address is 0xA4 SO-DIMMB TS Address is 0x34 SO-DIMMB is placed farther from the Processor than SO-DIMMA

SODIMM B DECOUPLING

+1.5V_SUS

+V_DDR_REF

B

R1906 1 2 Do Not Stuff M_VREF_CA_DIMM1 1 1 C1904 SC2D2U6D3V3KX-GP

Layout Note: Place these Caps near SO-DIMMB.

DY

B

+V_DDR_REF 1

R1907

C1913 SCD1U10V2KX-5GP

C1903 SCD1U10V2KX-5GP

C1915 SCD1U10V2KX-5GP

C1916 SCD1U10V2KX-5GP

C1917 SCD1U10V2KX-5GP

C1918 Do Not Stuff

DY

TC1901 C1810 Do Not Stuff SC10U10V5ZY-1GP

C1906 SC10U10V5ZY-1GP

C1907 SC10U10V5ZY-1GP

C1908 SC10U10V5ZY-1GP

C1809 SC10U10V5ZY-1GP

C1911 SC10U6D3V5KX-1GP

Place these caps close to VTT1 and VTT2.

H = 9.2mm

C1919 C1920 C1921 C1922 SC1U6D3V2KX-GP SC1U6D3V2KX-GP SC1U6D3V2KX-GP SC1U6D3V2KX-GP

DJ1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title

DDR3-SODIMM2

Size Date:

5 4 3 2

Document Number

Rev

DJ1 Montevina UMA

Friday, February 26, 2010

1

A00

of 88

Sheet

19

SSID = ICH

ICH_RTCX1 R2002 1 X2001

2 10MR2J-L-GP

ICH_RTCX2

4 1

C2002

1 1

C2001

SC15P50V2JN-2-GP

SC15P50V2JN-2-GP

X-32D768KHZ-46GP

+RTC_CELL R2003

2nd 82.30001.A81

SB1A

1 OF 6

LPC_LAD[0..3]

LPC_LAD[0..3]

37,58

2 1 2

ICH_RTCRST# ICH_RTCRST# SRTCRST# SM_INTRUDER# ICH_INTVRMEN LAN100_SLP

C23 C24 A25 F20 C22 B22 A22 E25

RTCX1 RTCX2

RTC LPC

20KR2F-L-GP C2003 SC1U10V3KX-3GP

G2001 Do Not Stuff

RTCRST# SRTCRST# INTRUDER# INTVRMEN LAN100_SLP GLAN_CLK LAN_RSTSYNC LAN_RXD0 LAN_RXD1 LAN_RXD2 LAN_TXD0 LAN_TXD1 LAN_TXD2 GLAN_DOCK#/GPIO56 GLAN_COMPI GLAN_COMPO HDA_BIT_CLK HDA_SYNC HDA_RST#

FW H0/LAD0 FW H1/LAD1 FW H2/LAD2 FW H3/LAD3 FW H4/LFRAME# LDRQ0# LDRQ1#/GPIO23 A20GATE A20M#

K5 K4 L6 K2 K3 J3 J1 N7 AJ27 AJ25 AE23 AJ26 AD22 AF25 AE22 AG25 L3 AF23 AF24 AH27 AG26 AG27 AH11 AJ11 AG12 AF12 AH9 AJ9 AE10 AF10 AH18 AJ18 AJ7 AH7

LPC_LAD0 LPC_LAD1 LPC_LAD2 LPC_LAD3 LPC_LFRAME# 37,58 +3.3V_RUN R2001

DY

R2005

+RTC_CELL R2004

Do Not Stuff KA20GATE 37 H_A20M# 8 H_DPRSTP# H_FERR#_R H_DPRSTP# 8,11,47 H_DPSLP# 8 +1.05V_VCCP

C13 2

C2004 SC1U10V3KX-3GP

20KR2F-L-GP

F14 G13 D14 D13 D12 E13 2GPIO56

GLAN_COMP ACZ_BIT_CLK_R ACZ_SYNC_R ACZ_RST#_R

LAN / GLAN CPU

DPRSTP# DPSLP# FERR# CPUPW RGD IGNNE# INIT# INTR RCIN# NMI SMI# STPCLK# THRMTRIP#

56R2J-4-GP H_FERR# 8 +3.3V_RUN R2008

1 R2006

2 56R2J-4-GP

H_PWRGOOD 8,42 H_IGNNE# H_INIT# 8 H_INTR 8 H_NMI 8 H_SMI# 8 H_STPCLK# 8 8

+1.5V_RUN

R2007

Place within 500 mil of SB.

R2009 1

DY

B10 B28 B27 AF6 AH4 AE7 AF4 AG4 AH3 AE5

DY

Do Not Stuff KBRCIN# +1.05V_VCCP R2011 37

2 24D9R2F-L-GP

Do Not Stuff

30 ICH_AZ_CODEC_BITCLK 30 ICH_AZ_CODEC_SYNC 30 ICH_AZ_CODEC_RST#

R2010 R2012 R2015

1 1 1

2 2 2

33R2J-2-GP 33R2J-2-GP 33R2J-2-GP 30 ICH_SDIN_CODEC

1 1 R2014

2 56R2J-4-GP 2 Do Not Stuff

H_THRMTRIP# 8,11,37,42

H_THERMTRIP_R

IHDA

HDA_SDIN0 HDA_SDIN1 HDA_SDIN2 HDA_SDIN3 HDA_SDOUT

1 R2013

2 H_THERMTRIP_1 54D9R2F-L1-GP

PECI SATA4RXN SATA4RXP SATA4TXN SATA4TXP SATA5RXN SATA5RXP SATA5TXN SATA5TXP SATA_CLKN SATA_CLKP SATARBIAS# SATARBIAS

Placed Within 2" from SB.

A00

30 ICH_SDOUT_CODEC

R2016

33R2J-2-GP

ACZ_SDATAOUT_R

AG5 AG7 AE8

HDA_DOCK_EN#/GPIO33 HDA_DOCK_RST#/GPIO34 SATALED#

66

SATA_LED#

SATA_LED#

AG8 AJ16 AH16 AF17 AG17 AH13 AJ13 AG14 AF14

C2005 1 C2006 1

2 SCD01U50V2KX-1GP 2 SCD01U50V2KX-1GP

SATA_TXN0_C SATA_TXP0_C

SATA

HDD

B

59 59 59 59 59 59 59 59

SATA_RXN0_C SATA_RXP0_C SATA_TXN0 SATA_TXP0 SATA_RXN1_C SATA_RXP1_C SATA_TXN1 SATA_TXP1

SATA0RXN SATA0RXP SATA0TXN SATA0TXP SATA1RXN SATA1RXP SATA1TXN SATA1TXP

ICH9M-GP-NF

CLK_PCIE_SATA# 7 CLK_PCIE_SATA 7 SATARBIAS

B

ODD

C2007 1 C2008 1

2 SCD01U50V2KX-1GP 2 SCD01U50V2KX-1GP

SATA_TXN1_C SATA_TXP1_C

1 R2017

2 24D9R2F-L-GP

Place within 500 mils from SB.

2010/01/04

+RTC_CELL R2018

1

A

2

330KR2J-L1-GP R2019

ICH_INTVRMEN

integrated VccSus1_05,VccSus1_5,VccCL1_5

INTVRMEN

LAN100_SLP

High=Enable High=Enable

Low=Disable Low=Disable

ICH_AZ_CODEC_BITCLK

integrated VccLan1_05VccCL1_05

1 2

DJ1

LAN100_SLP

Wistron Corporation

EC2001 Do Not Stuff Title 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C.

330KR2J-L1-GP R2020

1

1MR2J-1-GP

SM_INTRUDER#

DY

Lay Out Close SB1

5 4 3 2

Size Document Number Custom Date:

ICH9-LAN/HDA/SATA/LPC(1/4)

DJ1 Montevina UMA

Sheet

1

Rev

A00

of 88

Friday, February 26, 2010

20

SSID = ICH

5 OF 6 SB1E

2 OF 6 SB1B

+3.3V_RUN

AA26 AA27 AA3 AA6 AB1 AA23 AB28 AB29 AB4 AB5 AC17 AC26 AC27 AC3 AD1 AD10 AD12 AD13 AD14 AD17 AD18 AD21 AD28 AD29 AD4 AD5 AD6 AD7 AD9 AE12 AE13 AE14 AE16 AE17 AE2 AE20 AE24 AE3 AE4 AE6 AE9 AF13 AF16 AF18 AF22 AH26 AF26 AF27 AF5 AF7 AF9 AG13 AG16 AG18 AG20 AG23 AG3 AG6 AG9 AH12 AH14 AH17 AH19 AH2 AH22 AH25 AH28 AH5 AH8 AJ12 AJ14 AJ17 AJ8 B11 B14 B17 B2 B20 B23 B5 B8 C26 C27 E11 E14 E18 E2 E21 E24 E5 E8 F16 F28 F29 G12 G14 G18 G21 G24 G26 G27 G8 H2 H23 H28 H29