Professional Documents

Culture Documents

CH 8

Uploaded by

Mustafa JumaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CH 8

Uploaded by

Mustafa JumaCopyright:

Available Formats

8-1.

Introduction

n

1 / 22

8-2. General Register Organization

u Binary selector input : R1 R 2 + R 3 l 1) MUX A selector (SELA) : to place the content of R2 into BUS A l 2) MUX B selector (SELB) : to place the content of R3 into BUS B l 3) ALU operation selector (OPR) : to provide the arithmetic addition R2 + R3 l 4) Decoder selector (SELD) : to transfer the content of the output bus into R1 u Control Word l 14 bit control word (4 fields) : Fig. 8-2(b)

l

3 / 22

8-1 Introduction

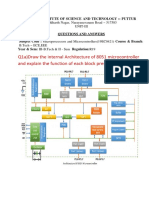

u 3 major parts of CPU : Fig. 8-1 l 1) Register Set l 2) ALU l 3) Control u Design Examples of simple CPU l Hardwired Control : Chap. 5 l Microprogrammed Control : Chap. 7

Computer Architecture as seen by the programmer u In this chapter : Chap. 8 l Describe the organization and architecture of the CPU with an emphasis on the user view of the computer s l User who programs the computer in machine/assembly language must be aware of 1) Instruction Formats 2) Addressing Modes 3) Register Sets

l

SELA (3 bits) : select a source register for the A input of the ALU SELB (3 bits) : select a source register for the B input of the ALU SELD (3 bits) : select a destination register using the 3 X 8 decoder OPR (5 bits) : select one of the operations in the ALU

Tab. 8-1 Tab. 8-2

Encoding of Register Selection Fields : Tab. 8-1

Chap. 8

The last section presents the concept of Reduced Instruction Set Computer (RISC)

Chap. 8 Central Processing Unit

SELA or SELB = 000 (Input) : MUX selects the external input data SELD = 000 (None) : no destination register is selected but the contents of the output bus are available in the external output Control Word Control Memory l Encoding of ALU Operation (OPR) : Tab. 8-2 Microprogrammed Control u Examples of Microoperations : Tab. 8-3

l l

TSFA (Transfer A) : R 7 R1, External Output R 2, External Output External Input XOR : R5 0 ( XOR R5 R 5)

Chap. 8 Central Processing Unit

Computer System Architecture

Computer System Architecture

8-2. General Register Organization

n

2 / 22

8-3. Stack Organization

n

4 / 22

8-2 General Register Organization

u Register l Memory locations are needed for storing pointers, counters, return address, temporary results, and partial products during multiplication (in the programming examples of Chap. 6) l Memory access is the most time-consuming operation in a computer l More convenient and efficient way is to store intermediate values in processor registers u Bus organization for 7 CPU registers : Fig. 8-2 l 2 MUX : select one of 7 register or external data input by SELA and SELB l BUS A and BUS B : form the inputs to a common ALU l ALU : OPR determine the arithmetic or logic microoperation

The result of the microoperation is available for external data output and also goes into the inputs of all the registers

l External Input

8-3 Stack Organization

u Stack or LIFO(Last-In, First-Out) l A storage device that stores information

The item stored last is the first item retrieved = a stack of tray

l

Clock R1 R2 R3 R4 R5 R6 R7 Load (7 lines) SELA MUX 38 decoder SELD OPR A bus

Input

Stack Pointer (SP)

The register that holds the address for the stack SP always points at the top item in the stack

Two Operations of a stack : Insertion and Deletion of Items

PUSH : Push-Down = Insertion POP : Pop-Up = Deletion

MUX B bus

SELB

l

Address 64 FULL EMTY 4 3 2 1 0

Stack

1) Register Stack (Stack Depth )

n

Arithmetic logic unit (ALU)

External Output

a finite number of memory words or register(stand alone) a portion of a large memory

2) Memory Stack (Stack Depth )

n

3 X 8 Decoder : select the register (by SELD) that receives the information from ALU

Chap. 8 Central Processing Unit

Output (a) Block diagram 3 3 3 5 SELASELBSELD OPR (b) Control word

u Register Stack : Fig. 8-3 l PUSH : SP SP + 1

* SP = 0, EMTY = 1, FULL = 0

Computer System Architecture

SP

Last Item

: Increment SP M [ SP ] DR : Write to the stack If ( SP = 0 ) then ( FULL 1) : Check if stack is full

C B A

EMTY 0

DR

: Mark not empty

Chap. 8 Central Processing Unit

Computer System Architecture

8-3. Stack Organization

The first item is stored at address 1, and the last item is stored at address 0

l

5 / 22

8-4. Instruction Formats

X = Operand Address u 3 types of CPU organizations AC AC + M [ X ] l 1) Single AC Org. : ADD X R1 R 2 + R 3 l 2) General Register Org. : ADD R1, R2, R3 l 3) Stack Org. : PUSH X TOS M [ X ]

7 / 22

POP : DR M [ SP ]

SP SP 1

: Read item from the top of stack

: Decrement Stack Pointer If ( SP = 0 ) then ( EMTY 1) : Check if stack is empty FULL 0 : Mark not full

PC

* Memory Stack PUSH = Address * Register Stack PUSH = Address Address Memory unit 1000 Program (instructions) 2000 Data (operands) 3000 Stack 3997 3998 3999 4000 4001

u Memory Stack : Fig. 8-4 l PUSH : SP SP 1

* SP = 4001 l

u The influence of the number of addresses on computer instruction [] X = (A + B)*(C + D) - 4 arithmetic operations : ADD, SUB, MUL, DIV - 1 transfer operation to and from memory and general register : MOV - 2 transfer operation to and from memory and AC register : STORE, LOAD - Operand memory addresses : A, B, C, D - Result memory address : X l 1) Three-Address Instruction

ADD ADD MUL R1, A, B R2, C, D X, R1, R2

M [ SP ] DR

The first item is stored at address 4000

AR

POP : DR M [ SP ]

SP SP + 1

* Error Condition PUSH when FULL = 1 POP when EMTY = 1

u Stack Limits l Check for stack overflow(full)/underflow(empty)

Checked by using two register

n

SP

R1 M [ A] + M [ B ] R 2 M [C ] + M [ D ] M [ X ] R1 R 2

Upper Limit and Lower Limit Register SP compared with the upper limit register SP compared with the lower limit register Chap. 8 Central Processing Unit

After PUSH Operation

n

Start Here

After POP Operation

n

DR

Each address fields specify either a processor register or a memory operand : Short program Require too many bit to specify 3 address y

Chap. 8 Central Processing Unit

Computer System Architecture

Computer System Architecture

8-4. Instruction Formats

6 / 22

l

8-4. Instruction Formats

2) Two-Address Instruction

MOV ADD MOV ADD MUL MOV R1, A R1, B R2, C R2, D R1, R2 X, R1

8 / 22

Stack Arithmetic u RPN (Reverse Polish Notation) l The common mathematical method of writing arithmetic expressions imposes difficulties when evaluated by a computer l A stack organization is very effective for evaluating arithmetic expressions l A * B + C * D AB * CD * + : Fig. 8-5 ) ( 3 * 4 ) + ( 5 * 6 ) 34 * 56 * +

R1 M [ A ] R1 R1 + M [ B ] R 2 M [C ] R2 R2 + M [D] R1 R1 R 2 M [ X ] R1

6 4 3 3 3 4 12 * 5 12 5 5 12 6 30 12 * 42 +

l

The most common in commercial computers Each address fields specify either a processor register or a memory operand

3) One-Address Instruction

LOAD ADD STORE LOAD ADD MUL STORE A B T C D T X

AC M [ A] AC A[C ] + M [ B ]

8-4 Instruction Formats

u Fields in Instruction Formats l 1) Operation Code Field : specify the operation to be performed l 2) Address Field : designate a memory address or a processor register l 3) Mode Field : specify the operand or the effective address (Addressing Mode)

M [T ] AC AC M [C ] AC AC + M [ D ] AC AC M [T ] M [ X ] AC

All operations are done between the AC register and memory operand

Computer System Architecture

Chap. 8 Central Processing Unit

Computer System Architecture

Chap. 8 Central Processing Unit

8-4. Instruction Formats

l

9 / 22

8-5. Addressing Modes

u Program Counter (PC) l PC keeps track of the instructions in the program stored in memory l PC holds the address of the instruction to be executed next l PC is incremented each time an instruction is fetched from memory u Addressing Mode of the Instruction l 1) Distinct Binary Code

Instruction Format Opcode Addressing Mode Field

l

11 / 22

4) Zero-Address Instruction

PUSH PUSH ADD PUSH PUSH ADD MUL POP X C D A B

TOS A TOS B TOS ( A + B ) TOS C TOS D TOS (C + D ) TOS (C + D ) ( A + B ) M [ X ] TOS

2) Single Binary Code

Instruction Format Opcode Addressing Mode Field

Stack-organized computer does not use an address field for the instructions ADD, and MUL PUSH, and POP instructions need an address field to specify the operand Zero-Address : absence of address ( ADD, MUL )

u Instruction Format with mode field : Fig. 8-6

Opcode Mode Address

u RISC Instruction l Only use LOAD and STORE instruction when communicating between memory and CPU l All other instructions are executed within the registers of the CPU without referring to memory l RISC architecture will be explained in Sec. 8-8

Computer System Architecture

u Implied Mode l Operands are specified implicitly in definition of the instruction l Examples

COM : Complement Accumulator

n

Operand in AC is implied in the definition of the instruction Operand is implied to be on top of the stack Chap. 8 Central Processing Unit

PUSH : Stack push

n

Chap. 8 Central Processing Unit

Computer System Architecture

8-5. Addressing Modes

l

10 / 22

8-5. Addressing Modes

u Immediate Mode l Operand field contains the actual operand l Useful for initializing registers to a constant value l Example : LD #NBR u Register Mode l Operands are in registers l Register is selected from a register field in the instruction

k-bit register field can specify any one of 2k registers

l

12 / 22

Program to evaluate X = ( A + B ) * ( C + D )

LOAD LOAD LOAD LOAD ADD ADD MUL STORE R1, A R2, B R3, C R4, D R1, R1, R2 R3, R3, R4 R1, R1, R3 X, R1

R1 M [ A] R2 M [B] R 3 M [C ] R4 M [D ] R1 R1 + R 2 R3 R3 + R4 R1 R1 R 3 M [ X ] R1

Example : LD R1

AC R1

Implied Mode

8-5 Addressing Modes

u Addressing Mode l 1) To give programming versatility to the user

pointers to memory, counters for loop control, indexing of data, .

l

u Register Indirect Mode l Selected register contains the address of the operand rather than the operand itself l : Address field of the instruction uses fewer bits to select a memory address

Register select bit

l

2) To reduce the number of bits in the addressing field of the instruction

u Instruction Cycle l 1) Fetch the instruction from memory and PC + 1 l 2) Decode the instruction l 3) Execute the instruction

Computer System Architecture

Example : LD (R1)

AC M [R1]

u Autoincrement or Autodecrement Mode l Similar to the register indirect mode except that

the register is incremented after its value is used to access memory the register is decrement before its value is used to access memory

Computer System Architecture

Chap. 8 Central Processing Unit

Chap. 8 Central Processing Unit

8-5. Addressing Modes

l

13 / 22

8-6. Data Transfer and Manipulation

n

15 / 22

Example (Autoincrement) : LD (R1)+

AC M [ R1], R1 R1 + 1

u Direct Addressing Mode l Effective address is equal to the address field of the instruction (Operand) l Address field specifies the actual branch address in a branch-type instruction AC M [ ADR ] l Example : LD ADR u Indirect Addressing Mode l Address field of instruction gives the address where the effective address is stored in memory AC M [ M [ ADR ]] l Example : LD @ADR u Relative Addressing Mode l PC is added to the address part of the instruction to obtain the effective address AC M [ PC + ADR ] l Example : LD $ADR u Indexed Addressing Mode l XR (Index register) is added to the address part of the instruction to obtain the effective address l Example : LD ADR(XR) AC M [ ADR + XR ] u Base Register Addressing Mode Not Here l the content of a base register is added to the address part of the instruction to obtain the effective address

Computer System Architecture

8-6 Data Transfer and Manipulation

u Most computer instructions can be classified into three categories: l 1) Data transfer, 2) Data manipulation, 3) Program control instructions u Data Transfer Instruction l Typical Data Transfer Instruction : Tab. 8-5

l

ADR = Address part of Instruction

Load : transfer from memory to a processor register, usually an AC (memory read) Store : transfer from a processor register into memory (memory write) Move : transfer from one register to another register Exchange : swap information between two registers or a register and a memory word Input/Output : transfer data among processor registers and input/output device Push/Pop : transfer data between processor registers and a memory stack @ : Indirect Address $ : Address relative to PC # : Immediate Mode ( ) : Index Mode, Register Indirect, Autoincrement - register

8 Addressing Mode for the LOAD Instruction : Tab. 8-6

u Data Manipulation Instruction l 1) Arithmetic, 2) Logical and bit manipulation, 3) Shift Instruction

Chap. 8 Central Processing Unit

Computer System Architecture

Chap. 8 Central Processing Unit

8-5. Addressing Modes

l

14 / 22

l l l

8-7. Program Control

Arithmetic Instructions : Tab. 8-7 Logical and Bit Manipulation Instructions : Tab. 8-8 Shift Instructions : Tab. 8-9

16 / 22

Similar to the indexed addressing mode except that the register is now called a base register instead of an index register

index register (XR) : LD ADR(XR)

n

AC M [ ADR + XR ] ADR index register hold an index number that is relative to the address part of the instruction AC M [ BR + ADR ]

BR

base register (BR) : LD ADR(BR)

n n

8-7 Program Control

u Program Control Instruction : Tab. 8-10 l Branch and Jump instructions are used interchangeably to mean the same thing

u Numerical Example

Addressing Mode Immediate Address Mode Direct Address Mode Indirect Address Mode Register Mode Register Indirect Mode Relative Address Mode Indexed Address Mode Autoincrement Mode u Autodecrement Mode

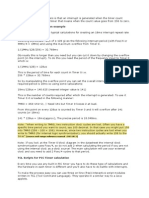

base register hold a base address the address field of the instruction gives a displacement relative to this base address Address Memory Effective Address 201 500 800 400 702 600 400 399 Content of AC 500 800 300 400 700 325 900 700 450 R1 = 400 600 500 + 202 (PC) 900 325 300 PC = 200 R1 = 400 XR = 100 399 AC 400 500 450 700 800 200 201 202 Load to AC Mode Address = 500 Next instruction

u Status Bit Conditions : Fig. 8-8 l Condition Code Bit or Flag Bit

The bits are set or cleared as a result of an operation performed in the ALU

R1 = 400 (after) R1 = 400 -1 (prior) 500 + 100 (XR)

702 800

u 4-bit status register l Bit C (carry) : set to 1 if the end carry C8 is 1 l Bit S (sign) : set to 1 if F7 is 1 l Bit Z (zero) : set to 1 if the output of the ALU contains all 0 s l Bit V (overflow) : set to 1 if the exclusive-OR of the last two carries (C8 and C7) is equal to 1 l Flag Example : A - B = A + ( 2 Comp. Of B ) : A =11110000, B = 00010100 s

11110000 + 11101100 (2 comp. of B) s 1 11011100

Computer System Architecture

C = 1, S = 1, V = 0, Z = 0

Chap. 8 Central Processing Unit

Computer System Architecture

Chap. 8 Central Processing Unit

8-7. Program Control

u Conditional Branch : Tab. 8-11 u Subroutine Call and Return l CALL : SP SP 1

M [ SP ] PC

l

17 / 22

8-8. Reduced Instruction Set Computer (RISC)

n

19 / 22

8-8 Reduced Instruction Set Computer (RISC)

u Complex Instruction Set Computer (CISC) l Major characteristics of a CISC architecture

1) A large number of instructions - typically from 100 to 250 instruction 2) Some instructions that perform specialized tasks and are used infrequently 3) A large variety of addressing modes - typically from 5 to 20 different modes 4) Variable-length instruction formats 5) Instructions that manipulate operands in memory (RISC - in register)

: Decrement stack point

: Push content of PC onto the stack PC Effective Address : Transfer control to the subroutine

RETURN : PC M [ SP ] : Pop stack and transfer to PC

SP SP + 1

: Increment stack pointer

u Program Interrupt l Program Interrupt

Transfer program control from a currently running program to another service program as a result of an external or internal generated request Control returns to the original program after the service program is executed

l

u Reduced Instruction Set Computer (RISC) l Major characteristics of a RISC architecture

1) Relatively few instructions 2) Relatively few addressing modes 3) Memory access limited to load and store instruction 4) All operations done within the registers of the CPU 5) Fixed-length, easily decoded instruction format 6) Single-cycle instruction execution 7) Hardwired rather than microprogrammed control

Interrupt Service Program Subroutine Call

1) An interrupt is initiated by an internal or external signal (except for software interrupt)

n

A subroutine call is initiated from the execution of an instruction (CALL) The address of the subroutine call is determined from the address field of an instruction

2) The address of the interrupt service program is determined by the hardware

n

3) An interrupt procedure stores all the information necessary to define the state of the CPU

n

A subroutine call stores only the program counter (Return address) Chap. 8 Central Processing Unit

Computer System Architecture

Computer System Architecture

Chap. 8 Central Processing Unit

8-7. Program Control

l

18 / 22

8-8. Reduced Instruction Set Computer (RISC)

l

20 / 22

Program Status Word (PSW)

The collection of all status bit conditions in the CPU

Two CPU Operating Modes

Supervisor (System) Mode : Privileged Instruction

n

External Int. Internal Int. Software Int.

Other characteristics of a RISC architecture

1) A relatively large number of registers in the processor unit 2) Use of overlapped register windows to speed-up procedure call and return 3) Efficient instruction pipeline 4) Compiler support for efficient translation of high-level language programs into machine language programs R15

R10 R73 R64 Local to D R63 Common to C and D Local to C R47 Common to B and C Local to B R31 Common to A and B Local to A

Interrupt Detect Determine the address of ISR Store Information

When the CPU is executing a program that is part of the operating system

User Mode : User program

n

PC, CPU Register, Status Condition

CPU operating mode is determined from special bits in the PSW

When the CPU is executing an user program

u Overlapped Register Windows l Time consuming operations during procedure call

Saving and restoring registers Passing of parameters and results

l

Common to D and A Circular Window

u Types of Interrupts l 1) External Interrupts

come from I/O device, from a timing device, from a circuit monitoring the power supply, or from any other external source

l

Main body of ISR ISR Restore Information Interrupt Return

Overlapped Register Windows

Provide the passing of parameters and avoid the need for saving and restoring register values by hardware

R58 Proc D R57 R48

2) Internal Interrupts or TRAP

caused by register overflow, attempt to divide by zero, an invalid operation code, stack overflow, and protection violation

u Concept of overlapped register windows : Fig. 8-9 l Total 74 registers : R0 - R73

R0 - R9 : Global registers R10 - R63 : 4 windows

n n n n

R42 Proc C R41 R32

3) Software Interrupts

initiated by executing an instruction (INT or RST) used by the programmer to initiate an interrupt procedure at any desired point in the program

R26 Proc B R25

Window A Window B Window C Window D

10 Local registers 2 sets of 6 registers (common to adjacent windows)

Chap. 8 Central Processing Unit

Common to all Procedures R0 Global registers

R9

Common to A and D R10 Proc A

R16 R15

Computer System Architecture

Chap. 8 Central Processing Unit

Computer System Architecture

8-8. Reduced Instruction Set Computer (RISC)

l

21 / 22

Example) Procedure A calls procedure B

R26 - R31

n n

Store parameters for procedure B Store results of procedure B

R16 - R25 : Local to procedure A R32 - R41 : Local to procedure B

l l

Window Size = L + 2C + G = 10 + ( 2 X 6 ) + 10 = 32 registers Register File (total register) = (L + C) X W + G = (10 + 6 ) X 4 + 10 = 74 registers

-, G : Global registers = 10 L : Local registers = 10 C : Common registers = 6 W : Number of windows = 4

u Berkeley RISC I l RISC Architecture : 1980

Berkeley RISC project : first project = Berkeley RISC I Stanford MIPS project

l

Berkeley RISC I

32 bit CPU, 32 bit instruction format, 31 instruction 3 addressing modes : register, immediate, relative to PC

Computer System Architecture

Chap. 8 Central Processing Unit

8-8. Reduced Instruction Set Computer (RISC)

l l l

22 / 22

Instruction Set : Tab. 8-12 Instruction Format : Fig. 8-10 Register Mode : bit 13 = 0

S2 = register Example) ADD R22, R21, R23

n

31 24 23 19 18 14 13 12 54 0 Opcode Rd Rs 0 Not used S2 8 5 5 1 8 5 (a) Register mode : (S2 specifies a register) 31 24 23 19 18 14 13 12 Opcode Rd Rs 1 8 5 5 1 31 24 23 19 18 Opcode COND 8 5 0 S2 13 0 Y 19

ADD Rs, S2, Rd : Rd = Rs + S2

Register Immediate Mode : bit 13 = 1

S2 = sign extended 13 bit constant Example) LDL (R22)#150, R5

n

LDL (Rs)S2, Rd : Rd = M[R22] + 150

(b) Register-immediate mode : (S2 specifies an operand)

PC Relative Mode

Y = 19 bit relative address Example) JMPR COND, Y

n

Jump to PC = PC + Y CALL, RET stack pointer

CWP (Current Window Pointer)

n

(c) PC relative mode :

RISC Architecture Originator Architecture Originator Alpha DEC MIPS MIPS Technologies PA-RISC Hewlett Packard PowerPC Apple, IBM, Motorola Sparc Sun i960 Intel

Licensees Mitsubishi, Samsung NEC, Toshiba Hitachi, Samsung Bul Fujitsu, Hyundai Intel only (Embedded Controller)

Computer System Architecture

Chap. 8 Central Processing Unit

You might also like

- Microcontroller and Embedded SystemsDocument2 pagesMicrocontroller and Embedded SystemsIndranilNo ratings yet

- CPU Instruction SummaryDocument9 pagesCPU Instruction SummaryDereck AntonyDengo DomboNo ratings yet

- SPI I2C Interface AnDocument13 pagesSPI I2C Interface AnNivin PaulNo ratings yet

- 8051 Microcontroller ArchitectureDocument25 pages8051 Microcontroller ArchitectureSachin KhandelwalNo ratings yet

- Lec20 RTL DesignDocument40 pagesLec20 RTL DesignVrushali patilNo ratings yet

- SystemVerilog Vs Verilog in RTL DesignDocument4 pagesSystemVerilog Vs Verilog in RTL DesignVijay KumarNo ratings yet

- CSE331L - Introduction to Assembly LanguageDocument7 pagesCSE331L - Introduction to Assembly LanguageTanjila Islam Ritu 1811017642No ratings yet

- BGK MPMC Unit-3 Q and ADocument21 pagesBGK MPMC Unit-3 Q and AMallesh ArjaNo ratings yet

- Bus Architecture ExplainedDocument14 pagesBus Architecture ExplainedAyushi SinghNo ratings yet

- Single Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGADocument4 pagesSingle Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGAInternational Organization of Scientific Research (IOSR)No ratings yet

- Memory Notes1Document102 pagesMemory Notes1nirmal_inbox100% (1)

- Arduino-Based Embedded System ModuleDocument8 pagesArduino-Based Embedded System ModuleIJRASETPublicationsNo ratings yet

- CPU Central Processing UnitDocument73 pagesCPU Central Processing UnitShiv Patel 18-38No ratings yet

- RISC Vs CISC, Harvard V/s Van NeumannDocument35 pagesRISC Vs CISC, Harvard V/s Van NeumannVRAJ PATELNo ratings yet

- Vi For Smaties Linux EditorDocument10 pagesVi For Smaties Linux EditorSandeep ChaudharyNo ratings yet

- 5 - Internal MemoryDocument22 pages5 - Internal Memoryerdvk100% (1)

- FPGA Design MethodologiesDocument9 pagesFPGA Design MethodologiesSambhav VermanNo ratings yet

- Three Main Components of a Computer SystemDocument36 pagesThree Main Components of a Computer SystemAnshulNo ratings yet

- Chapter 7: Register Transfer: ObjectivesDocument7 pagesChapter 7: Register Transfer: ObjectivesSteffany RoqueNo ratings yet

- Master StationDocument138 pagesMaster StationWilmer Quishpe AndradeNo ratings yet

- Ch01 Microcontroller History and FeaturesDocument20 pagesCh01 Microcontroller History and Featuresmaissy dellaNo ratings yet

- Bus System & Data TransferDocument5 pagesBus System & Data Transferlmehta16No ratings yet

- Assembly Language - A Low-Level Programming LanguageDocument67 pagesAssembly Language - A Low-Level Programming LanguageprithiksNo ratings yet

- Ilovepdf MergedDocument430 pagesIlovepdf MergedYuvraj ChhabraNo ratings yet

- Recommended lubricants and refill capacitiesDocument2 pagesRecommended lubricants and refill capacitiestele123No ratings yet

- Coa Unit 1Document28 pagesCoa Unit 1vivek kumarNo ratings yet

- Project FileDocument131 pagesProject FileshaanjalalNo ratings yet

- Asynchronous Clock SynchronizationDocument9 pagesAsynchronous Clock Synchronizationanish1988100% (1)

- CVP Solution (Quiz)Document9 pagesCVP Solution (Quiz)Angela Miles DizonNo ratings yet

- ITIL - Release and Deployment Roles and Resps PDFDocument3 pagesITIL - Release and Deployment Roles and Resps PDFAju N G100% (1)

- Hardware DesignDocument42 pagesHardware DesignSruthi PaletiNo ratings yet

- 03b - FIE - Parcial #3 PLD - Resumen 04c 09Document36 pages03b - FIE - Parcial #3 PLD - Resumen 04c 09amilcar93No ratings yet

- Emb PIC Charles Kim Chap2Document2 pagesEmb PIC Charles Kim Chap2subiNo ratings yet

- VSP-12Way - Is Rev.03Document55 pagesVSP-12Way - Is Rev.03Marcelo AlmeidaNo ratings yet

- Organization: Basic Computer Organization and DesignDocument29 pagesOrganization: Basic Computer Organization and DesignGemechisNo ratings yet

- What Is A MicroprocessorDocument21 pagesWhat Is A MicroprocessorArghya SantraNo ratings yet

- DDR SDR Sdram ComparisionDocument12 pagesDDR SDR Sdram ComparisionSrinivas CherukuNo ratings yet

- T89C51 Training Board Manual GuideDocument44 pagesT89C51 Training Board Manual GuidedavidegrimaNo ratings yet

- 4 Bit Cpu ReportDocument16 pages4 Bit Cpu ReportHarshil LodhiNo ratings yet

- Design of VLSI Architecture For A Flexible Testbed of Artificial Neural Network For Training and Testing On FPGADocument7 pagesDesign of VLSI Architecture For A Flexible Testbed of Artificial Neural Network For Training and Testing On FPGAInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Interfacing Techniques 4-3-3) : Pre-Requisite: MicroprocessorsDocument97 pagesInterfacing Techniques 4-3-3) : Pre-Requisite: Microprocessorssrikaanth3811No ratings yet

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocument8 pagesRipple Carry and Carry Lookahead Adders: 1 ObjectivesYasser RaoufNo ratings yet

- Sap PDFDocument135 pagesSap PDFKowshikaNo ratings yet

- Intel 8051 Micrcontroller: What Is A Microcontroller?Document20 pagesIntel 8051 Micrcontroller: What Is A Microcontroller?satya_vanapalli3422No ratings yet

- Ch17 Spi Protocol and Max7221 Display InterfacingDocument51 pagesCh17 Spi Protocol and Max7221 Display InterfacingSimple knowledgeNo ratings yet

- Orcad PSpice DesignerDocument47 pagesOrcad PSpice DesignerAishwarya JS100% (1)

- 8086 MicroprocessorDocument21 pages8086 MicroprocessorPinki KumariNo ratings yet

- Labview Serial CommunicationDocument0 pagesLabview Serial Communicationmajidkhan04No ratings yet

- Low Power Uart DeviceDocument19 pagesLow Power Uart DeviceparnabmasterNo ratings yet

- Block Diagram of Intel 8086Document5 pagesBlock Diagram of Intel 8086Ritesh SinghNo ratings yet

- CoE 211 Digital Logic Design Lab Manual CoE v5Document158 pagesCoE 211 Digital Logic Design Lab Manual CoE v5HanNo ratings yet

- MCB2300 CanDocument14 pagesMCB2300 CanMichaelNo ratings yet

- Microcontrollers and Embedded SystemsDocument35 pagesMicrocontrollers and Embedded SystemsTarek BarhoumNo ratings yet

- CECS 347 Programming in C Sylabus: Writing C Code For The 8051Document52 pagesCECS 347 Programming in C Sylabus: Writing C Code For The 8051BHUSHANNo ratings yet

- Ldmicro ChangesDocument4 pagesLdmicro ChangesPandu Milik MuNo ratings yet

- Introduction To PSpiceDocument15 pagesIntroduction To PSpiceUmera Anjum100% (1)

- Set an 18ms interrupt period using PIC Timer 0Document3 pagesSet an 18ms interrupt period using PIC Timer 0f.last100% (1)

- MPMC Unit4Document61 pagesMPMC Unit4Nandhini ShreeNo ratings yet

- Uart DesignDocument20 pagesUart Designtrung100% (2)

- 8086 Microprocessor ArchitectureDocument30 pages8086 Microprocessor ArchitectureprasadapawaskarNo ratings yet

- Evaluation of Microprocessor PDFDocument2 pagesEvaluation of Microprocessor PDFJennifer100% (1)

- Floor Plan: General Notes All Diamensins Are in MMDocument1 pageFloor Plan: General Notes All Diamensins Are in MMMustafa JumaNo ratings yet

- Group A - S-SDocument114 pagesGroup A - S-SMustafa JumaNo ratings yet

- ch11 p6Document6 pagesch11 p6Mustafa JumaNo ratings yet

- Lec16 CPUDocument11 pagesLec16 CPUaly20052010No ratings yet

- ASM Architecture ASM Disk Group AdministrationDocument135 pagesASM Architecture ASM Disk Group AdministrationVamsi ChowdaryNo ratings yet

- 10 Consulting Frameworks To Learn For Case Interview - MConsultingPrepDocument25 pages10 Consulting Frameworks To Learn For Case Interview - MConsultingPrepTushar KumarNo ratings yet

- Data SheetDocument14 pagesData SheetAnonymous R8ZXABkNo ratings yet

- Gigahertz company background and store locationsDocument1 pageGigahertz company background and store locationsjay BearNo ratings yet

- Coa - Ofx-8040a (H078K5G018)Document2 pagesCoa - Ofx-8040a (H078K5G018)Jaleel AhmedNo ratings yet

- IBM TS3500 Command Line Interface (CLI) ExamplesDocument6 pagesIBM TS3500 Command Line Interface (CLI) ExamplesMustafa BenmaghaNo ratings yet

- GSM Multi-Mode Feature DescriptionDocument39 pagesGSM Multi-Mode Feature DescriptionDiyas KazhiyevNo ratings yet

- UNIT: 01 Housekeeping SupervisionDocument91 pagesUNIT: 01 Housekeeping SupervisionRamkumar RamkumarNo ratings yet

- Managing operations service problemsDocument2 pagesManaging operations service problemsJoel Christian Mascariña0% (1)

- Shubh AmDocument2 pagesShubh AmChhotuNo ratings yet

- 63db2cf62042802 Budget Eco SurveyDocument125 pages63db2cf62042802 Budget Eco SurveyNehaNo ratings yet

- CONFLICT ManagementDocument56 pagesCONFLICT ManagementAhmer KhanNo ratings yet

- UPGRADEDocument2 pagesUPGRADEVedansh OswalNo ratings yet

- Presentation of The LordDocument1 pagePresentation of The LordSarah JonesNo ratings yet

- Parasim CADENCEDocument166 pagesParasim CADENCEvpsampathNo ratings yet

- Assignment 2 - p1 p2 p3Document16 pagesAssignment 2 - p1 p2 p3api-31192579150% (2)

- BIU and EU functions in 8086 microprocessorDocument12 pagesBIU and EU functions in 8086 microprocessorDaksh ShahNo ratings yet

- Whats The Average 100 M Time For An Olympics - Google SearchDocument1 pageWhats The Average 100 M Time For An Olympics - Google SearchMalaya KnightonNo ratings yet

- Rust Experimental v2017 DevBlog 179 x64 #KnightsTableDocument2 pagesRust Experimental v2017 DevBlog 179 x64 #KnightsTableIngrutinNo ratings yet

- A Dream Takes FlightDocument3 pagesA Dream Takes FlightHafiq AmsyarNo ratings yet

- Savable Data Page - Its Configuration, Usage & ExecutionDocument20 pagesSavable Data Page - Its Configuration, Usage & ExecutionsurmanpaNo ratings yet

- Concept, Types, Characteristics and ClassificationsDocument6 pagesConcept, Types, Characteristics and ClassificationsCJ FaNo ratings yet

- Company Profi Le: IHC HytopDocument13 pagesCompany Profi Le: IHC HytopHanzil HakeemNo ratings yet

- Responsibility Centres: Nature of Responsibility CentersDocument13 pagesResponsibility Centres: Nature of Responsibility Centersmahesh19689No ratings yet

- Tita-111 2Document1 pageTita-111 2Gheorghita DuracNo ratings yet