Professional Documents

Culture Documents

Maquinas de Estados Mealy VHDL

Uploaded by

Francisco Javier Herrera HernandezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Maquinas de Estados Mealy VHDL

Uploaded by

Francisco Javier Herrera HernandezCopyright:

Available Formats

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Unidad 8 Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Andres.Iborra@upct.es Juan.Suardiaz@upct.es Mayo 2003

TEMARIO

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

CONTENIDO

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.). 8.1. Introduccin. 8.1.1. Concepto de estado. 8.1.2. Mquinas tipo Mealy y Moore. 8.1.3. Tablas y Diagramas de Estados. 8.2. Anlisis de mquinas de estados. 8.2.1. Estructura de una mquina de estados. 8.2.2. Lgica de salida. 8.2.3. Ecuaciones caractersticas. 8.3. Diseo de Mquinas de Estados. 8.3.1. Asignacin de estados. 8.3.2. Minimizacin de estados. 8.3.3. Ecuaciones de Transicin. 8.3.4. Ecuaciones de Excitacin. 8.4. Descripcin VHDL de mquinas de estados. 8.5. Ejemplo de aplicacin: Diseo del circuito de control de llenado de un depsito de lquidos.

OBJETIVOS ESPECFICOS

Repasar los conceptos de estado y variable de estado. Distinguir entre comportamientos tipo Mealy y Moore. Conocer la estructura de diseo de una mquina de estados. Ser capaz de deducir las ecuaciones caractersticas de un sistema secuencial. Poder minimizar un diagrama de estados. Ser capaz de obtener un diagrama de estados partiendo de unas especificaciones dadas. Poder afrontar con xito el diseo de una mquina de estados. Aprender a modelar estos componentes en VHDL.

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

8.1 INTRODUCCIN

Concepto de estado. En la unidad anterior se han definido los circuitos secuenciales como aquellos que recuerdan lo que les ha sucedido en instantes de tiempo anteriores y son capaces de alterar su comportamiento futuro en base a esta informacin. Un contador es un claro ejemplo de este tipo de circuitos, ya Q que es capaz de recordar su valor actual (estado actual) a fin CLK de sumarle 1 para evolucionar al siguiente valor (estado). El valor actual del contador se define como su estado actual, el cual a su vez sirve para determinar cmo va evolucionar para llegar al estado siguiente. De forma general, se puede considerar que un circuito secuencial ha de memorizar una serie de situaciones, de forma que su comportamiento puede considerarse como la evolucin de una situacin a otra (o incluso a la misma). Cada una de estas situaciones ser lo que se denominar un estado y el cambio de una situacin a otra ser lo que se denominar transicin. Por ejemplo, si el contador actualmente presenta el valor de cuenta 5, en la prxima activacin del reloj deber incrementarse para pasar al estado 6. Este cambio del estado 5 al estado 6 es lo que se denomina transicin. Como ya se ha comentado, el circuito secuencial ha de memorizar los posibles estados. Para ello usar biestables, los cuales constituyen los elementos mnimos de almacenamiento de informacin. Como un biestable puede codificar dos estados (1 0), para codificar un sistema secuencial que presente E estados, se deber usar un nmero de biestables (B) tal que 2B E. En consecuencia: N Biestables = log2(N estados) La forma en que se codifica cada posible situacin (estado) segn los posibles valores que presenten los biestables es lo que se denomina asignacin de estados.

3

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Mquinas de Mealy y Moore. En una mquina de estados, cada estado siempre ser funcin del estado anterior y de las entradas. Sin embargo, atendiendo a la forma en que se generan las salidas es posible hablar de dos tipos diferentes de mquinas de estado finitas: Mquina de Moore.

Estado Siguiente = F(Estado Actual, Entrada) Salida = G(Estado Actual)

Mquina de Mealy

Estado Siguiente = F(Estado Actual, Entrada) Salida = G(Estado Actual, Entrada)

Tablas y Diagramas de estado. Para describir el funcionamiento de un circuito secuencial se utilizan las denominadas tablas de estados (o tablas de excitacin) y unos dibujos denominados diagramas de estados. Supongamos el caso de un circuito secuencial que se comporte como un contador de tres bits, con una seal (Up) que controle si la cuenta se realiza de forma ascendente (Up=1) o descendente (Up=0). La tabla de estados consiste en una tabla en la que se muestra en funcin del estado actual y las combinaciones posibles de las entradas, el prximo estado al que se deber acudir. Valor Est. Actual Ent. Est. Sig. Cuenta Q2 Q1 Q0 U Q2* Q1* Q0*

0 1 2 3 4 5 6 7 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

4

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

1 0 0 0 0 0 0 1 0 1 1 1 1 1 1 0

1 0 0 1 0 1 1 0 1 0 0 1 0 1 1 0

1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Un diagrama de estados es un dibujo que muestra cada estado de la mquina y todas las posibles secuencias en las cuales un circuito puede cambiar de un estado a otro. Los estados se representan con crculos y las transiciones mediante flechas. Sobre las flechas se suele usar una notacin del tipo In-1In-1I0/Sm-1Sm-2S 0 para sealar los valores de las entradas (I n-1In-1I 0) que producen la salida correspondiente (Sm-1Sm-2S 0). I2I1 E S

Notacin Moore

I2I1/S0 E

Notacin Mealy

En el caso de mquinas tipo Moore, en las que las salidas slo dependen del estado es comn representar la salida dentro del crculo que representa el estado y usar en las transiciones una notacin del tipo: In-1In-1I0.

Diagrama de estados del contador Up/Down de tres bits:

U Ei

1 E0 E7 1 0 E6 0 1 E5 0 0 0 0

1 E1

E2 0 1 E3 E4

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

8.2 ANLISIS DE MQUINAS DE ESTADO

Estructura de una mquina de estados. De manera general, es posible considerar que una mquina de estados est formada por los siguientes bloques funcionales: 1.- Memoria de estados. Se trata de un conjunto de n flip-flops que almacenan el estado actual de la mquina, y tiene 2n estados distintos. Lo normal es hablar de mquinas de estados sncronas, es decir aqullas en las que todos los flip-flops se encuentran conectados a una seal de reloj comn. Este tipo de mquinas ser el que se aborda en la presente unidad. 2.- Lgica del estado siguiente. Se trata de un bloque combinacional que, en funcin del estado y entradas actuales, genera una funcin (F) que alimentar a las entradas de los biestables y har que estos evolucionen hacia el estado siguiente. 3.- Lgica de salida. Genera las funciones de salida del circuito secuencial. Lgica de salida. Anteriormente se ha comentado que la diferencia entre los dos posibles modelos de mquinas de estado se encuentra en cmo son generadas las salidas. Mquina de Mealy: S=G(Entradas, Estado Actual) Estado Actual MEMORIA DE ESTADO Excitacin RESET CLK

6

Entradas

LGICA DE ESTADO SIGUIENTE (F)

LGICA DE SALIDA (G)

Salidas

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Mquina de Moore: S=G(Estado Actual) Entradas Estado Actual MEMORIA DE ESTADO Excitacin RESET CLK Salidas

LGICA DE ESTADO SIGUIENTE (F)

LGICA DE SALIDA (G)

En el diseo de circuitos de alta velocidad, con frecuencia es necesario asegurar que las salidas de la mquina de estados se encuentren disponibles tan pronto como sea posible y que no cambien durante cada periodo de reloj. Una forma de conseguir este comportamiento es codificar el estado de forma que las mismas variables de estado sirvan como salida, lo que conduce a mquinas tipo Moore. En consecuencia, cuando se trabaja en diseos digitales de alta velocidad, las mquinas de Moore presentan mejores resultados. Sin embargo, las mquinas tipo Mealy suelen producir soluciones de menor rea al presentar menos estados que sus equivalentes tipo Moore. En consecuencia, es tarea del diseador elegir la mejor opcin, en funcin de las necesidades de su diseo. Ecuacin caracterstica. El comportamiento funcional de un biestable puede describirse formalmente mediante una expresin booleana, denominada ecuacin caracterstica, que especifica el siguiente estado del biestable (Q*) como una funcin de su estado actual (Q) y de las entradas actuales. Es importante resaltar que la ecuacin caracterstica no describe el comportamiento de temporizacin detallado del dispositivo (activo por nivel, flanco), sino solamente la respuesta funcional a las entradas de control.

7

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Q Q

Q Q

BIESTABLE D D 0 1 Q* 0 1

BIESTABLE T T 0 1 Q* Q

Q

Q* = D Con Enable (EN): Q* = EN D + EN Q

Q* = T Q + T Q

S R

Q Q

J K

Q Q

BIESTABLE S-R S 0 0 1 1 R 0 1 0 1 Q* Q 0 1 No Valido J 0 0 1 1

BIESTABLE J-K K 0 1 0 1 Q* Q 0 1

Q

Q* = S + R Q

Q* = J Q + K Q

En conclusin, si se desea analizar un circuito del que se conoce que implementa una mquina de estados, conviene seguir los siguientes pasos bsicos: 1. Determinar las funciones del estado siguiente (F) y salida (G) en base a los elementos constitutivos que forman el circuito y sus conexiones. 2. Utilizar las funciones F y G para construir una tabla de estado/salida que especifique completamente el estado siguiente y la salida del circuito para toda posible combinacin de estado siguiente y salida. 3. Dibujar un diagrama de estado que presente la informacin de los pasos anteriores de forma grfica.

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

8.3 DISEO DE MQUINAS DE ESTADO.

El proceso de diseo de una mquina de estados finita, a partir de una especificacin o descripcin en palabras puede resumirse en los siguientes pasos: 1. Construir una tabla de estado/salida que corresponde a la especificacin, empleando nombres de mnemnicos para los estados. (Tambin es posible comenzar con un diagrama de estados). 2. (Opcional) Minimizar el nmero de estados en la tabla de estado/salida o diagrama de estados. 3. Elegir un conjunto de variables de estado y asignar combinaciones de estadovariable a los estados nombrados (proceso de asignacin de estados). 4. Crear la denominada tabla de transiciones. Esto es, sustituir las combinaciones de estado-variable en la tabla de estado/salida para crear una tabla de transicin/salida que muestre la siguiente combinacin variable-estado y salida para cada combinacin de estado/entrada actual. 5. Elegir un tipo de flip-flop para la memoria de estado. 6. Construir una tabla de excitacin, que muestre los valores de excitacin requeridos para obtener el siguiente estado deseado para cada combinacin de estado/entradas. 7. Obtener las ecuaciones de excitacin a partir de la tabla de excitacin. 8. Obtener las ecuaciones de salida a partir de la tabla de transiciones. 9. Implementar de las ecuaciones en un circuito fsico. Minimizacin de estados. En ocasiones, la especificacin conduce a un diagrama de estados inicial que presenta muchos estados. Bajo unas determinadas condiciones es posible efectuar una reduccin de estados gracias a que ciertos caminos de la mquina de estados pueden eliminarse porque su comportamiento en funcin de las entradas y salidas se halla duplicado por algn otro camino equivalente. De forma general, es posible decir que dos estados tendrn un comportamiento equivalente (y por lo tanto podrn resumirse en uno slo) si para todas sus combinaciones posibles de entradas, sus salidas son las mismas y evolucionan hacia los mismos estados o hacia estados que tambin son equivalentes.

9

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

El algoritmo para reducir los estados podra resumirse en los siguientes pasos: 1. En primer lugar se agrupan los estados que presentan las mismas salidas (caso de mquinas de Moore) o las mismas salidas en las transiciones (caso de mquinas de Mealy). Estos determinarn un conjunto de estados potencialmente equivalentes, ya que los estados no pueden ser equivalentes si sus salidas difieren. 2. A continuacin se examinan las transiciones, a fin de comprobar que para cada posible combinacin conducen al mismo estado (o a dos estados que tambin son equivalentes). En caso de ocurrir esto, ambos estados son equivalentes y pueden reemplazarse por un nuevo estado que englobe a ambos. Entonces se cambian todas las transiciones de forma que se actualicen todas las evoluciones hacia este nuevo estado y se repite el proceso hasta que no puedan unirse ms estados. Ejemplo de minimizacin:

Diagrama de estados original

Diagrama de estados minimizado (E0 E2)

10

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Asignacin de estados. El nmero de puertas que se necesitarn para implementar una mquina de estados se halla fuertemente relacionado con la manera en que se produce la codificacin de sus estados. a) Metodologa de asignacin heurstica. Una estrategia heurstica habitual para la asignacin de estados es aquella que trata de minimizar el nmero de bits que han de cambiar a lo largo de las transiciones. Consideremos una mquina de estados que presenta 5 estados (S0S4) y se duda entre cualquiera de las siguientes codificacin de estados:

Estado S0 S1 S2 S3 S4

Asignacin 1 Q2 Q1 Q0 0 0 0 1 0 1 1 1 1 0 1 0 0 1 1

Estado S0 S1 S2 S3 S4

Asignacin 2 Q2 Q1 Q0 0 0 0 0 0 1 0 1 0 0 1 1 1 1 1

En este caso, se analizaran todas las transiciones que presenta la mquina de estados y calcularamos para cada una de ellas el nmero de bits que han de cambiar de un estado al siguiente. Supongamos que la mquina de estado disponible presenta las transiciones resumidas en la tabla adjunta:

Bits que cambian Asignacin 1 Asignacin 2 2 1 3 1 3 1 2 1 1 1 2 2 13 bits 7 bits

Transicin S0 -> S1 S0 -> S2 S1 -> S3 S2 -> S3 S3 -> S4 S4 -> S1

11

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

En consecuencia, la asignacin 2 es la ptima ya que minimiza el nmero de bits que cambiarn a lo largo de la evolucin de los estados. El principal problema de este mtodo es que hay que efectuar todas las combinaciones posibles y analizar cada una de ellas. Lo habitual es que los entornos de desarrollo presenten herramientas que realicen esta asignacin de forma automtica. Otro aspecto importante en la asignacin de estados es la codificacin de los estados iniciales. Conviene elegir una que sea posible implementar fcilmente en la inicializacin de los biestables. La ms habitual suele ser todo a 0 (RESET) o todo a 1 (SET). b) Codificacin One-hot. Este tipo de codificacin suele presentar buenos resultados cuando se realizan diseos que deben trabajar a elevadas frecuencias de reloj. La idea fundamental consiste en realizar una asignacin que en vez de usar N bits para codificar 2N estados, se usen tantos bits como estados presenta el diseo. De esta forma, una mquina con S estados, estar implementada usando S flip-flops y no el log 2(S). Adems cada estado tendr una asignacin en la que un nico bit tendr el valor de 1 y el resto 0. As, una mquina de estados que presentara 4 posibles estados de funcionamiento presentara la siguiente codificacin:

Asignacin Tradicional (2 flip-flops) Estado Q2 Q1 S0 0 0 S1 0 1 S2 1 0 S3 1 1 Asignacin One hot Estado Q3 Q2 Q1 S0 0 0 0 S1 0 0 1 S2 0 1 0 S3 1 0 0

Q0 1 0 0 0

La ventaja de la codificacin One-hot radica en el hecho de conseguir simplificar la lgica de generacin del estado siguiente y de las salidas, conduciendo a diseos que pueden trabajar a una frecuencia de funcionamiento superior.

12

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Ecuaciones de transicin. Permiten obtener la lgica combinacional de salida.

UP CLK

Cuenta

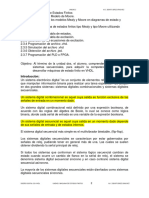

Est. Actual Est. Siguiente Salidas Q1 Q0 Up Q1* Q0* S1 S0 0 0 0 1 1 0 0 0 0 0 1 0 1 0 0 0 1 0 0 0 0 1 1 0 1 1 1 0 0 1 1 0 0 0 1 1 0 2 1 0 1 1 1 1 0 1 1 0 1 0 1 1 3 1 1 1 0 0 1 1 Se minimizara por Karnaugh S1 = Q1 y S0 = Q0 (Mquina de Moore) Ecuaciones de excitacin. Generan la lgica combinacional del siguiente estado. Suponiendo biestables T:

Est. Actual Est. Siguiente Excitacin Q1 Q0 Up Q1* Q0* T1 T0 0 0 0 1 1 1 1 0 0 0 1 0 1 0 1 0 1 0 0 0 0 1 1 0 1 1 1 0 1 1 1 0 0 0 1 1 1 2 1 0 1 1 1 0 1 1 1 0 1 0 0 1 3 1 1 1 0 0 1 1 Minimizando por Karnaugh se obtendra: T0 = 1 T1 = QoUp + Qo Up = Qo xnor Up. Cuenta

13

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

8.4 DESCRIPCIN VHDL DE MQUINAS DE ESTADOS.

VHDL permite realizar descripciones logartmicas a alto nivel de mquinas de estado. De esta forma, el diseador se evita tareas como generar la tabla de transicin de estados, o la obtencin de las ecuaciones de excitacin, basadas en el tipo de biestable seleccionado. Una mquina de estados se puede describir en VHDL de varias formas. 1. En primer lugar, en la seccin de declaraciones de la arquitectura, se define un tipo enumerado en el que se asignan identificadores a cada estado. Suele ser recomendable utilizar identificadores ilustrativos para los estados. La herramienta de sntesis ser la encargada de codificar estos estados. Aqu tambin suele ser -- Esto se colocara en la zona de declaraciones de la arquitectura. TYPE TipoEstados IS (Esperar, E1, E2, E3); SIGNAL tEstadoActual, tEstadoSiguiente: TipoEstados; 2. En lo que se refiere a la descripcin funcional de la mquina de estados, tanto para las mquinas de Moore como para las de Mealy conviene separar la parte secuencial de la combinacional, de manera que las asignaciones de salida se efecten con sentencias de asignacin concurrente; la asignacin del siguiente estado con un proceso y una sentencia case y finalmente modelar los biestables usados en otro proceso separado. En conclusin, dentro de la arquitectura que describe la mquina de estados conviene que aparezcan tres zonas claramente diferenciadas: c) a) b)

a) Una zona dedicada a un proceso, el cual modela la lgica combinacional encargada de la generacin del estado siguiente. b) Una zona dedicada a un proceso que modela la lgica secuencial encargada de implementar la memoria de estado. c) Una zona concurrente en la que se modela la lgica combinacional encargada de implementar las ecuaciones de salida.

14

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Ejemplo de descripcin VHDL de una Mquina de estados:

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MaquinaEstados IS PORT ( sEntrada1, sEntrada2, sEntrada3: IN std_logic; --Seales de entrada. CLK: IN std_logic; --Seal de reloj. (No olvidar) sResetL: IN std_logic; --Seal de inicializacin sSalida1, sSalida2: OUT std_logic); --Salidas END MaquinaEstados; ARCHITECTURE MaquinaEstadosArch OF MaquinaEstados IS --Declaracin del tipo asociado a los estados. TYPE TipoEstados IS (EInicio, EDetect1, EAbort, EDetect2, EFin); --Seales auxiliares para la codificacin del --estado actual y siguiente. SIGNAL tEstadoActual, tEstadoSiguiente: TipoEstados; BEGIN -- Proceso dedicado a la lgica de estado: LOGICA_ESTADO: PROCESS(tEstadoActual, sEntrada1, sEntrada2, sEntrada3) BEGIN CASE (tEstadoActual) IS WHEN EInicio => IF (sEntrada1 = 1) THEN tEstadoSiguiente <= EAbort; ELSIF (sEntrada2 = 0 AND sEntrada3 = 1) THEN tEstadoSiguiente <= EDetect2; ELSE tEstadoSiguiente <= EInicio; END IF; WHEN EDetect1 => IF (sEntrada1 = 1) THEN tEstadoSiguiente <= EFin; ELSE tEstadoSiguiente <= EDetect1; END IF; WHEN EAbort =>

IF (sEntrada2 = 1) THEN tEstadoSiguiente <= Edetect2; ELSE tEstadoSiguiente <= EDetect1; END IF; WHEN EDetect2 => IF (sEntrada2 = 1) THEN tEstadoSiguiente <= EFin; ELSE tEstadoSiguiente <= EAbort; END IF; WHEN EFin => IF (sEntrada1 = 0 and sEntrada2 = 0 and sEntrada3 = 0) THEN tEstadoSiguiente <= EInicio; ELSE tEstadoSiguiente <= EFin; END IF; END CASE; END PROCESS LOGICA_ESTADO; -- Proceso dedicado a la Memoria de Estado MEM_ESTADO: PROCESS(CLK, sResetL, tEstadoSiguiente) BEGIN --Inicializacin con RESET_L IF (sResetL =0) THEN tEstadoSiguiente<=Einicio; ELSIF(rising_edge(CLK)) THEN tEstadoActual <= tEstadoSiguiente; END IF; END PROCESS MEM_ESTADO; --Zona concurrente dedicada a modelar la --lgica de salida. --Si salidas = f(est actual, entradas)=> Mquina. MEALY --Si salidas = f(est actual)=> Mquina. MOORE sSalida1 <= 1 WHEN tEstadoActual = EInicio ELSE 1 WHEN tEstadoActual = EDetect1 ELSE 0; sSalida2 <= 1 WHEN tEstadoActual = EAbort ELSE 1 WHEN tEstadoActual = EFin ELSE 0; END MaquinaEstadosArch;

15

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

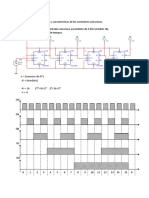

Ej1: Describa en VHDL el diagrama de estados de la figura adjunta:

RESET

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MaquinaEstados IS PORT ( sEntrada: IN std_logic; --Seal de entrada. CLK: IN std_logic; --Seal de reloj. sResetH: IN std_logic; --Seal de inicializacin sSalida: OUT std_logic); --Salida END MaquinaEstados; ARCHITECTURE MaquinaEstadosArch OF MaquinaEstados IS --Declaracin del tipo asociado a los estados. TYPE TipoEstados IS (E0, E1, E2, E3, E4); --Seales auxiliares para la codificacin del --estado actual y siguiente. SIGNAL tEstadoActual, tEstadoSiguiente: TipoEstados; BEGIN -- Proceso dedicado a la lgica de estado: LOGICA_ESTADO: PROCESS(tEstadoActual, sEntrada) BEGIN CASE (tEstadoActual) IS WHEN E0 => IF (sEntrada = 1) THEN tEstadoSiguiente <= E1; ELSE tEstadoSiguiente <= E4; END IF; WHEN E1 => IF (sEntrada = 1) THEN tEstadoSiguiente <= E2; ELSE tEstadoSiguiente <= E4; END IF;

WHEN E2 => IF (sEntrada = 1) THEN tEstadoSiguiente <= E3; ELSE tEstadoSiguiente <= E4; END IF; WHEN E3 => tEstadoSiguiente <= E3; WHEN E4 => IF (sEntrada = 1) THEN tEstadoSiguiente <= E1; ELSE tEstadoSiguiente <= E4; END IF; END CASE; END PROCESS LOGICA_ESTADO; -- Proceso dedicado a la Memoria de Estado MEM_ESTADO: PROCESS(CLK, sResetH, tEstadoSiguiente) BEGIN --Inicializacin con RESET_H IF (sResetH =1) THEN tEstadoSiguiente<=E0; ELSIF(rising_edge(CLK)) THEN tEstadoActual <= tEstadoSiguiente; END IF; END PROCESS MEM_ESTADO; --Zona concurrente dedicada a modelar la --lgica de salida. sSalida <= 1 WHEN (tEstadoActual = E2 and sEntrada = 1) ELSE 0; -- sSalida = f(Estado, entrada) => Mquina de Mealy. END MaquinaEstadosArch;

16

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

8.5 EJEMPLO DE APLICACIN: DISEO DEL CIRCUITO DE CONTROL DE LLENADO DE UN DEPSITO DE LQUIDOS.

Un tanque de agua abierto por la parte superior dispone de tres sensores de deteccin de llenado (A, B, C) que determinan 4 posibles niveles de llenado (VACIO, NORMAL, LLENO, ALARMA). El nivel del tanque se controla mediante dos vlvulas (E, entrada y S, salida). Se pide disear un circuito de control que opere de la siguiente forma: En condiciones de llenado normal, las vlvulas E y S se encuentran abiertas. Si el lquido llega al nivel de vaco, se cierra la vlvula de salida y se mantiene abierta la de entrada. Si el lquido llega al nivel de lleno, se cierra la vlvula de entrada y se mantiene abierta la de salida. Si por cualquier circunstancia, por ejemplo lluvia, se llegara al nivel de alarma, se deber cerrar la vlvula de entrada y abrir la de salida. Esta situacin se mantendr hasta que el tanque llegue al estado de vacio. Datos adicionales: El funcionamiento de los sensores digitales y las vlvulas E y S se encuentra resumido en las tablas adjuntas: E

Sensores de deteccin A B C Significado 0 0 0 VACIO 0 0 1 NORMAL 0 1 0 NO VLIDO 0 1 1 LLENO 1 0 0 NO VLIDO 1 0 1 NO VLIDO 1 1 0 NO VLIDO 1 1 1 ALARMA

Vlvulas E y S: 1 Abierta 0 Cerrada

A B

17

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

Desde el punto de vista de nuestro diseo, es posible considerarlo como una caja negra que presentar el siguiente aspecto: Entradas: Tres entradas asociadas para cada uno de los sensores de deteccin de nivel ms una seal de reloj (CLK) y otra de inicializacin (ResetH), asociadas a la parte secuencial. Salidas: Dos (E y S), encargadas de controlar las vlvulas de llenado y vaciado. A B C CLK ResetH a) Diseo de Mquina de estados tipo MOORE: E ES Equivalentes MQUINA DE ESTADOS E

ABC

18

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MaquinaEstadosMoore IS PORT ( sA, sB, sC: IN std_logic; --Seal de entrada. CLK: IN std_logic; --Seal de reloj. sResetH: IN std_logic; --Seal de inicializacin sE, sS: OUT std_logic); --Salida END MaquinaEstadosMoore; ARCHITECTURE MaquinaEstadosMooreArch OF MaquinaEstadosMoore IS --Declaracin del tipo asociado a los estados. TYPE TipoEstados IS (VACIO, NORMAL, LLENO, ALARMA); --Seales auxiliares para la codificacin del --estado actual y siguiente. SIGNAL tEstadoActual, tEstadoSiguiente: TipoEstados; BEGIN -- Proceso dedicado a la lgica de estado: LOGICA_ESTADO: PROCESS(tEstadoActual, sEntrada) BEGIN CASE (tEstadoActual) IS WHEN VACIO => IF (sA = 0 and sB=0 and sC = 0) THEN tEstadoSiguiente <= VACIO; ELSIF (sA = 0 and sB=0 and sC = 1) THEN tEstadoSiguiente <= NORMAL; ELSIF (sA = 0 and sB=1 and sC = 1) THEN tEstadoSiguiente <= LLENO; ELSIF (sA = 1 and sB=1 and sC = 1) THEN tEstadoSiguiente <= ALARMA; END IF; WHEN NORMAL => IF (sA = 0 and sB=0 and sC = 0) THEN tEstadoSiguiente <= VACIO; ELSIF (sA = 0 and sB=0 and sC = 1) THEN tEstadoSiguiente <= NORMAL;

ELSIF (sA = 0 and sB=1 and sC = 1) THEN tEstadoSiguiente <= LLENO; END IF; WHEN LLENO => ELSIF (sA = 0 and sB=0 and sC = 1) THEN tEstadoSiguiente <= NORMAL; ELSIF (sA = 0 and sB=1 and sC = 1) THEN tEstadoSiguiente <= LLENO; ELSIF (sA = 1 and sB=1 and sC = 1) THEN tEstadoSiguiente <= ALARMA; END IF; WHEN ALARMA => IF (sA = 0 and sB=0 and sC = 0) THEN tEstadoSiguiente <= VACIO; ELSE tEstadoSiguiente <= ALARMA; END IF; END CASE; END PROCESS LOGICA_ESTADO; -- Proceso dedicado a la Memoria de Estado MEM_ESTADO: PROCESS(CLK, sResetH, tEstadoSiguiente) BEGIN --Inicializacin con RESET_H IF (sResetH =1) THEN tEstadoSiguiente<=E0; ELSIF(rising_edge(CLK)) THEN tEstadoActual <= tEstadoSiguiente; END IF; END PROCESS MEM_ESTADO; --Zona concurrente dedicada a modelar la --lgica de salida. sS <= 0 WHEN (tEstadoActual = VACIO) ELSE 1; sE <= 1 WHEN (tEstadoActual = NORMAL or tEstadoActual = VACIO) ELSE 0; -- sSalida = f(Estado) => Mquina de M OORE. END MaquinaEstadosMooreArch;

19

Diseo de Sistemas Electrnicos-DB4

Unidad 8. Diseo Basado en Mquinas de Estado Finitas (F.S.M.)

b) Diseo de Mquina de estados tipo MEALY: ABC/ES Equivalentes E

Diagrama Mealy original

Diagrama Mealy simplificado

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MaquinaEstadosMealy IS PORT ( sA, sB, sC: IN std_logic; --Seal de entrada. CLK: IN std_logic; --Seal de reloj. sResetH: IN std_logic; --Seal de inicializacin sE, sS: OUT std_logic); --Salida END MaquinaEstadosM ealy; ARCHITECTURE MaquinaEstadosM ealyArch OF MaquinaEstadosMealy IS --Declaracin del tipo asociado a los estados. TYPE TipoEstados IS (NO_ALARMA, ALARMA); --Seales auxiliares para la codificacin del --estado actual y siguiente. SIGNAL tEstadoActual, tEstadoSiguiente: TipoEstados; BEGIN -- Proceso dedicado a la lgica de estado: LOGICA_ESTADO: PROCESS(tEstadoActual, sEntrada) BEGIN CASE (tEstadoActual) IS WHEN NO_ALARMA => IF (sA = 1 and sB=1 and sC = 1) THEN tEstadoSiguiente <= ALARMA; ELSE tEstadoSiguiente <= NO_ALARMA; END IF;

WHEN ALARMA => IF (sA = 0 and sB=0 and sC = 0) THEN tEstadoSiguiente <= NO_ALARMA; ELSE tEstadoSiguiente <= ALARMA; END IF; END CASE; END PROCESS LOGICA_ESTADO; -- Proceso dedicado a la Memoria de Estado MEM_ESTADO: PROCESS(CLK, sResetH, tEstadoSiguiente) BEGIN --Inicializacin con RESET_H IF (sResetH =1) THEN tEstadoSiguiente<=E0; ELSIF(rising_edge(CLK)) THEN tEstadoActual <= tEstadoSiguiente; END IF; END PROCESS MEM_ESTADO; --Zona concurrente dedicada a modelar la --lgica de salida. sS <= 1 WHEN (sC = 1) ELSE 0; sE <= 1 WHEN (tEstadoActual = NO_ALARMA and sA = 0 and sB = 0) ELSE 0; -- sSalida = f(Estado, Entradas) => Mquina de M EALY. END MaquinaEstadosM ealyArch;

20

You might also like

- Maquina Moore y MealyDocument24 pagesMaquina Moore y MealyKiara Salcedo Mamani100% (1)

- Proyecto Semáforo de Dos Vías Con VHDLDocument5 pagesProyecto Semáforo de Dos Vías Con VHDLQuintana Albarracin Carlos Javier50% (2)

- Contadores J-KDocument14 pagesContadores J-KYessenia López0% (1)

- VHDL Unidad 2 Máquinas de Estados FinitosDocument23 pagesVHDL Unidad 2 Máquinas de Estados Finitosgustavosm50% (2)

- Contador Con Flip-FlopDocument2 pagesContador Con Flip-Floptubi vok3100% (3)

- Maquinas de Estados FinitosDocument8 pagesMaquinas de Estados FinitosOmar Ruiz RodríguezNo ratings yet

- Trabajo Final1 - VHDLDocument7 pagesTrabajo Final1 - VHDLElyel Surco M0% (1)

- Implementación de funciones lógicas mediante PAL y VHDLDocument12 pagesImplementación de funciones lógicas mediante PAL y VHDLgustavogomez4505No ratings yet

- Proyecto Final VHDLDocument14 pagesProyecto Final VHDLFortino50% (2)

- Fpga y PLD, VHDL y VerilogDocument6 pagesFpga y PLD, VHDL y VerilogLuis PintadoNo ratings yet

- Maquinas de Estado Con VHDLDocument20 pagesMaquinas de Estado Con VHDLMiguel Andrés Fino100% (2)

- 6 Circuitos Combinacionales P ImprimirDocument36 pages6 Circuitos Combinacionales P ImprimirFabian AcostaNo ratings yet

- Contador CanicasDocument8 pagesContador Canicasaioros2112No ratings yet

- Circuitos aritméticos binariosDocument76 pagesCircuitos aritméticos binariosChampa Jiménez de CostanillasNo ratings yet

- Comunicación Serial 16F877ADocument17 pagesComunicación Serial 16F877AClintonSemanate100% (1)

- Sistemas Digitales Trabajo 4Document34 pagesSistemas Digitales Trabajo 4福嶋満雄No ratings yet

- Display's BCD 7 y 16 SegmentosDocument5 pagesDisplay's BCD 7 y 16 SegmentosLuis Alberto SDNo ratings yet

- Práctica 8 Latches y Flip FlopsDocument4 pagesPráctica 8 Latches y Flip FlopsRay GzzNo ratings yet

- Teclado matricial: decodificación con circuitos TTL y 74C922Document14 pagesTeclado matricial: decodificación con circuitos TTL y 74C922Edwin Gandhy Flores Gómez0% (1)

- MICROCODE Programa de Secuencia de Led y SemaforoDocument13 pagesMICROCODE Programa de Secuencia de Led y SemaforoDanny Sixto Armijos LoyolaNo ratings yet

- 5 - Maquinas de Estado Con VHDLDocument21 pages5 - Maquinas de Estado Con VHDLwilliamNo ratings yet

- Laboratorio 5 (Interrupciones)Document10 pagesLaboratorio 5 (Interrupciones)Manolo Camilo Ortega CondegaNo ratings yet

- Laboratorio Latch Flip Flops MAEFNDocument28 pagesLaboratorio Latch Flip Flops MAEFNItaloCardenasNo ratings yet

- Aplicaciones Con VHDLDocument6 pagesAplicaciones Con VHDLViny Pazmiño50% (2)

- 1 Estructura Funcionamiento ALUDocument6 pages1 Estructura Funcionamiento ALUAlbri Reyes100% (3)

- Diseño Logico Secuencial Con VHDLDocument43 pagesDiseño Logico Secuencial Con VHDLENIC-AITCG100% (1)

- Programación II - Ejercicio Del Ratón en El LaberintoDocument1 pageProgramación II - Ejercicio Del Ratón en El LaberintoRaquel Umaña0% (1)

- Practica 2 PicoBlazeDocument24 pagesPractica 2 PicoBlazeAntonio David EscobarNo ratings yet

- Mapas de KarnaughDocument25 pagesMapas de Karnaughjlva_lkpbNo ratings yet

- Reporte de Practica 8 ALUDocument9 pagesReporte de Practica 8 ALUDavid Hernández Osorio100% (1)

- 2 Descripción General Del PIC16F877 PDFDocument63 pages2 Descripción General Del PIC16F877 PDFMikael MontenegroNo ratings yet

- Multimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásDocument9 pagesMultimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásArmando Campos SalazarNo ratings yet

- Ejercicios programación PIC16F84 control motoresDocument3 pagesEjercicios programación PIC16F84 control motoresRoberto Andres Ruiz Pereira100% (1)

- Mapas de Karnaugh PaperDocument7 pagesMapas de Karnaugh PaperJhonJaraNo ratings yet

- PIC16F877A GuíaDocument74 pagesPIC16F877A GuíaCarliTos Javier100% (1)

- Diseño Flip FlopDocument8 pagesDiseño Flip FlopLuis GonzálezNo ratings yet

- Unit 2 - Clasificacion Por Estructura PLCDocument26 pagesUnit 2 - Clasificacion Por Estructura PLCJaret GarciaNo ratings yet

- Modeladoy SimulacionDocument36 pagesModeladoy Simulacionanblor71No ratings yet

- TECLADO MATRICIAL 4X4 CON ARDUINODocument10 pagesTECLADO MATRICIAL 4X4 CON ARDUINOBabyGirl78No ratings yet

- PRÁCTICA 9 FLIP-FLOPSDocument18 pagesPRÁCTICA 9 FLIP-FLOPSChamín AlcántaraNo ratings yet

- Divisor de 4 Bits en VHDLDocument5 pagesDivisor de 4 Bits en VHDLJorge Almaguer100% (1)

- Informe Control PidDocument9 pagesInforme Control PidByron ArgosNo ratings yet

- Contador VHDLDocument6 pagesContador VHDLAntonio PérezNo ratings yet

- Presentacion PLDsDocument112 pagesPresentacion PLDsAlejandro BejaranoNo ratings yet

- LatchesDocument9 pagesLatchesFabio LópezNo ratings yet

- Zero CrossingDocument3 pagesZero CrossingEiverPaltaNo ratings yet

- Ejercicios de electrónica de potencia en microrred autónomaDocument6 pagesEjercicios de electrónica de potencia en microrred autónomaRicardo BarrionuevoNo ratings yet

- Control Pid DiscretoDocument8 pagesControl Pid DiscretoDanny Ochoa Correa100% (4)

- Resolucion Examen FinalDocument8 pagesResolucion Examen FinalGustavo Cadillo RamirezNo ratings yet

- Registros de desplazamiento y dispositivos lógicos programablesDocument7 pagesRegistros de desplazamiento y dispositivos lógicos programablescarranzabustinza50% (2)

- Máquina de Moore y Mealy para detectar códigos repetidosDocument9 pagesMáquina de Moore y Mealy para detectar códigos repetidosOmar LlambaNo ratings yet

- Laboratorio N°8 SC2Document4 pagesLaboratorio N°8 SC2Brayan VQ100% (1)

- Registros de DesplazamientoDocument30 pagesRegistros de Desplazamientoabeat_1100% (2)

- Practica 8G2 Contador Sincrono FlipFlop DLDocument4 pagesPractica 8G2 Contador Sincrono FlipFlop DLAlexander Robles CaicedoNo ratings yet

- ELT2680 Tema11 MAQ ESTADODocument47 pagesELT2680 Tema11 MAQ ESTADOAlex Jhoel Uzeda TorrezNo ratings yet

- GogogogoDocument18 pagesGogogogoJose Angel LeonNo ratings yet

- Máquinas de Estados PDFDocument13 pagesMáquinas de Estados PDFjosmarsonicNo ratings yet

- Diseno Digital Com VHDLDocument23 pagesDiseno Digital Com VHDLOmar TrejoNo ratings yet

- Diagrama de Estado y Tabla de EstadoDocument9 pagesDiagrama de Estado y Tabla de EstadoErick AlexanderNo ratings yet

- Máquina de EstadosDocument4 pagesMáquina de EstadosRodrigo TavaerzNo ratings yet

- Amef 3Document74 pagesAmef 3Francisco Javier Herrera HernandezNo ratings yet

- Estrategia 1Document25 pagesEstrategia 1Francisco Javier Herrera HernandezNo ratings yet

- Serie Asincrona en CDocument17 pagesSerie Asincrona en CAlejandro GuzmánNo ratings yet

- Polimeros Previo PDFDocument30 pagesPolimeros Previo PDFAlejandra Sarabia100% (1)

- Capitulo 1 PDFDocument48 pagesCapitulo 1 PDFFrancisco Javier Herrera HernandezNo ratings yet

- Arquitectura de Von NeumannDocument4 pagesArquitectura de Von NeumanncxgarcianNo ratings yet

- Pic 16F877Document9 pagesPic 16F877Jave Zabdiel Hernandez MarinNo ratings yet

- Circuito 555 Biestable: Análisis y AplicacionesDocument16 pagesCircuito 555 Biestable: Análisis y AplicacionesÁlvaro Adrián Bahamonde BahamondeNo ratings yet

- Arquitectura Del Computador Lab 1Document14 pagesArquitectura Del Computador Lab 1Jess Gabriel RojasNo ratings yet

- Lab 4Document7 pagesLab 4Marco Antonio Ergueta YujraNo ratings yet

- Arduino ArquitecturaDocument8 pagesArduino ArquitecturaJosito HNNo ratings yet

- Silabo Electrónica DigitalDocument6 pagesSilabo Electrónica DigitalGuido MartinezNo ratings yet

- Digitales Practica 6Document10 pagesDigitales Practica 6Joan RuizNo ratings yet

- Sistemas Digitales Lab 1Document11 pagesSistemas Digitales Lab 1Gerson OvalleNo ratings yet

- Motherboard (Placa Madre)Document8 pagesMotherboard (Placa Madre)Paula PereyraNo ratings yet

- Sebastian-Barrios-Control 5 Electronica2Document5 pagesSebastian-Barrios-Control 5 Electronica2Sebastian BarriosNo ratings yet

- Procesador VHDL PDFDocument199 pagesProcesador VHDL PDFIron PeñaNo ratings yet

- Curso Básico de Microcontroladores PICDocument50 pagesCurso Básico de Microcontroladores PICEdison Correa0% (1)

- Microcontroladores Unidad 2Document13 pagesMicrocontroladores Unidad 2Fredd AlvarezNo ratings yet

- Que Significa TTL y CMOS PDFDocument5 pagesQue Significa TTL y CMOS PDFgtranNo ratings yet

- Documento PDFDocument15 pagesDocumento PDFDe la Cruz Ortiz Paulo CesarNo ratings yet

- PRÁCTICA No. 8 CONTADORES DIGITALESDocument4 pagesPRÁCTICA No. 8 CONTADORES DIGITALESCruz Vázquez Byorn axelNo ratings yet

- Cerradura Electrónica DigitalDocument22 pagesCerradura Electrónica Digitalthelords_94No ratings yet

- Infineon IR2110 DataSheet v01 - 00 EN 1731327.en - EsDocument18 pagesInfineon IR2110 DataSheet v01 - 00 EN 1731327.en - Esjhon130296No ratings yet

- Problemas de Sistemas DigitalesDocument109 pagesProblemas de Sistemas DigitalesJuan GarciaNo ratings yet

- Actividad 1 SenaDocument5 pagesActividad 1 SenaDaniela Peña NiñoNo ratings yet

- Guia de Ejercicios 2Document3 pagesGuia de Ejercicios 2Ricardo GarciaNo ratings yet

- Tarea 5 Analizar y Determinar La Organización Del Procesador.Document8 pagesTarea 5 Analizar y Determinar La Organización Del Procesador.Lissie Dianela Chuc UicabNo ratings yet

- Lab. #05 Acevedo Briones TrafosDocument13 pagesLab. #05 Acevedo Briones TrafosHerNan Acevedo QuispeNo ratings yet

- Leccion Grupal Grupo C Digital PDFDocument17 pagesLeccion Grupal Grupo C Digital PDFDavis SisalemaNo ratings yet

- Guia Ets Comp 04Document9 pagesGuia Ets Comp 04Aldo CapistranNo ratings yet

- Práctica 1.0Document50 pagesPráctica 1.0DIEGO JESUS GARCIA CEDILLONo ratings yet

- VHDL para La Simulacion de Circuitos SecuencialesDocument2 pagesVHDL para La Simulacion de Circuitos SecuencialesfrandyNo ratings yet

- MemoriaDocument101 pagesMemoriaCristhian Flores ReyesNo ratings yet

- Revista Digital Leoger ServelionDocument8 pagesRevista Digital Leoger ServelionLeoger ServelionNo ratings yet