Professional Documents

Culture Documents

Us 6721207

Uploaded by

Saurabh ChoudharyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Us 6721207

Uploaded by

Saurabh ChoudharyCopyright:

Available Formats

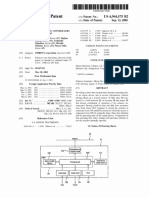

US006721207B2

(12) United States Patent

(10) Patent N0.:

(45) Date of Patent:

Tsujikawa et al.

(56)

(54) NON-VOLATILE MEMORY SYSTEM

US 6,721,207 B2

*Apr. 13, 2004

References Cited

INCLUDING A CONTROL DEVICE TO

U.S. PATENT DOCUMENTS

CONTROL WRITING, READING AND

STORAGE AND OUTPUT OPERATIONS OF

NON-VOLATILE DEVICES INCLUDING

MEMORY CELLS AND DATA LATCHES

5,570,315 A

5,602,789 A

5,761,122 A

5,768,191 A

(75) Inventors: Tetsuya Tsujikawa, Hamura (JP);

5,870,218 A

5,982,667 A

Atsushi Nozoe, Hino (JP); Michitaro

Kanamitsu, Ome (JP); Shoji Kubono,

Akishima (JP); Eiji Yamamoto,

4/2001 Sato et al.

5/2001

JP

JP

(JP); Hitachi ULSI Systems Co., Ltd.,

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 10/211,342

Aug. 5, 2002

(22) Filed:

Prior Publication Data

(65)

11, 2001, now Pat. No. 6,507,520, which is a continuation of

application No. 09/539,633, ?led on Mar. 30, 2000, now Pat.

No. 6,233,174, which is a continuation of application No.

09/250,157, ?led on Feb. 16, 1999, now Pat. No. 6,046,936.

(51)

(52)

(58)

Primary ExaminerHoai Ho

(74) Attorney, Agent, or FirmAntonelli, Terry, Stout &

Kraus, LLP

ABSTRACT

device and non-volatile memory devices, each including

Continuation of application No. 10/011,723, ?led on Dec.

Foreign Application Priority Data

(JP)

Flash MemoryMultiLevel Memory, US Makers Set

About Technological Development Precedent and Bring to

the Commercial Stage in 1995, Getting Over Reliability,

A non-volatile memory system is provided with a control

Related US. Application Data

Feb. 16, 1998

5/1987

11/1997

OTHER PUBLICATIONS

(57)

US 2002/0191459 A1 Dec. 19, 2002

(30)

62-099996

9297996

(with English translation).

This patent is subject to a terminal dis

claimer.

(63)

McGoldrick et al. ..... .. 711/103

FOREIGN PATENT DOCUMENTS

Tokyo (JP)

Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

365/185.21

2/1999 Jyouno et al. ....... .. 365/18503

11/1999 Jyouno et al. ....... .. 365/185.22

6,226,708 B1

(JP)

Notice:

6/1998 Nakamura et al.

6/1998 ch01 et al.

6,222,763 B1

Kodaira (JP); Ken Matsubara, Ome

(73) Assignees: Renesas Technology Corp., Tokyo

10/1996 Tanaka et al. ....... .. 365/185.22

2/1997 Endoh et al. ........ .. 365/185.03

........................................... .. 10-32776

Int. Cl.7 .............................................. .. G51C 16/04

US. Cl. ............................ .. 365/185.28; 365/185.29

Field of Search ..................... .. 365/185.28, 185.29,

memory cells and data latches. The control device supplies

commands to the non-volatile memory devices, including a

write command, and ?rst and second read commands. When

the control device supplies the write command with write

address information and data for storing in the non-volatile

memory device, it stores the data to the data latches and then

to the memory cells, and then veri?es storage. When the

control device supplies the ?rst read command with read

address information, the nonvolatile memory device reads

data stored in the memory cells to the data latches and then

outputs the data in the data latches to the control device.

When the control device supplies the second read command,

the non-volatile memory device outputs data in the data

latches to the control device.

4 Claims, 57 Drawing Sheets

365/18501

MEMORY MAIv

DATA LATCH

CIRCUIT

SENSE LATCH

CRCUW

5* L

MODE CONIROL CWT/UH

STATUS REGISIHJ

U.S. Patent

Apr. 13, 2004

Sheet 1 0f 57

3 4

US 6,721,207 B2

f3

MEMORY MAT,

DATA LATCH

ADDREss

BUFFER

ADDRESS

DECODER

CIRCUIT,

SENSE LATCH

CIRCUIT

I

7\

17

I/OOII?

I MULTI

V07

PLEXER-

*7 INPUTS

16 (Ff-3%)

21

1' DRTA )

BUFFER

R/Bb

\11

2' COUNTER v12

CEb

18

2O

CONIAFEOL

S

BUFFER +MODE CONTROL CIRCUIT

,

gggggcmcm sTATUs REGISTER I

M;

Y ADDRESS 7

SIGN

BUFFER

F DEcoDER .

3g;S0

Y ADDREss

N L

x2:

I YAR(RATEDIRDUTT/

0 UTPUT

Y

3%?

~"

Q _ ______A,)\_/5

r13

180

* INTERNAL POWER

21

5f+

SUPPLY CIRCUlT

,_

U.S. Patent

Apr. 13, 2004

US 6,721,207 B2

Sheet 2 0f 57

CONTROL GATE

POTENTIAL

FIG. 2

/CG

CONTROL GATE

FG

INTERLAYER

INSULATING FILM

SOURCE

POTENTIAL

S\ *

J DRAIN

FLOATING GATE

POTENTIAL

TUNNEL OXIDE FILM

SOURCE

I DRAIN _/0

MEMORY WELL

WELL POTENTIAL

sue

MODE

FIRST

COMMAND

SECOND

COMMAND

READ

OUR

NO NEED

RECOVERY

READ

01H

NO NEED

EHASE

20H

BOH

PROGRAM

TFR

40H

ADDITIONAL

PROGRAM

RETRY

PROGRAM

PARTIAL

ERASE

0H

40H

IAH

NO NEED

2FH

BOH

REWRITE

11H

40H

U.S. Patent

Apr. 13, 2004

Sheet 3 0f 57

US 6,721,207 B2

FIG. 4

TITLE

DEFINITION

1/07 Ready/IE?

VOH=Ready VOL"=Busy

I/O6 Reserved

[/05 Erase Check

VoH"=Fai| VOL:Pass

1/04 Program Check VOH"=FaIl VOL"=Pass

[/03 Reserved

I/O2 Reserved

I/ O1

Reserved

[/00 Reserved

STATUS REGISTER

U.S. Patent

Apr. 13, 2004

US 6,721,207 B2

Sheet 5 0f 57

FIG. 6

PROGRAM

DATA

DLL

DLR

DOA OD

11

VWV3

VH3 ------------ -

VH2 ------------

vm

-- ---------- -

VWE2

VWV2

VWE1

VWV1

VWDS

OV

MEMORY CELL

NUMBER

U.S. Patent

Apr. 13, 2004

Sheet 6 0f 57

US 6,721,207 B2

FIG. 8

-17v

SELECTED

wORD LINE

----------

SEOTOR

BATCH

ERASE

0V

5 +111

P11 j=

-----------

(1 WORD ERASE

AT SAME TIME)

&

&

0v

IN

NON-SELECTED

WORD LINE

IN

SELECTED

WORD LINE

---------

WRITE EvERY

BIT

0v

(1 WORD WRITE

AT SAME TIME)

NONSELECTED

wORD LINE

J:

W

SELECTED

W

NON-SELECTED

BIT LINE

BIT LINE

OPERATION VOLTAGE

FIG. 9

WHITE

Case1

(1)

Case2

Case3

(3)

Case4

(3)

CaSeS

(2)

(3)

(31 (HT (1)

I I I

ERASING STATE

I II

U.S. Patent

Apr. 13, 2004

Sheet 8 0f 57

US 6,721,207 B2

FIG. 1 1

AND TYPE

MEMORY MAT

M1

l

/ SOURCE LINE

SDI BIT LINE

(CONTROL GATE) FIJI [

WL (WORD LINE)

1|

j.

WL (WORD LINE)

SUB-BIT LINE

'l;_ ._ ;.j>'/

/\/MC

mv/

i

_T_

{MC

g)

klzqvMc AL-LI SUB-BIT LINE

l

WL (WORD LINE)

11/ MC

farm

SSi (sOuRcE LINE

CONTROL GATE)

MC\

wORO

WORD LINE

WORO LINE

WORO LINE MCf

1 /\/M2

ILL

BIT LINE

NEARIIOTFIIFTMAT

__

01

BIT LINE

SOURCE LINE

u-"

A\_/MC

AVMC

'

BIT LINE

BIT LINE

U.S. Patent

Apr. 13, 2004

Sheet 9 0f 57

US 6,721,207 B2

DiNOR TYPE

MEMORY MAT

>-SOURCE LINE

WORD LINE

\_,MC

WORD LINE

WORD LINE

Hp/MC

WORD NE

SUB-BIT LINE

.5

FF

5 '

WORD LINE

.:

_j

\\_M_(_;--.

SELECTED GATE-

_j

4| \MC

____ _-__I

BIT LINE

BIT UNE

NAND TYPE

MEMORY MAT

sOuRcE LINE

r1

CONTROL GATE

---- --

ME"

SOURCE LINE

2]

WORD LINE -#/::i .... --_.__ WMC

WORD LINE

II

..... ..__D|

WORD LlNE-

----- --___|| WMC

WORD LINE-

\ M-_-___I|

'

WORD LINE ~7

12/ MC

I

BIT LINE

____ .____" \\_MC

.... -.

OONTROL GATE

.,_5

BIT LINE

BIT LINE

U.S. Patent

Apr. 13, 2004

HiCFI TYPE

MEMORY MAT

BIT LINE

SOURCE LINE

CONTROL GATE

Sheet 10 0f 57

"Jab

T|| MC

WORD LINE

SUB-SOURCE

LINE

\<~

SOURCE LINE

TLII

II_

II'TF"

rJl MC

l

Fur/MC

US 6,721,207 B2

,7

WORD LINE

Ii

MC

ITLI.

BIT LINE

CONTROL GATE

r71

SUB-BIT MM??WORD LINE

IL_

TTLI

5% Q

___

._

__

MC5"

BIT LINE

{MC

MC5H'TT

BIT LINE BIT LINE

LL

AMC

BIT LINE

U.S. Patent

Apr. 13, 2004

FETCH FIRST COMMAND

Sheet 11 0f 57

5'81

US 6,721,207 B2

'

FETCH SECTOR ADDRESS FSQ

TS

'01-

FETCH PROGRAM DATA

53

FETCH SECOND COMMAND

84

LATCH '01" DATA

5 PROGRAM '00- DATA

5

5 (SEE FIG 23)

=

PROGRAMING 5

OPERATION -;

:

:

VERIFY vwv3

FAIL;

g

?

I

-_,-._PP_S_S_ ________________ _.

T52

'

LATCH '00" DATA

11' WORD

?lswwgggcm

FAIL

T84

________________________ _'

PROGRAM *oo- DATA

ERRATIC/

PROGRAMING

OPERATION

T53

"0'

PROGRAMING

OPERATION

OISTURB

DETECTION

OPERATION

LATCH '10 DATA

P OGRAM "1()' DATA

SET PASS FLAG

TO STATUS

55? REGISTER

I

SET FAIL FLAG

,38

TO STATUS

I

REGISTER

I

( END TOTO) CENDINGI)

PROGRAM FLOW (CASE 1)

U.S. Patent

Apr. 13, 2004

Sheet 12 0f 57

FIG. 17

Vth

VWV3

> "01"

---------------- __

> "H"

BIT NUMBER

"01" PROGRAM DATA

FIG. 18

Vlh 1

> ~01

WW2

BIT NUMBER

7190i EBQQBAM DATA

US 6,721,207 B2

U.S. Patent

Apr. 13, 2004

Sheet 13 0f 57

FIG. 19

BlT NUMBER

"10" PROGRAM DATA

FIG. 20

V

asm

VWD

0v

,7

_

mun?l"1.M0_m

>

BIT NUMBER

MQ/DISTURB

DETECTION OPERATON

US 6,721,207 B2

U.S. Patent

Apr. 13, 2004

Sheet 14 0f 57

US 6,721,207 B2

FIG. 21

DATA LATCH PROCESS

CALCULATION CONTENT

(SENSE LATCH DATA OF

SELECTED MAT SIDE)

'01- PROGRAM DATA

A+

'00" PROGRAM DATA

A+B

'10" PROGRAM DATA

5+8

"0o" ERRATIC DETECTION DATA

A+B_

"10" ERRATIC DETECTION DATA

A .

'11" DIsTuRB DETECTION DATA

A - B

A: UPPER DlGlT DATA

BILOWER DIGIT DATA

FIG. 22

UPIIXDER LOIENER A+B' A+B K+B m A-' A-B

DIGIT

0

DIGIT

1

'I

U.S. Patent

Apr. 13, 2004

Sheet 15 0f 57

US 6,721,207 B2

START '01" PROGRAMING

OPERATION

5 S101

?

-

I

EXECUTE DATA LATCH

PROcEss

-_

8'11 APPLY "o1" PROGRAMING

BIAS VOLTAGE

7

S121

EXECUTE PROGRAM

VERIFY vwvs

813

ALL

JUDGIEIAENT

PASS

END "01" PROGRAMING)

OPERATION

sTART "I0" ERRATIO

DETECTION

II

EXECUTE DATA LATCH

S201

5

E

PROCESS

I

E

I

5211

EXECUTE ERRATIO

VERIFY VWE1

522

\-

ALL

\\

FAIL

JUDGMENT

PASS

END "10" ERRATID

DETECTION

l

' _

-__l

U.S. Patent

Apr. 13, 2004

Sheet 17 0f 57

US 6,721,207 B2

5a2%:5a2

a:

28mSm5%g2m5Mi?

ED59am

/3Q02i06.%53

/\

>45?

REELE5%52081

6Emm

a36y013/0m01>a1m>0%m0a..a30%

a2$0%253

3IE5185%

g

5

2

3

$

g

m

:

w

z

o

?

5

.

c

f

m

g

w

325m23m2%

$<E52m730s5

-w@3<_25.180m owa'skm%wa m

e2

22.00

023.00w23

O

2;_gS

053:20P

6i?

a:

O00

29::

P6:2

S2F3220

Q

gos2 122

O

a:

2%?

10:2

Q

P

2

F

_

3

:93:

a:

O

F

f

200

2020

O

:22.

2

F

P

f

0.0

0

23.00

:

50

Q

F

P6%E53E2.$5S02E5%2

U.S. Patent

Apr. 13, 2004

Sheet 18 0f 57

wgm5w3?oz:w5fm@i06zoq?mw

5%EB250%

3m06%5%@55m2 0m,5

W

6138E6%

on;0%

\\/

1151112112144,

.I....\-

v3xj6a83m.sQ2% 55m2%23m0%

i

2.6. x

To23Q

2<5E20635 3-g2mm3rm%a5

US 6,721,207 B2

mR),|IU\h_LuH

Wmw?hniuao

3:30

200

22

i:o0.0OI;C0PQ52;F302g

30@o@IOPFf02263O8g:932;0: 3103o6:0FOrP29112029.:0;:

01gO2?o0PZr3Fd:_.:1i2"%g:o8;.

2w5$:<smb0z681xowr5im?0z2v

U.S. Patent

Apr. 13, 2004

Sheet 19 0f 57

on;0%

50To22HMaw/,.

m2$85%EDm5To.

.mTOEE

\\\_T$iEO3%3m._2@i&

w

g\86u. m33m\2

$052i03%$250%5%mag

55as95%

93m25m5%03%ism1m2amgm EwQ5Z3UzWI1.OfEm?Za

<Em5w2,z3sig

m35.61035%.?

0%

Hm)UuLRw

wmanoq?

US 6,721,207 B2

we?

o3iozo:a:of003ZeroP6:?09.0oQFo:22z9mdo a:

I322O2:2;OF200:50i;I:2i

:52;F

05OF22L0Q0g.210;:29::a;@I3Q0PO@22F981a3;:98;: @38525$986%5m3.KEg m

Aw8z15c2s

You might also like

- How to Find Out About Patents: The Commonwealth and International Library: Libraries and Technical Information DivisionFrom EverandHow to Find Out About Patents: The Commonwealth and International Library: Libraries and Technical Information DivisionNo ratings yet

- From Invention to Patent: A Scientist and Engineer's GuideFrom EverandFrom Invention to Patent: A Scientist and Engineer's GuideNo ratings yet

- Non-volatile memory device status detectionDocument75 pagesNon-volatile memory device status detectionSaurabh ChoudharyNo ratings yet

- Us6944575Document49 pagesUs6944575Anonymous KiraNo ratings yet

- United States Patent: (10) Patent No.: US 6,957,339 B2Document43 pagesUnited States Patent: (10) Patent No.: US 6,957,339 B2Alex MungaiNo ratings yet

- Us7997527 PDFDocument11 pagesUs7997527 PDF雷黎明No ratings yet

- Ulllted States Patent (10) Patent N0.: US 8,516,483 B2Document19 pagesUlllted States Patent (10) Patent N0.: US 8,516,483 B2david19775891No ratings yet

- United States Patent: (12) (10) Patent No.: US 7.464,653 B2Document20 pagesUnited States Patent: (12) (10) Patent No.: US 7.464,653 B2marcoNo ratings yet

- US5715376Document137 pagesUS5715376ztakahashiNo ratings yet

- United States Patent: (10) Patent No.: US 8,218,501 B2Document25 pagesUnited States Patent: (10) Patent No.: US 8,218,501 B2Know-7No ratings yet

- Aircraft Software Part Library ManagementDocument96 pagesAircraft Software Part Library Managementdavid19775891No ratings yet

- United States Patent: Shah-HosseiniDocument28 pagesUnited States Patent: Shah-Hosseinidavid19775891No ratings yet

- United States Patent: AugustoDocument18 pagesUnited States Patent: AugustocherniNo ratings yet

- United States Patent: Bourdon Et A) - (10) Patent N0.: (45) Date of PatentDocument14 pagesUnited States Patent: Bourdon Et A) - (10) Patent N0.: (45) Date of Patentdavid19775891No ratings yet

- 59 0f1-,-,,é - 1,, M 13,553 $525113ei Iiii?if III Fifit 21811101511121.1118Document22 pages59 0f1-,-,,é - 1,, M 13,553 $525113ei Iiii?if III Fifit 21811101511121.1118Qwerty UiopNo ratings yet

- United States Patent: Cheng Et Al. (10) Patent No.: US 9,078,547 B2Document10 pagesUnited States Patent: Cheng Et Al. (10) Patent No.: US 9,078,547 B2Alex BrcNo ratings yet

- US7156267Document7 pagesUS7156267Efabind OtNo ratings yet

- US7963479Document10 pagesUS7963479雷黎明No ratings yet

- United States Patent Patent No.: US8 215,454 B2: Portlock Et Al 10) 45) Date of Patent Jul. 10, 2012Document13 pagesUnited States Patent Patent No.: US8 215,454 B2: Portlock Et Al 10) 45) Date of Patent Jul. 10, 2012anhntran4850No ratings yet

- Ulllted States Patent (10) Patent N0.: US 8,555,288 B2Document82 pagesUlllted States Patent (10) Patent N0.: US 8,555,288 B2david19775891No ratings yet

- United States Patent (19) 11 Patent Number: 6,064,708: Sakamaki (45) Date of Patent: May 16, 2000Document16 pagesUnited States Patent (19) 11 Patent Number: 6,064,708: Sakamaki (45) Date of Patent: May 16, 2000Rumi Kai RekaNo ratings yet

- US7741796Document9 pagesUS7741796ALiftsNo ratings yet

- United States Patent (10) Patent No.: US 8,024,070 B2Document7 pagesUnited States Patent (10) Patent No.: US 8,024,070 B2CY LiuNo ratings yet

- 2010 - Us7721821 - Underground Boring Machine and Method For Controlling Underground BoringDocument13 pages2010 - Us7721821 - Underground Boring Machine and Method For Controlling Underground BoringCường Nguyễn QuốcNo ratings yet

- United States Patent 19 11 Patent Number: 5,726,911: Canada Et Al. 45 Date of Patent: Mar. 10, 1998Document14 pagesUnited States Patent 19 11 Patent Number: 5,726,911: Canada Et Al. 45 Date of Patent: Mar. 10, 1998sebastianNo ratings yet

- United States Patent: (12) (10) Patent N0.: US 7,266,518 B2Document11 pagesUnited States Patent: (12) (10) Patent N0.: US 7,266,518 B2Marii WataNo ratings yet

- United States Patent: Motohama Et A) - (10) Patent N0.: (45) Date of PatentDocument16 pagesUnited States Patent: Motohama Et A) - (10) Patent N0.: (45) Date of Patentdavid19775891No ratings yet

- US7992581Document17 pagesUS7992581Ragil YogaNo ratings yet

- 289 Floating Floor Slab Holders - US8505267Document9 pages289 Floating Floor Slab Holders - US8505267gmpintorNo ratings yet

- Cutting and transfer drum in a continuous-film labeling machineDocument6 pagesCutting and transfer drum in a continuous-film labeling machineErin GokNo ratings yet

- Tesla Patent ACCELERATED MATHEMATICAL ENGINEDocument12 pagesTesla Patent ACCELERATED MATHEMATICAL ENGINECharles GrossNo ratings yet

- United States Patent: Mcclure Et Al. (45) Date of Patent: Aug. 3, 2004Document35 pagesUnited States Patent: Mcclure Et Al. (45) Date of Patent: Aug. 3, 2004MaiChiVuNo ratings yet

- United States Patent: (10) Patent No.: (45) Date of PatentDocument27 pagesUnited States Patent: (10) Patent No.: (45) Date of PatentAlberto Esau Reyes CruzNo ratings yet

- Us 6758544Document16 pagesUs 6758544norbertscribdNo ratings yet

- United States Patent: (10) Patent No.: US 8.457,550 B2Document24 pagesUnited States Patent: (10) Patent No.: US 8.457,550 B2charitablegrinderNo ratings yet

- United States Patent: (10) Patent No.: US 9,131,338 B2Document18 pagesUnited States Patent: (10) Patent No.: US 9,131,338 B2Teju AshuNo ratings yet

- United States Patent (10) Patent No.: US 7489,225 B2: Dadafshar (45) Date of Patent: Feb. 10, 2009Document24 pagesUnited States Patent (10) Patent No.: US 7489,225 B2: Dadafshar (45) Date of Patent: Feb. 10, 2009Jie99No ratings yet

- United States Patent: (10) Patent No.: (45) Date of PatentDocument35 pagesUnited States Patent: (10) Patent No.: (45) Date of PatentLazlo JoószNo ratings yet

- INDUCTION IRONING TITLEDocument20 pagesINDUCTION IRONING TITLERonan RojasNo ratings yet

- US8851163B2 patent for multiple offset slim wellhead connectorDocument15 pagesUS8851163B2 patent for multiple offset slim wellhead connectorDiseno VATNo ratings yet

- United States Patent (19) : 11 Patent Number: 5,755,291 45) Date of Patent: May 26, 1998Document21 pagesUnited States Patent (19) : 11 Patent Number: 5,755,291 45) Date of Patent: May 26, 1998Justus VenterNo ratings yet

- Unit Structure For Hazard SwitchDocument15 pagesUnit Structure For Hazard SwitchKawaljeet SinghNo ratings yet

- Senographe 600thf AsmDocument120 pagesSenographe 600thf Asmjesus medranoNo ratings yet

- United States Patent (10) Patent No.: US 7,594,010 B2Document58 pagesUnited States Patent (10) Patent No.: US 7,594,010 B2KrozeNo ratings yet

- Us 7748384Document28 pagesUs 7748384himanshi413No ratings yet

- United States Patent: Kotsopoulos Et Al. (45) Date of Patent: Apr. 18, 2006Document10 pagesUnited States Patent: Kotsopoulos Et Al. (45) Date of Patent: Apr. 18, 2006Taufiq AhmadNo ratings yet

- Segmented Bearing BushingDocument12 pagesSegmented Bearing BushingAnonymous 2k25WMLY0No ratings yet

- Ulllted States Patent (10) Patent N0.: US 8,489,847 B2Document12 pagesUlllted States Patent (10) Patent N0.: US 8,489,847 B2david19775891No ratings yet

- United States Patent: Heishi Et AlDocument12 pagesUnited States Patent: Heishi Et AlwelsyaNo ratings yet

- CTP in PhunDocument30 pagesCTP in Phunlong trịnhNo ratings yet

- Us6230368 PDFDocument9 pagesUs6230368 PDFSantoshNo ratings yet

- United States Patent: Matsushita Et AlDocument25 pagesUnited States Patent: Matsushita Et AlEl Kanouani ZakariaNo ratings yet

- A086557 PDFDocument313 pagesA086557 PDFK11E77No ratings yet

- United States Patent (10) Patent No.: US 7,134,558 B1: Mimlitch, III Et Al. (45) Date of Patent: Nov. 14, 2006Document22 pagesUnited States Patent (10) Patent No.: US 7,134,558 B1: Mimlitch, III Et Al. (45) Date of Patent: Nov. 14, 2006Erin GokNo ratings yet

- USAF Stability and Control Digital Datcom Users ManualDocument313 pagesUSAF Stability and Control Digital Datcom Users ManualFabian ZenderNo ratings yet

- Vacuum Insulated Beverage DispenserDocument13 pagesVacuum Insulated Beverage DispenserGabriel RochaNo ratings yet

- Quick Connector and CheckerDocument41 pagesQuick Connector and CheckerTUNCAY GUMUSNo ratings yet

- United States Patent (10) Patent No.: US 7,769,145 B2: Melide0 (45) Date of Patent: Aug. 3, 2010Document18 pagesUnited States Patent (10) Patent No.: US 7,769,145 B2: Melide0 (45) Date of Patent: Aug. 3, 2010Andrew StarkNo ratings yet

- Quick Connector With A Sensor HousingDocument11 pagesQuick Connector With A Sensor HousingTUNCAY GUMUSNo ratings yet

- United States Patent: (12) (10) Patent N0.: US 7,367,396 B2 Springett Et Al. (45) Date of Patent: May 6, 2008Document24 pagesUnited States Patent: (12) (10) Patent N0.: US 7,367,396 B2 Springett Et Al. (45) Date of Patent: May 6, 2008HKHKBOOKSNo ratings yet

- Gita Press Invoice - 22165Document1 pageGita Press Invoice - 22165Saurabh ChoudharyNo ratings yet

- Gita Press Invoice - 22165Document1 pageGita Press Invoice - 22165Saurabh ChoudharyNo ratings yet

- Terms and ConditionsDocument1 pageTerms and ConditionsSaurabh ChoudharyNo ratings yet

- R Nagaswamy - Art and Religion of The Bhairavas - Illumined by Two Rare Sanskrit Texts Sarva-siddhānta-Vivēka and Jñāna-siddhi-Tamil Arts AcademyDocument355 pagesR Nagaswamy - Art and Religion of The Bhairavas - Illumined by Two Rare Sanskrit Texts Sarva-siddhānta-Vivēka and Jñāna-siddhi-Tamil Arts AcademySaurabh ChoudharyNo ratings yet

- Narendra Nath Bhattacharyya History of The Tantric ReligionDocument484 pagesNarendra Nath Bhattacharyya History of The Tantric ReligionFrater Legbha100% (14)

- Saiva Siddantha ConferenceenglishDocument3 pagesSaiva Siddantha ConferenceenglishSaurabh ChoudharyNo ratings yet

- Walter Russell - The Secret of LightDocument163 pagesWalter Russell - The Secret of Lighttombosliekamp98% (53)

- Selected Writings of Mahamahopadhyaya Gopinath KavirajDocument205 pagesSelected Writings of Mahamahopadhyaya Gopinath Kavirajchetanpandey100% (5)

- Walter Russell - A New Concept of The UniverseDocument98 pagesWalter Russell - A New Concept of The Universefredtyler9100% (1)

- Mr. Gousal Azam: 7978466567 Mr. Varender Beri: 7065044985Document1 pageMr. Gousal Azam: 7978466567 Mr. Varender Beri: 7065044985Saurabh ChoudharyNo ratings yet

- Payment ReceiptDocument1 pagePayment Receiptraj biradarNo ratings yet

- Payment ReceiptDocument1 pagePayment Receiptraj biradarNo ratings yet

- Great Systems of Yoga: Ernest WoodDocument86 pagesGreat Systems of Yoga: Ernest WoodparagNo ratings yet

- JD - GPL - Strategic InitiativesDocument4 pagesJD - GPL - Strategic InitiativesSaurabh ChoudharyNo ratings yet

- Us 8346894Document26 pagesUs 8346894Saurabh ChoudharyNo ratings yet

- Petition 2Document84 pagesPetition 2Saurabh ChoudharyNo ratings yet

- Us 7808483Document16 pagesUs 7808483Saurabh ChoudharyNo ratings yet

- Cost ManagementDocument7 pagesCost ManagementSaurabh ChoudharyNo ratings yet

- Us 7505406Document12 pagesUs 7505406Saurabh ChoudharyNo ratings yet

- Us 6947748Document19 pagesUs 6947748Saurabh ChoudharyNo ratings yet

- Us 6931128Document15 pagesUs 6931128Saurabh ChoudharyNo ratings yet

- United States Patent: (12) (10) Patent N0.: US 6,911,652 B2Document6 pagesUnited States Patent: (12) (10) Patent N0.: US 6,911,652 B2Saurabh ChoudharyNo ratings yet

- Smart CityDocument3 pagesSmart CitySaurabh ChoudharyNo ratings yet

- Nestle HeroesDocument5 pagesNestle HeroesSaurabh ChoudharyNo ratings yet

- Us 6744692Document22 pagesUs 6744692Saurabh ChoudharyNo ratings yet

- 2013-GEIPER Holiday CalenderDocument3 pages2013-GEIPER Holiday CalenderSaurabh ChoudharyNo ratings yet

- DLC Lab QP Oct2019Document5 pagesDLC Lab QP Oct2019bnatarajNo ratings yet

- Principles of Compiler Design 2001 Regulations CS337Document2 pagesPrinciples of Compiler Design 2001 Regulations CS337Monica NareshNo ratings yet

- SP PDFDocument2 pagesSP PDFPRAYAGRAJ PandyaNo ratings yet

- Uc3 Aula 1 Manual Novo Virtual Box 6.1Document242 pagesUc3 Aula 1 Manual Novo Virtual Box 6.1Prof. Tercio RibeiroNo ratings yet

- CS 3853 Computer Architecture - Memory HierarchyDocument37 pagesCS 3853 Computer Architecture - Memory HierarchyJothi RamasamyNo ratings yet

- TTControl TTC - 60 DatasheetDocument2 pagesTTControl TTC - 60 DatasheetalextectomNo ratings yet

- Calculations in A Userform - Excel VBADocument5 pagesCalculations in A Userform - Excel VBAJossli OmarNo ratings yet

- Digital Forensic Analysis of A PlayStation 4 Hard Drive With Links To XRY Mobile ForensicsDocument35 pagesDigital Forensic Analysis of A PlayStation 4 Hard Drive With Links To XRY Mobile ForensicsLuke BarghNo ratings yet

- ALU Command ReferenceDocument209 pagesALU Command ReferenceparthieeeNo ratings yet

- Isd 5116Document52 pagesIsd 5116Rafael AlcazarNo ratings yet

- Microprocessor and Microcontroller Laboratory ManualDocument23 pagesMicroprocessor and Microcontroller Laboratory Manualanand_gudnavarNo ratings yet

- Troubleshooting VMMDocument119 pagesTroubleshooting VMMCash Sly0% (1)

- OOP Concepts Quiz: Encapsulation, Inheritance, PolymorphismDocument5 pagesOOP Concepts Quiz: Encapsulation, Inheritance, PolymorphismShoaib MalikNo ratings yet

- Presentation 5587 1540244493Document41 pagesPresentation 5587 1540244493Bayo HarahapNo ratings yet

- GTU #3130702 Data Structures (DS) Unit 2 - Linked ListsDocument60 pagesGTU #3130702 Data Structures (DS) Unit 2 - Linked ListsDivyes PNo ratings yet

- OBS Reference ManualDocument74 pagesOBS Reference ManualsdfsdffewNo ratings yet

- Acknowledgement: SRS of Clinical Management SystemDocument11 pagesAcknowledgement: SRS of Clinical Management SystemFNMAMSNo ratings yet

- Ol Ict Marking Scheme 2018Document10 pagesOl Ict Marking Scheme 2018supun gamageNo ratings yet

- F5 Solutions Playbook September 2016 PDFDocument92 pagesF5 Solutions Playbook September 2016 PDFlinwintkNo ratings yet

- MELSEC iQ-F FX5 User's Manual Safety PrecautionsDocument266 pagesMELSEC iQ-F FX5 User's Manual Safety PrecautionsghostyguoNo ratings yet

- Windows 10 64 Bit Product Capability MatrixDocument5 pagesWindows 10 64 Bit Product Capability MatrixJorge montañezNo ratings yet

- MSX Computing - Jun-Jul 1986Document68 pagesMSX Computing - Jun-Jul 1986BulesteNo ratings yet

- FALCON X3 Quick Start GuideDocument2 pagesFALCON X3 Quick Start Guidebmx0964No ratings yet

- App PM5200English-OEM-A2 QSG 20120520 CYRUS 20130221030616Document14 pagesApp PM5200English-OEM-A2 QSG 20120520 CYRUS 20130221030616Riski SuhardinataNo ratings yet

- Online Train Ticket Reservation System GADDocument37 pagesOnline Train Ticket Reservation System GADMayur JadhavNo ratings yet

- Ansi C12.21-2006Document79 pagesAnsi C12.21-2006Carol Hernandez100% (1)

- Nagaraj - Salesforce DeveloperDocument5 pagesNagaraj - Salesforce DeveloperthirakannamnagarajaachariNo ratings yet

- Alephnaught Koadic C3Document50 pagesAlephnaught Koadic C3Austral AnglerNo ratings yet

- McAfee SIEM Collector Installation and Configuration v1 2Document19 pagesMcAfee SIEM Collector Installation and Configuration v1 2hemant shekhawatNo ratings yet

- Week 1 Slides - AWS MoocDocument22 pagesWeek 1 Slides - AWS Moockaylia123No ratings yet