Professional Documents

Culture Documents

Non-volatile memory device status detection

Uploaded by

Saurabh ChoudharyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Non-volatile memory device status detection

Uploaded by

Saurabh ChoudharyCopyright:

Available Formats

US006504764B2

(12) United States Patent

(10) Patent N0.:

(45) Date of Patent:

Tsujikawa et al.

(56)

(54) NON-VOLATILE MEMORY DEVICE

U.S. PATENT DOCUMENTS

Atsushi Nozoe, Hino (JP); Michitaro

5,570,315

5,602,789

5,768,191

5,870,218

Kanamitsu, Ome (JP); Shoji Kubono,

Akishima (JP); Eiji Yamamoto,

Kodaira (JP); Ken Matsubara, Ome

(JP)

(73) Assignee: Hitachi, Ltd., Tokyo (JP)

Notice:

*Jan. 7, 2003

References Cited

(75) Inventors: Tetsuya Tsujikawa, Hamura (JP);

(*)

US 6,504,764 B2

A

A

A

A

10/1996

2/1997

6/1998

2/1999

Tanaka et al.

Endoh et al.

(31101 et al.

Jyouno et al.

5,910,918 A

6/1999

5,917,756 A

6,064,606 A

*

*

6/1999 Imamiya et al. ..... .. 365/185.17

5/2000 Kuroda et al. ............ .. 365/200

6,222,763 B1

Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

Hirano ................ .. 365/18516

4/2001 Sato et al.

FOREIGN PATENT DOCUMENTS

JP

U.S.C. 154(b) by 0 days.

9297996

11/1997

OTHER PUBLICATIONS

This patent is subject to a terminal dis

claimer.

Flash MernoryMultiLevel Memory US Makers Set

About Technological Development Precedent and Bring to

the Commerical Stage in 1995, Getting Over Reliability,

(21) Appl. No.: 09/985,116

Nov. 1, 2001

(22) Filed:

Prior Publication Data

(65)

(with English Translation).

* cited by examiner

Primary ExaminerHoai Ho

(74) Attorney, Agent, or FirmAntonelli, Terry, Stout &

Kraus, LLP

US 2002/0027807 A1 Mar. 7, 2002

Related US. Application Data

(63)

(57)

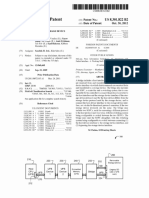

A non-volatile memory device having a plurality of memory

Continuation of application No. 09/820,906, ?led on Mar.

cells and a control circuit. The control circuit receives

30, 2001, now Pat. No. 6,320,793, which is a continuation

of application No. 09/539,633, ?led on Mar. 30, 2000, now

operation commands from outside the device and controls

the operation of the device according to the commands. The

commands include read commands and write commands. In

Pat. No. 6,233,174, which is a continuation of application

No. 09/250,157, ?led on Feb. 16, 1999, now Pat. No.

6,046,936.

(30)

(51)

(52)

(58)

a read command, the control circuit reads data in the

memory cells and outputs it. In a write command, the control

circuit controls the inputting of data to data latch circuits and

then to memory cells. The control circuit provides status

information indicating whether the writing of data is a

Foreign Application Priority Data

Feb. 16, 1998

ABSTRACT

(JP) ........................................... .. 10-32776

Int. Cl.7 .............................................. .. G11C 16/04

US. Cl. ............... ..

365/185.28; 365/185.22

Field of Search ..................... .. 365/185.28, 185.22,

success or a failure.

11 Claims, 57 Drawing Sheets

365/18501

,6

f3

MEMORY MAT,

ADDRESS

ADDRESS

BUFFER

05000511

+

M 2

17

V00

[/07

INPUT

DATA LATCH

0100011,

SENSE LATCH

016000

x

DATA

21

/ 13

2 Y GATE

$15

.1 - CONTROL L ARRAY cmcun ,_ OUTPUT

BUFFER

C|HCU|T

Y ADDRESS

R/Bb

BUFFER

DECODER

\

V06

2 |Y ADDRESS

V55

LOUNTER

CED

OEb

\ 12

(8

WEb

,,

REsslcJ v

MODE CONTROL cmcun _ INTERNAL POWER

CD51,

5110i

1156mm

S

19

180

,i,

2.

11

SUPPLY 010000

t

21

I

17.

U.S. Patent

Jan. 7, 2003

US 6,504,764 B2

Sheet 1 0f 57

FIG. 1

8

{1

MEMORY MAT,

X

DATA LATCH

ADDRESS

ADDRESS

cIRcuIT,

DDEEER

DEcoDER

SENSE LATCH

CIRCUIT

(t/""S""~> <f__" ,i7\_/5

\ N

[/07 I l MULT|_

R/Bb

PIExER :

BUFFER

CIRCUIT

Y ADDRESS

I" DECODER \

2 Y ADDRESS _

V85 1::

CEb

f5

3' |NPUT LEQKXTROL 1% ARRAY C|RCUIT _> OUTPUT

Vcc

OED

E couIITER

I8

CONTROL

BUFFER

11

\42

520

WEb

REgg

SIGNAL

BUFFER + MDDE CONTROL DIRDIIIT

,NTERNAL POWER

CDEb

CIRCUIT

SUPPLY CIRCUIT

>

-* STATUS REG|STER

>

,5

19

180

U.S. Patent

Jan. 7, 2003

US 6,504,764 B2

Sheet 2 0f 57

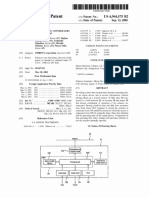

CONTROL GATE

POTENTIAL

FIG. 2

L/

CONTROL GATE

INTERLAYER

INSULATING FILM

SOURCE

POTENTIAL

S\ -

CG

JFG

DRAIN

POTENTIAL

FLOATING GATE

TUNNEL OXIDE FILM

SOURCE

DRAIN

MEMORY WELL

5

wELL POTENTIAL

SUB

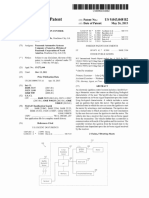

MODE

FIRST

COMMAND

SECOND

COMMAND

READ

OUR

NO NEED

RECOVERY

READ

OIH

NO NEED

ERAsE

20H

BOH

PROGRAM

IFH

40H

10

40

ADDITIONAL

PROGRAM

RETRY

PROGRAM

PARTIAL

ERASE

IAH

NO NEED

2FH

BOH

REwRITE

IIR

40H

JD

U.S. Patent

Jan. 7, 2003

Sheet 3 0f 57

US 6,504,764 B2

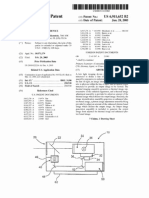

FIG. 4

TITLE

I/O7

Ready/m

DEFINITION

VOH ": Ready VOL ":Busy

I/O6 Reserved

[/05

Erase Check

VOH "= Fail VOL ": Pass

1/04

Program Check

VOH ": Fail VOL "= Pass

[/03 Reserved

1/02 Reserved

1/01 Reserved

I/OO Reserved

STATUS REGISTER

U.S. Patent

Jan. 7, 2003

Sheet 5 0f 57

US 6,504,764 B2

FIG. 6

B$ERAM 41/00

DLL

DLR

O1

00

1O

VH3 --------VWE2

----------------- i,

\\ 001!

VH2 ____________ _, vwvz >

VWE1

VH1 iiiiiiiiiiii v,

---------------- _

vwv1 > 0

VWDS >

H ,,

OV

MEMORY CELL

NUMBER

U.S. Patent

Jan. 7, 2003

-17v

Sheet 6 6f 57

US 6,504,764 B2

SELECT

WORD L

TOR

BATCH

35

i PH

----------PL ;,

0V

(1 WORD ERASE

AT SAME TIME)

i

W

SELECT

------------------- ~~

WRITE EVERY

BIT

NON-SELECTED

WORD LINE

0v

WORD

N~SELECTED

RD LINE

(I WORD WRITE

AT SAME TIME)

ECTED

LINE

6V

NONSELECTED

BIT LINE

OPERATION VOLTAGE

FIG. 9

WRITE

CaseI

Case2

(1)

(3)

(2)

(2)

CaseS

(3)

Case4

Cases

(2)

(3)

(2) I (I) I

(1) I

(31) (It) I I I I] (if) HG?)

ERASING STATE

U.S. Patent

Jan. 7, 2003

Sheet 8 0f 57

US 6,504,764 B2

11

AND TYPE

MEMORY MAT

,

SDI (BIT LINE

OONTROL GATE)

jIII

WL (wORO LINE)

M1

[MI

I].

_

SUB-BIT LINE

L/ML

a

JEEP

SUB-BIT LINE

//

i.

__T_ /

i.

II

[if

SSI (SOURCE LINE

CONTROL GATE)

[MC

g)

n f/MC

WL (WORO LINE)

SOURCE LINE

J:

WL (WORO LINE)

LL:

BIT LINE

BIT LINE

FIG. 12

NOR TYPE

MEMORY MAT

SOURCE LINE

MC

WORD LINE

WORD LINE

WORD LINE

WORD LINE

II

II

MCI BIT LINE

I

I

I : /'\ L / MC

I

I

I

BIT LINE

U.S. Patent

Jan. 7, 2003

Sheet 9 0f 57

US 6,504,764 B2

FIG. 13

DiNOR WPE

MEMORY MAT

>SOURCE LINE

W 0 DH D L W E

w

0 Dn RD LI E

m

WORD LINE

SELECTED GATE

SUB-BIT LINE

ERNIE:

BIT LINE

FIG. 14

NAND TYPE

MEMORY MAT

SOURCE LINE

SOURCE LINE

CONTROL GATE

I

I

fJ/W?"

WORD LINE

I: rL/MC

WORD LINE

II

II

II

WORD LINE

II

II

I

I

WORD LINE

WORD LINE

BIT LINE

CONTROL GATE

| rv/MC

":3

I

BIT LINE

BIT LINE

U.S. Patent

Jan. 7, 2003

HICR TYPE

MEMORY MAT

BIT LINE

Sheet 10 0f 57

SOURCE LINE

'

CONTROL GATE FIJI MC

IEF

sOuROE LINE

'

wORO LINE

l1 l

SUB-SOURCE

, I_I FY r/MC

LINE

\\-R_

WORD LINE

SUB-BIT

WORD LINE

BIT LINE

CONTROL GATE

US 6,504,764 B2

'

WEI MC

l

LIT)

IEF

l

1'1.

/

MC

_I_

:L

L

Big

i 5

IvIO 5 Ir

BIT LINE

ILL

K MC

MC 5 ,[

BIT LINE BIT LINE

II_L

'

aMO

BIT LINE

U.S. Patent

Jan. 7, 2003

T5

I01.

PROGRAMING

OPERATION

Sheet 11 0f 57

US 6,504,764 B2

2 (SEE FIG. 23)

'

' I

"II" WORD

DISTURB DETECTION

VWDS ?

T82

FAIL

T84

__________________________ ,_

'01"

PROGRAMING

OPERATION

T53

'0"

PROGRAMING

OPERATION

ERRATIC/

DISTURB

DETECTION

OPERATION

"00" ERRATIC

DETECTION

VWE2 ?

LATCH "IO" DATA

PROGRAM 10 DATA

PASS

SET PASS FLAG

SET FAIL FLAG

T0 STATIIS

T0 STATUS

A REGISTER

REGISTER

( END (OK) ) Q ENDING) )

PROGRAM FLOW (CASE 1)

S8

f

U.S. Patent

Jan. 7, 2003

Sheet 12 0f 57

FIG. 17

Vth

> "01"

vwvs ~~~~~~~~~~~~~~~~ -

>

BIT NUMBER

"01" PROGRAM DATA

FIG. 18

Vth

W > 00

0V

BIT NUMBER

"00" PROGRAM DATA

US 6,504,764 B2

U.S. Patent

Jan. 7, 2003

Sheet 13 0f 57

FIG. 19

A

Vth

> "01"

> "00"

W >*

"11..

0V

BIT NUMBER

"10" PROGRAM DATA

FIG. 20

VWE2

VWE1

VWDS ----------------- E

> "11"

BlT NUMBER

w

DETECTION OPERATION

US 6,504,764 B2

U.S. Patent

Jan. 7, 2003

Sheet 14 0f 57

US 6,504,764 B2

FIG. 21

CALCULATION CONTENT

(SENSE LATCH DATA OF

DATA LATCH PROCESS

SELECTED MAT SIDE)

"01 PROGRAM DATA

Mg

"00" PROGRAM DATA

A+B

"10" PROGRAM DATA

3+8

"00" ERRATIC DETECTION DATA

A+B

"10" ERRATIC DETECTION DATA

A . 5

"II" DISTuRR DETECTION DATA

A - B

A: UPPER DIGIT DATA

8 I LOWER DIGIT DATA

FIG. 22

uPIER LOEVER A+ A+B AIR E5 Ag A.B

DIGIT

DIGIT

U.S. Patent

Jan. 7, 2003

Sheet 15 0f 57

US 6,504,764 B2

FIG. 23

E

START "01" PROGRAMING

OPERATION

S1072

EXECUTE OATA LATCH

PROCESS

-=~

V

APPLY "01" PROGRAMING

BIAS VOLTAGE

5 312?

EXECUTE PROORAII/I

vERIEY vwva

S13

ALL

JUDGMENT

FAIL

PASS

END "01" PROORAMINO

OPERATION

FIG. 24 I ---------------------------------------------------- _,

E

START "10" ERRATIC

( DETECTION

I

5 520?

5

.

EXECUTE DATA LATCH

PROCESS

I

92 T2

EXECUTE ERRATIC

VERIFY vwEI

END "10 ERRATIC

DETECTION

U.S. Patent

Jan. 7, 2003

1/\_\w351E260%853m;2%

EFF0%, arm

0% HMTE

WE/kw

52iE.F6w% $5\/.9

0%03%,70%235

US 6,504,764 B2

w

FFFE8%

33m

2%FwF0

E:

Qm3585%FFEED/

wm>

Sheet 17 0f 57

F.;/

L Fl.

.Y...1. ...

gF01>12512%9;

3FIxE28D5 M5$36m.1o.65w/Cz-6m905gw

365m

2FFg

5w

mF@FFF$5

FF

8

FOFF

O

FF

F

OF

FOFSO

0

FF220

FF

8

F

FOFF

FF FQ:F

FFF2OOFFFFF

F202;

Q0

FOF

FF2

502;

O

i329

8FFFFFFFFFOF F 2Q

OFOFF

FFFF

FF

FOFFZ

F

OF

F5:2

F:

O

O2

FF

FF FFQSF FFF

MnaomTwu

F

j

m

W

w

23

<

E

g

a

F

m

5

I

9

E

3

0

FE<w2Zm5FQa38E

S

FF

FFFFF;

F220

FOF

F;

FF

3

FF

F5

OFOZQSF FFO

F.35%E@ZMFOw1S085WmEn%DF1O

You might also like

- Walter Russell - The Secret of LightDocument163 pagesWalter Russell - The Secret of Lighttombosliekamp98% (53)

- Narendra Nath Bhattacharyya History of The Tantric ReligionDocument484 pagesNarendra Nath Bhattacharyya History of The Tantric ReligionFrater Legbha100% (14)

- MLB Schematic OverviewDocument86 pagesMLB Schematic OverviewBarış Akdamar100% (4)

- Selected Writings of Mahamahopadhyaya Gopinath KavirajDocument205 pagesSelected Writings of Mahamahopadhyaya Gopinath Kavirajchetanpandey100% (5)

- (Database & ERP - OMG) Gaetjen, Scott - Knox, David Christopher - Maroulis, William - Oracle Database 12c security-McGraw-Hill Education (2015) PDFDocument549 pages(Database & ERP - OMG) Gaetjen, Scott - Knox, David Christopher - Maroulis, William - Oracle Database 12c security-McGraw-Hill Education (2015) PDFboualem.iniNo ratings yet

- BI StrategyDocument14 pagesBI Strategyfarah ImenNo ratings yet

- Us 6721207Document74 pagesUs 6721207Saurabh ChoudharyNo ratings yet

- United States Patent: Motohama Et A) - (10) Patent N0.: (45) Date of PatentDocument16 pagesUnited States Patent: Motohama Et A) - (10) Patent N0.: (45) Date of Patentdavid19775891No ratings yet

- US7156267Document7 pagesUS7156267Efabind OtNo ratings yet

- Us 6758544Document16 pagesUs 6758544norbertscribdNo ratings yet

- Ulllted States Patent (19) (11) Patent Number: 6,058,119: L B3 CalculationDocument19 pagesUlllted States Patent (19) (11) Patent Number: 6,058,119: L B3 CalculationRoshan KarnaNo ratings yet

- Unlted States Patent (10) Patent N0.2 US 7,464,259 B2Document16 pagesUnlted States Patent (10) Patent N0.2 US 7,464,259 B2حسام.علاوي جاسمNo ratings yet

- United States Patent: Condit Et A) - (10) Patent N0.: (45) Date of PatentDocument22 pagesUnited States Patent: Condit Et A) - (10) Patent N0.: (45) Date of Patentdavid19775891No ratings yet

- Aircraft Software Part Library ManagementDocument96 pagesAircraft Software Part Library Managementdavid19775891No ratings yet

- Ulllted States Patent (10) Patent N0.: US 8,516,483 B2Document19 pagesUlllted States Patent (10) Patent N0.: US 8,516,483 B2david19775891No ratings yet

- Ulllted States Patent (10) Patent N0.: US 8,555,288 B2Document82 pagesUlllted States Patent (10) Patent N0.: US 8,555,288 B2david19775891No ratings yet

- United States Patent: (10) Patent No.: US 6,957,339 B2Document43 pagesUnited States Patent: (10) Patent No.: US 6,957,339 B2Alex MungaiNo ratings yet

- Multi-Protocol Storage BridgeDocument31 pagesMulti-Protocol Storage BridgeManoj Kumar MauryaNo ratings yet

- Us6944575Document49 pagesUs6944575Anonymous KiraNo ratings yet

- Ulllted States Patent (10) Patent N0.: US 8,489,847 B2Document12 pagesUlllted States Patent (10) Patent N0.: US 8,489,847 B2david19775891No ratings yet

- Flat Panel Display Gate Driver CircuitDocument23 pagesFlat Panel Display Gate Driver CircuitGiancarloRichardRivadeneyraMirandaNo ratings yet

- ( ) Notice: Subject To Any Disclaimer, The Term of This E. "C Issn 0. EDocument23 pages( ) Notice: Subject To Any Disclaimer, The Term of This E. "C Issn 0. EEmmanuel Avalos HuarteNo ratings yet

- Aparatos y Metodos para Mantener La Circulación Constante Durante La Perforación.Document9 pagesAparatos y Metodos para Mantener La Circulación Constante Durante La Perforación.Raul BlancoNo ratings yet

- United States Patent: (12) (10) Patent No.: US 9,043,048 B2 Manotas, Jr. (45) Date of Patent: May 26, 2015Document9 pagesUnited States Patent: (12) (10) Patent No.: US 9,043,048 B2 Manotas, Jr. (45) Date of Patent: May 26, 2015StephenNo ratings yet

- Us 7642455Document6 pagesUs 7642455patelajayNo ratings yet

- US8851163B2 patent for multiple offset slim wellhead connectorDocument15 pagesUS8851163B2 patent for multiple offset slim wellhead connectorDiseno VATNo ratings yet

- Us7363398Document59 pagesUs7363398Anonymous KiraNo ratings yet

- United States Patent: (10) Patent No.: US 8,218,501 B2Document25 pagesUnited States Patent: (10) Patent No.: US 8,218,501 B2Know-7No ratings yet

- US9212603Separate-type Rotary EngineDocument12 pagesUS9212603Separate-type Rotary Engine임학진No ratings yet

- CTP in PhunDocument30 pagesCTP in Phunlong trịnhNo ratings yet

- United States Patent: Kotsopoulos Et Al. (45) Date of Patent: Apr. 18, 2006Document10 pagesUnited States Patent: Kotsopoulos Et Al. (45) Date of Patent: Apr. 18, 2006Taufiq AhmadNo ratings yet

- Us 8991762Document10 pagesUs 8991762Nathália RozaNo ratings yet

- United States Patent: AugustoDocument18 pagesUnited States Patent: AugustocherniNo ratings yet

- US8986395Document13 pagesUS8986395Stefania PredaNo ratings yet

- United States Patent: (12) (10) Patent No.: US 7.464,653 B2Document20 pagesUnited States Patent: (12) (10) Patent No.: US 7.464,653 B2marcoNo ratings yet

- Us 7664476Document19 pagesUs 7664476pepixx985No ratings yet

- Us7997527 PDFDocument11 pagesUs7997527 PDF雷黎明No ratings yet

- United States Patent (10) Patent No.: US 7,558,698 B2: Funge Et Al. (45) Date of Patent: Jul. 7, 2009Document22 pagesUnited States Patent (10) Patent No.: US 7,558,698 B2: Funge Et Al. (45) Date of Patent: Jul. 7, 2009Nose NoloseNo ratings yet

- Us 8510756Document22 pagesUs 8510756david19775891No ratings yet

- US7963479Document10 pagesUS7963479雷黎明No ratings yet

- United States Patent: Cheng Et Al. (10) Patent No.: US 9,078,547 B2Document10 pagesUnited States Patent: Cheng Et Al. (10) Patent No.: US 9,078,547 B2Alex BrcNo ratings yet

- 59 0f1-,-,,é - 1,, M 13,553 $525113ei Iiii?if III Fifit 21811101511121.1118Document22 pages59 0f1-,-,,é - 1,, M 13,553 $525113ei Iiii?if III Fifit 21811101511121.1118Qwerty UiopNo ratings yet

- United States Patent: Tawara Et Al. (45) Date of Patent: Aug. 7, 2007Document25 pagesUnited States Patent: Tawara Et Al. (45) Date of Patent: Aug. 7, 2007SintaDwiSampurnaNo ratings yet

- United States Patent (10) Patent No.: US 9,115,565 B1Document20 pagesUnited States Patent (10) Patent No.: US 9,115,565 B1VladislavNo ratings yet

- Us8063750Document8 pagesUs8063750Anonymous KiraNo ratings yet

- Us 8468154Document22 pagesUs 8468154Sami LeinoNo ratings yet

- United States Patent: Matsushita Et AlDocument25 pagesUnited States Patent: Matsushita Et AlEl Kanouani ZakariaNo ratings yet

- United States Patent: Bourdon Et A) - (10) Patent N0.: (45) Date of PatentDocument14 pagesUnited States Patent: Bourdon Et A) - (10) Patent N0.: (45) Date of Patentdavid19775891No ratings yet

- Oleumtech Us6967589Document21 pagesOleumtech Us6967589shadyghanemNo ratings yet

- United States Patent: (10) Patent No.: US 9,131,338 B2Document18 pagesUnited States Patent: (10) Patent No.: US 9,131,338 B2Teju AshuNo ratings yet

- United States Patent (10) Patent No.: US 8,014,526 B2Document12 pagesUnited States Patent (10) Patent No.: US 8,014,526 B2sat258No ratings yet

- United States Patent (10) Patent No.: US 7,134,558 B1: Mimlitch, III Et Al. (45) Date of Patent: Nov. 14, 2006Document22 pagesUnited States Patent (10) Patent No.: US 7,134,558 B1: Mimlitch, III Et Al. (45) Date of Patent: Nov. 14, 2006Erin GokNo ratings yet

- Vacuum Insulated Beverage DispenserDocument13 pagesVacuum Insulated Beverage DispenserGabriel RochaNo ratings yet

- United States Patent (10) Patent No.: US 8,024,070 B2Document7 pagesUnited States Patent (10) Patent No.: US 8,024,070 B2CY LiuNo ratings yet

- United States Patent (10) Patent No.: US 6,712,734 B1: Loeffler (45) Date of Patent: Mar. 30, 2004Document7 pagesUnited States Patent (10) Patent No.: US 6,712,734 B1: Loeffler (45) Date of Patent: Mar. 30, 2004pmurphNo ratings yet

- FUSE BYTE SETTINGS FOR ATMEL MCUDocument4 pagesFUSE BYTE SETTINGS FOR ATMEL MCUFabrício AngieneNo ratings yet

- Quick Connector With A Sensor HousingDocument11 pagesQuick Connector With A Sensor HousingTUNCAY GUMUSNo ratings yet

- United States Patent: Choi (45) Date of Patent: Aug. 21, 2007Document10 pagesUnited States Patent: Choi (45) Date of Patent: Aug. 21, 2007Stéwàrt ChïkômôlâNo ratings yet

- Umted States Patent (10) Patent N6. US 8,522,253 B1: Rozas Et A1. (45) Date of Patent: Aug. 27, 2013Document14 pagesUmted States Patent (10) Patent N6. US 8,522,253 B1: Rozas Et A1. (45) Date of Patent: Aug. 27, 2013david19775891No ratings yet

- United States Patent: Shah-HosseiniDocument28 pagesUnited States Patent: Shah-Hosseinidavid19775891No ratings yet

- United States Patent: Wang Et Al. Patent No.: Date of Patent: US 8,671,381 B1 Mar.11, 2014Document26 pagesUnited States Patent: Wang Et Al. Patent No.: Date of Patent: US 8,671,381 B1 Mar.11, 2014David PetersNo ratings yet

- US5715376Document137 pagesUS5715376ztakahashiNo ratings yet

- US9360082Document11 pagesUS9360082kippcamNo ratings yet

- How to Find Out About Patents: The Commonwealth and International Library: Libraries and Technical Information DivisionFrom EverandHow to Find Out About Patents: The Commonwealth and International Library: Libraries and Technical Information DivisionNo ratings yet

- Great Systems of Yoga: Ernest WoodDocument86 pagesGreat Systems of Yoga: Ernest WoodparagNo ratings yet

- Gita Press Invoice - 22165Document1 pageGita Press Invoice - 22165Saurabh ChoudharyNo ratings yet

- Gita Press Invoice - 22165Document1 pageGita Press Invoice - 22165Saurabh ChoudharyNo ratings yet

- Petition 2Document84 pagesPetition 2Saurabh ChoudharyNo ratings yet

- Payment ReceiptDocument1 pagePayment Receiptraj biradarNo ratings yet

- Walter Russell - A New Concept of The UniverseDocument98 pagesWalter Russell - A New Concept of The Universefredtyler9100% (1)

- R Nagaswamy - Art and Religion of The Bhairavas - Illumined by Two Rare Sanskrit Texts Sarva-siddhānta-Vivēka and Jñāna-siddhi-Tamil Arts AcademyDocument355 pagesR Nagaswamy - Art and Religion of The Bhairavas - Illumined by Two Rare Sanskrit Texts Sarva-siddhānta-Vivēka and Jñāna-siddhi-Tamil Arts AcademySaurabh ChoudharyNo ratings yet

- Terms and ConditionsDocument1 pageTerms and ConditionsSaurabh ChoudharyNo ratings yet

- Us 8346894Document26 pagesUs 8346894Saurabh ChoudharyNo ratings yet

- Mr. Gousal Azam: 7978466567 Mr. Varender Beri: 7065044985Document1 pageMr. Gousal Azam: 7978466567 Mr. Varender Beri: 7065044985Saurabh ChoudharyNo ratings yet

- Payment ReceiptDocument1 pagePayment Receiptraj biradarNo ratings yet

- Saiva Siddantha ConferenceenglishDocument3 pagesSaiva Siddantha ConferenceenglishSaurabh ChoudharyNo ratings yet

- JD - GPL - Strategic InitiativesDocument4 pagesJD - GPL - Strategic InitiativesSaurabh ChoudharyNo ratings yet

- Us 6931128Document15 pagesUs 6931128Saurabh ChoudharyNo ratings yet

- Us 7808483Document16 pagesUs 7808483Saurabh ChoudharyNo ratings yet

- Us 6947748Document19 pagesUs 6947748Saurabh ChoudharyNo ratings yet

- United States Patent: (12) (10) Patent N0.: US 6,911,652 B2Document6 pagesUnited States Patent: (12) (10) Patent N0.: US 6,911,652 B2Saurabh ChoudharyNo ratings yet

- Cost ManagementDocument7 pagesCost ManagementSaurabh ChoudharyNo ratings yet

- Us 7505406Document12 pagesUs 7505406Saurabh ChoudharyNo ratings yet

- Us 6744692Document22 pagesUs 6744692Saurabh ChoudharyNo ratings yet

- Smart CityDocument3 pagesSmart CitySaurabh ChoudharyNo ratings yet

- 2013-GEIPER Holiday CalenderDocument3 pages2013-GEIPER Holiday CalenderSaurabh ChoudharyNo ratings yet

- Nestle HeroesDocument5 pagesNestle HeroesSaurabh ChoudharyNo ratings yet

- S4f08.23.en-Us 18Document1 pageS4f08.23.en-Us 18Samir SahooNo ratings yet

- EY Risk Innovation Techathon-Use Case1Document9 pagesEY Risk Innovation Techathon-Use Case1Abhijit PolNo ratings yet

- Pi Odbc ManualDocument117 pagesPi Odbc ManualJordi Cebrián100% (1)

- SQL Is Used Often To Query, Insert, Update, and Modify Data. at A Basic Level SQL Is A Method For Communicating Between You and The DatabaseDocument8 pagesSQL Is Used Often To Query, Insert, Update, and Modify Data. at A Basic Level SQL Is A Method For Communicating Between You and The DatabaseMohd AzazNo ratings yet

- Class XII (As Per CBSE Board) : Computer ScienceDocument38 pagesClass XII (As Per CBSE Board) : Computer ScienceDrAshish VashisthaNo ratings yet

- OODP-Unit 5Document128 pagesOODP-Unit 5Akshat Dutt KaushikNo ratings yet

- Linux - Foundation.2passeasy - Cka.dumps.2022 May 14.by - Boyd.40q.vceDocument9 pagesLinux - Foundation.2passeasy - Cka.dumps.2022 May 14.by - Boyd.40q.vceMaximNo ratings yet

- What Is An Index Organized Table (IOT) ?Document5 pagesWhat Is An Index Organized Table (IOT) ?ramkashyapNo ratings yet

- Refresh Test Database From Production in Lesser TimeDocument6 pagesRefresh Test Database From Production in Lesser TimeAbdul QadirNo ratings yet

- Prune Days and Change Capture in Data Warehouse Application Console (DAC)Document3 pagesPrune Days and Change Capture in Data Warehouse Application Console (DAC)nelrick1984100% (2)

- Web Mining Techniques and ApplicationsDocument13 pagesWeb Mining Techniques and ApplicationsSunil Kr Pandey100% (2)

- Notes On Database Management SystemDocument24 pagesNotes On Database Management SystemAditya BafnaNo ratings yet

- Relational Databases and SQL FundamentalsDocument18 pagesRelational Databases and SQL FundamentalsMary JamesNo ratings yet

- Linux MCQSDocument9 pagesLinux MCQSBashir Ahmed Zubir AliNo ratings yet

- LogDocument5 pagesLogGabrielle Grace RiveraNo ratings yet

- Galaxymanagement PDFDocument8 pagesGalaxymanagement PDFdileepNo ratings yet

- ETLDocument3 pagesETLAbiNo ratings yet

- VPLEX VS6 Shutdown Procedure For Cluster 1 in A Metro ConfigurationDocument33 pagesVPLEX VS6 Shutdown Procedure For Cluster 1 in A Metro ConfigurationJorgeNo ratings yet

- McseDocument2 pagesMcseRanjith KumarNo ratings yet

- Delimited Report Output Using Report BuilderDocument20 pagesDelimited Report Output Using Report BuilderPritesh Mogane0% (1)

- Assignment - 1.3: QuestionsDocument3 pagesAssignment - 1.3: QuestionsSrinivasaRao JJNo ratings yet

- Nosql Data Architecture PatternsDocument62 pagesNosql Data Architecture PatternsManisha_tNo ratings yet

- QA Chapter1Document2 pagesQA Chapter1Anthony CarmeloNo ratings yet

- DOP-C02demo Exam Practice QuestionsDocument7 pagesDOP-C02demo Exam Practice Questionslovegeorge393No ratings yet

- SQL Queries Hands On MySQLDocument3 pagesSQL Queries Hands On MySQLMohammed IbrahimNo ratings yet

- Naukri SivaPrasadK (4y 0m)Document5 pagesNaukri SivaPrasadK (4y 0m)Pavithra k rNo ratings yet

- Normalization 1st To 5th NF With ExampleDocument33 pagesNormalization 1st To 5th NF With Examplesjkushwaha21No ratings yet

- Mongodb QRC QueriesDocument2 pagesMongodb QRC QuerieskinoshitNo ratings yet