Professional Documents

Culture Documents

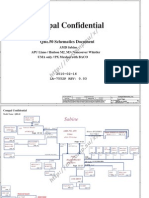

JE50-HR M/B Schematics

Uploaded by

ismaeltorresrojasOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

JE50-HR M/B Schematics

Uploaded by

ismaeltorresrojasCopyright:

Available Formats

A

Compal Confidential

1

Model Name : JE50-HR/SJV50-HR

Compal Project Name : P5WE0/P5WS0

File Name : LA-6902P

Compal Confidential

2

JE50-HR/SJV50-HR(P5WE0/P5WS0) M/B Schematics Document

Intel Sandy Bridge Processor with DDRIII + Cougar Point PCH

Nvidia N12P GS/GV

2010-10-19

REV:0.1

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2010/10/15

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Cover Page

Size Document Number

Custom

Rev

JE50-HR/SJV50-HR M/B Schematics0.4

Date:

Sheet

Wednesday, October 27, 2010

E

of

61

Fan Control

page 42

PEG(DIS)

PCI-E 2.0x16 5GT/s PER LANE

100MHz

Nvidia

N12P GS/GV

Memory BUS(DDRIII)

204pin DDRIII-SO-DIMM X2

Dual Channel

Intel

Sandy Bridge

133MHz

page 11,12

BANK 0, 1, 2, 3

1.5V DDRIII 1066/1333

Processor

page22~30

rPGA989

page 4~10

HDMI(DIS)

CRT(DIS)

HDMI Conn.

page 33

LVDS(DIS)

FDI x8

LVDS Conn.

CRT Conn.

page 31

page 32

DMI x4

100MHz

100MHz

2.7GT/s

1GB/s x4

LVDS(UMA/OPTIMUS)

CRT(UMA/OPTIMUS)

TMDS(UMA/OPTIMUS)

Intel

Cougar Point-M

USB 2.0 conn x2

Bluetooth

Conn

CMOS Camera

USB port 0,1 on

USB/B

page 38

USB port 13

USB port 10

page 38

USBx14

3.3V 48MHz

HD Audio

3.3V 24MHz

3G connector

USB port 9,12 on 3G/B

page 31

page 37

2

PCH

HDA Codec

100MHz

PCI-Express x 8 (ARD PCIE2.0 2.5GT/s)

SATA x 6 (GEN1 1.5GT/S ,GEN2 3GT/S) 100MHz

port 2,3

port 5

USB 3.0 conn x1

NEC uPD720200AF1

with USB3.0 Conn.

page 45

port 1

WLAN, WWAN

USB port 12,13

page 37

BCM57785

SPI ROM x1

page 35,36

Card Reader

Conn. page 35,36

SATA HDD

Conn. page

RJ45

page 36

34

SATA CDROM

Conn. page 34

page 40

LPC BUS

page 43,44

page 39

USB 2.0/B 2Port

USB Port0,1 page 38

LF-6901P

Touch Pad

FPC for USB3.0

Int.KBD

page 40

page 40

page 38

USB 3.0 /B

1 port as USB3.0

1 port as USB2.0

page 38

DC/DC Interface CKT.

page 41

ENE KB930

LS-6904P

Power On/Off CKT.

page 41

Phone Jack x 2

33MHz

Sub-board

LS-6901P

page 13

Int. Speaker

page 13

port 2

port 0,1

RTC CKT.

page 41

SPI

page 13~21

LAN(GbE) &

Card Reader

MINI Card x2

ALC271X/277X

989pin BGA

BIOS ROM

page 40

LS-6903P

4

3G/B

page 37

Power Circuit DC/DC

page 46~59

LS-6902P + LS-6905P

Issued Date

2010/10/15

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

page 40

A

Compal Electronics, Inc.

Compal Secret Data

Security Classification

PWR/B

Title

Block Diagrams

Size Document Number

Custom

Rev

JE50-HR/SJV50-HR M/B Schematics 0.4

Date:

Sheet

Wednesday, October 27, 2010

E

of

61

Voltage Rails

Power Plane

Description

S1

S3

S5

VIN

Adapter power supply (19V)

N/A

N/A

N/A

BATT+

Battery power supply (12.6V)

N/A

N/A

N/A

+VALW

+V

+VS

Clock

HIGH

HIGH

HIGH

ON

ON

ON

ON

S1(Power On Suspend)

LOW

HIGH

HIGH

HIGH

ON

ON

ON

LOW

S3 (Suspend to RAM)

LOW

LOW

HIGH

HIGH

ON

ON

OFF

OFF

S4 (Suspend to Disk)

LOW

LOW

LOW

HIGH

ON

OFF

OFF

OFF

S5 (Soft OFF)

LOW

LOW

LOW

LOW

ON

OFF

OFF

OFF

B+

AC or battery power rail for power circuit.

N/A

N/A

N/A

Core voltage for CPU

ON

OFF

OFF

+VGA_CORE

Core voltage for GPU

ON

OFF

OFF

+VGFX_CORE

Core voltage for UMA graphic

ON

OFF

OFF

+0.75VS

+0.75VP to +0.75VS switched power rail for DDR terminator

ON

OFF

OFF

+1.05VSDGPU

+1.0VSPDGPU to +1.0VSDGPU switched power rail for GPU

ON

OFF

OFF

+1.05VS_VTT

+1.05VS_VCCPP to +1.05VS_VCCP switched power rail for CPU

ON

OFF

OFF

+1.05VS_PCH

+1.05VS_VCCP to +1.05VS_PCH power for PCH

ON

OFF

OFF

+1.5V

+1.5VP to +1.5V power rail for DDRIII

ON

ON

OFF

+1.5VS

+1.5V to +1.5VS switched power rail

ON

OFF

OFF

Vcc

Ra/Rc/Re

+1.5VSDGPU

+1.5VS to +1.5VSDGPU switched power rail for GPU

ON

OFF

OFF

Board ID

(+5VALW or +3VALW) to 1.8V switched power rail to PCH & GPU

ON

OFF

OFF

+1.8VSDGPU

+1.8VS to +1.8VSDGPU switched power rail for GPU

ON

OFF

OFF

+3VALW

+3VALW always on power rail

ON

ON

ON*

+3VALW_EC

+3VALW always to KBC

ON

ON

ON*

+3V_LAN

+3VALW to +3V_LAN power rail for LAN

ON

ON

ON*

0

1

2

3

4

5

6

7

+3VALW to +3VALW_PCH power rail for PCH (Short Jumper)

ON

ON

ON*

+3VALW to +3VS power rail

ON

OFF

OFF

+5VALW

+5VALWP to +5VALW power rail

ON

ON

ON*

+5VALW_PCH

+5VALW to +5VALW_PCH power rail for PCH (Short resister)

ON

ON

ON*

+5VS

+5VALW to +5VS switched power rail

ON

OFF

OFF

+VSB

+VSBP to +VSB always on power rail for sequence control

ON

ON

ON*

+RTCVCC

RTC power

ON

ON

ON

Device

Address

Smart Battery

0001 011X b

Board ID

0

1

2

3

4

5

6

7

EC SM Bus2 address

Device

3.3V +/- 5%

100K +/- 5%

Rb / Rd / Rf

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC

V AD_BID min

0 V

0.216 V

0.436 V

0.712 V

1.036 V

1.453 V

1.935 V

2.500 V

V AD_BID typ

0 V

0.250 V

0.503 V

0.819 V

1.185 V

1.650 V

2.200 V

3.300 V

BOARD ID Table

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

EC SM Bus1 address

Address

Device

Address

Clock Generator (9LVS3199AKLFT,

RTM890N-631-VB-GRT)

1101 0010b

DDR DIMM0

1001 000Xb

PCB Revision

0.1

0.2

0.3

0.4

1.0

DDR DIMM2

1001 010Xb

USB Port Table

USB 2.0 USB 1.1 Port

UHCI0

3G & BT & USB30 & USB20 Config

USB30 SKU: USB30@

OPTMIUS SKU: OPT@

3G SKU: 3G@

BT SKU: BT@

USB20 SKU: USB20@

Non-OPTMIUS SKU: NOPT@

LAN Chip A0 version: A0@ N12P-GS: GS@

LAN chip B0 Version: B0@ N12P-GV: GV@

BOM Config

BT@/3G@/USB30@/UMA@/UMAO@/NOPT@/A0@

UMA Only:

OPTIMUS(N12P-GS): BT@/3G@/USB30@/UMA@/DIS@/X76@/OPT@/A0@/GS@

DIS Only(N12P-GS): BT@/3G@/USB30@/DISO@/DIS@/X76@/NOPT@/A0@/GS@

OPTIMUS(N12P-GV): BT@/3G@/USB30@/UMA@/DIS@/X76@/OPT@/A0@/GV@

DIS Only(N12P-GV): BT@/3G@/USB30@/DISO@/DIS@/X76@/NOPT@/A0@/GV@

UHCI2

UHCI3

UHCI4

EHCI2

UHCI5

UHCI6

VRAM P/N :

64*16

Samsung : SA000035700

Hynix : SA000032400/SA0000324C0

128*16

Samsung : SA00003MQ40

Hynix : SA00003VS00

UHCI1

EHCI1

0

1

2

3

4

5

6

7

8

9

10

11

12

13

3 External

USB Port

USB/B (Right Side)

USB/B (Right Side)

USB3.0 colay USB2.0 Conn.

USB/B Colay USB3.0

BTO Item

UMA Only

UMA with OPTIMUS

Dis with OPTIMUS

DIS Only

OPTIMUS

Non-OPTIMUS

3G

Blue Tooth

USB2.0

USB3.0

VRAM

Connector

Unpop

LAN Chip A0 version

LAN Chip B0 version

N12P-GS

N12P-GV

2010/10/15

BOM Structure

UMAO@

UMA@

DIS@

DISO@

OPT@

NOPT@

3G@

BT@

USB20@

USB30@

X76@

CONN@

@

A0@

B0@

GS@

GV@

Compal Electronics, Inc.

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

EVT

EVT2

DVT

PVT

Pre-MP

Mini Card 1(WLAN)

3G/B(WWAN)

Camera

Mini Card 2(Reserved)

3G/B(SIM Card)

BlueTooth

Compal Secret Data

Security Classification

Issued Date

V AD_BID max

0 V

0.289 V

0.538 V

0.875 V

1.264 V

1.759 V

2.341 V

3.300 V

BTO Option Table

PCH SM Bus address

3

Board ID / SKU ID Table for AD channel

+1.8VS

+3VALW_PCH

SLP_S1# SLP_S3# SLP_S4# SLP_S5#

HIGH

Full ON

+CPU_CORE

+3VS

SIGNAL

STATE

Title

Notes List

Size Document Number

Custom

Rev

JE50-HR/SJV50-HR M/B Schematics 0.4

Date:

Sheet

Wednesday, October 27, 2010

E

of

61

+1.05VS_VTT

ZZZ

DA60000KC00

JCPU1A

D

15

15

15

15

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

B28

B26

A24

B23

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

15

15

15

15

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

G21

E22

F21

D21

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

15

15

15

15

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

G22

D22

F20

C21

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

15

15

15

15

15

15

15

15

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

A21

H19

E19

F18

B21

C20

D18

E17

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

15

15

15

15

15

15

15

15

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

A22

G19

E20

G18

B20

C19

D19

F17

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

15 FDI_FSYNC0

15 FDI_FSYNC1

15 FDI_INT

R145

24.9_0402_1%

15 FDI_LSYNC0

15 FDI_LSYNC1

J18

J17

FDI0_FSYNC

FDI1_FSYNC

H20

FDI_INT

J19

H17

FDI0_LSYNC

FDI1_LSYNC

A18

A17

B16

eDP_COMPIO

eDP_ICOMPO

eDP_HPD

C15

D15

eDP_AUX

eDP_AUX#

C17

F16

C16

G15

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

C18

E16

D16

F15

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

DMI

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

EDP_COMP

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

eDP

eDP_COMPIO and ICOMPO signals should

be shorted near balls,

Trace Width for EDP_COMPIO=4mils,

EDP_ICOMPO=12mils,

and both length less than 500 mils...

should not be left floating

,even if disable eDP function...

B27

B25

A25

B24

PCI EXPRESS* - GRAPHICS

+1.05VS_VTT

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

Intel(R) FDI

15

15

15

15

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

Sandy Bridge_rPGA_Rev0p61

CONN@

J22

J21

H22

R517

24.9_0402_1%

PEG_COMP

PEG_GTX_C_HRX_N15

K33

PEG_GTX_C_HRX_N14

M35

PEG_GTX_C_HRX_N13

L34

PEG_GTX_C_HRX_N12

J35

PEG_GTX_C_HRX_N11

J32

PEG_GTX_C_HRX_N10

H34

PEG_GTX_C_HRX_N9

H31

PEG_GTX_C_HRX_N8

G33

PEG_GTX_C_HRX_N7

G30

PEG_GTX_C_HRX_N6

F35

PEG_GTX_C_HRX_N5

E34

PEG_GTX_C_HRX_N4

E32

PEG_GTX_C_HRX_N3

D33

PEG_GTX_C_HRX_N2

D31

PEG_GTX_C_HRX_N1

B33

PEG_GTX_C_HRX_N0

C32

PEG_GTX_C_HRX_P15

J33

PEG_GTX_C_HRX_P14

L35

PEG_GTX_C_HRX_P13

K34

PEG_GTX_C_HRX_P12

H35

PEG_GTX_C_HRX_P11

H32

PEG_GTX_C_HRX_P10

G34

PEG_GTX_C_HRX_P9

G31

PEG_GTX_C_HRX_P8

PEG_GTX_C_HRX_P7

F33

PEG_GTX_C_HRX_P6

F30

PEG_GTX_C_HRX_P5

E35

PEG_GTX_C_HRX_P4

E33

PEG_GTX_C_HRX_P3

F32

PEG_GTX_C_HRX_P2

D34

PEG_GTX_C_HRX_P1

E31

PEG_GTX_C_HRX_P0

C33

B32

PEG_HTX_GRX_N15

PEG_HTX_GRX_N14

M29

PEG_HTX_GRX_N13

M32

PEG_HTX_GRX_N12

M31

PEG_HTX_GRX_N11

L32

PEG_HTX_GRX_N10

L29

PEG_HTX_GRX_N9

K31

PEG_HTX_GRX_N8

K28

PEG_HTX_GRX_N7

J30

PEG_HTX_GRX_N6

J28

PEG_HTX_GRX_N5

H29

PEG_HTX_GRX_N4

G27

PEG_HTX_GRX_N3

E29

PEG_HTX_GRX_N2

F27

PEG_HTX_GRX_N1

D28

PEG_HTX_GRX_N0

F26

E25

PEG_HTX_GRX_P15

PEG_HTX_GRX_P14

M28

PEG_HTX_GRX_P13

M33

PEG_HTX_GRX_P12

M30

PEG_HTX_GRX_P11

L31

PEG_HTX_GRX_P10

L28

PEG_HTX_GRX_P9

K30

PEG_HTX_GRX_P8

K27

PEG_HTX_GRX_P7

J29

PEG_HTX_GRX_P6

J27

PEG_HTX_GRX_P5

H28

PEG_HTX_GRX_P4

G28

PEG_HTX_GRX_P3

E28

PEG_HTX_GRX_P2

F28

PEG_HTX_GRX_P1

D27

PEG_HTX_GRX_P0

E26

D25

C46 1

C49 1

C51 1

C53 1

C60 1

C71 1

C75 1

C82 1

C92 1

C93 1

C102 1

C111 1

C113 1

C125 1

C129 1

C144 1

PEG_ICOMPI and PEG_RCOMPO signals should be

shorted and routed,

max length = 500 mils,trace width=4mils

PEG_ICOMPO signals should be routed with - max

length = 500 mils,trace width=12mils

spacing =15mils

PEG_GTX_HRX_N15

2 DIS@ 0.22U_0402_10V6K

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N14

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N13

PEG_GTX_HRX_N12

2 DIS@ 0.22U_0402_10V6K

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N11

PEG_GTX_HRX_N10

2 DIS@ 0.22U_0402_10V6K

PEG_GTX_HRX_N9

2 DIS@ 0.22U_0402_10V6K

PEG_GTX_HRX_N8

2 DIS@ 0.22U_0402_10V6K

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N7

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N6

PEG_GTX_HRX_N5

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N4

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N3

DIS@

0.22U_0402_10V6K

2

PEG_GTX_HRX_N2

2 DIS@ 0.22U_0402_10V6K

PEG_GTX_HRX_N1

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_N0

2 DIS@ 0.22U_0402_10V6K

PEG_GTX_HRX_N[0..15] 22

PEG_GTX_HRX_P[0..15] 22

PEG_HTX_C_GRX_N[0..15] 22

PEG_HTX_C_GRX_P[0..15] 22

PEG_GTX_HRX_P15

PEG_GTX_HRX_P14

PEG_GTX_HRX_P13

PEG_GTX_HRX_P12

PEG_GTX_HRX_P11

PEG_GTX_HRX_P10

C68 1

PEG_GTX_HRX_P9

2 DIS@ 0.22U_0402_10V6K

C81 1

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_P8

C86 1

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_P7

C89 1

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_P6

C100 1

2 DIS@ 0.22U_0402_10V6K

PEG_GTX_HRX_P5

C105 1

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_P4

C106 1

2 DIS@ 0.22U_0402_10V6K

PEG_GTX_HRX_P3

C117 1

DIS@

0.22U_0402_10V6K

2

PEG_GTX_HRX_P2

C119 1

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_P1

C135 1

2 DIS@ 0.22U_0402_10V6K PEG_GTX_HRX_P0

C138 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_N15

C516 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_N14

C520 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_N13

C529 1

2 DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_N12

PEG_HTX_C_GRX_N11

C534 1

DIS@ 0.22U_0402_10V6K

C538

1

2 2DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_N10

PEG_HTX_C_GRX_N9

C540 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_N8

C542

2 DIS@ 0.22U_0402_10V6K

C544 1 1

2 DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_N7

C546 1

2 DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_N6

C548 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_N5

C550

2 DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_N4

C552 1 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_N3

C554

2 DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_N2

C556 1 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_N1

C558 1

DIS@

0.22U_0402_10V6K

2

PEG_HTX_C_GRX_N0

C560 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_P15

C515 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_P14

C528 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_P13

C533 1

2 DIS@ 0.22U_0402_10V6K

PEG_HTX_C_GRX_P12

C536 1

2 DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_P11

C539 1

PEG_HTX_C_GRX_P10

2 DIS@ 0.22U_0402_10V6K

C541 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_P9

C543 1

2 DIS@ 0.22U_0402_10V6KPEG_HTX_C_GRX_P8

C545 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_P7

C547 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_P6

PEG_HTX_C_GRX_P5

C549

0.22U_0402_10V6K

C551

0.22U_0402_10V6K

1 1 2 DIS@

2 DIS@

PEG_HTX_C_GRX_P4

C553 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_P3

C555 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_P2

C557 1

2 DIS@ 0.22U_0402_10V6K PEG_HTX_C_GRX_P1

PEG_HTX_C_GRX_P0

C559

DIS@ 0.22U_0402_10V6K

1

C561 1

2 2DIS@ 0.22U_0402_10V6K

C47

C50

C52

C56

C66

1

1

1

1

1

2 DIS@ 0.22U_0402_10V6K

2 DIS@ 0.22U_0402_10V6K

2 DIS@ 0.22U_0402_10V6K

2 DIS@ 0.22U_0402_10V6K

2 DIS@ 0.22U_0402_10V6K

Typ- suggest 220nF. The change in AC capacitor

value from 100nF to 220nF is to enable

compatibility with future platforms having PCIE

Gen3 (8GT/s)

Compal Secret Data

Security Classification

2010/10/15

Issued Date

Deciphered Date

2011/10/15

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

Title

PROCESSOR(1/7) DMI,FDI,PEG

Size

Document Number

Custom

JE50-HR/SJV50-HR M/B Schematics

Date:

W ednesday, October 27, 2010

Sheet

1

of

61

Rev

0.4

Buffered reset to CPU

+3VS

+3VALW

R87

43_0402_1%

1

2 BUF_CPU_RST#

okCPUreset

O

A

4 PM_SYS_PWRGD_BUF

1

R204

2

130_0402_5%

PM_DRAM_PWRGD_R

R203

39_0402_1%

40,50 H_PROCHOT#

18 H_THRMTRIP#

H_PECI_ISO

R92

56_0402_5% H_PROCHOT#_R

1

2

CLOCKS

A16

A15

PECI

AL32

PROCHOT#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

R8

AK1

A5

A4

PRDY#

PREQ#

H_CPUPWRGD_R

OK

AM34

AP33

PM_SYNC

UNCOREPWRGOOD

UNCOREPWRGOOD: CORE

PM_DRAM_PWRGD_R

V8

SM_DRAMPWROK

SM_DRAMPWROK:DRAM power ok

BUF_CPU_RST#

AR33

RESET#

JTAG & BPM

18 H_CPUPWRGD

R81

0_0402_5%

1

2

H_PM_SYNC_R

PWR MANAGEMENT

1 10K_0402_5%

R96

0_0402_5%

1

2

1 1K_0402_5%

1 1K_0402_5%

+1.05VS_VTT

If use External Graphic or

use integrated without eDP

DPLL_REF_SSCLK PD 1K_5% to GND

DPLL_REF_SSCLK# PH 1K_5% to +1.05VS_VTT

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST# 6

R231

1 140_0402_1%

1 25.5_0402_1%

1 200_0402_1%

2

R566 2

R571 2

DDR3 Compensation Signals

THERMTRIP#

TCK

TMS

TRST#

TDI

TDO

R03 modify

AP29

AP27

15 H_PM_SYNC

R516 2

R518 2

CLK_CPU_DMI 14

CLK_CPU_DMI# 14

CATERR#

AN33

R97

0_0402_5% H_THEMTRIP#_R

AN32

1

2

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

A28

A27

AR26

AR27

AP30

AR28

AP26

DBR#

AL35

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

TCK

TMS

TRST#

TDI

TDO

DBRESET#_R

PAD

PAD

PAD

T66

T67

T68

PAD

PAD

T69

T70

@

@

@

+3VS

H_PECI

1 62_0402_5%

H_PROCHOT#

SKTOCC#

BCLK

BCLK#

CLK_CPU_DMI

CLK_CPU_DMI#

@

@

R101

0_0402_5%

1

2

R40

1K_0402_5%

18,40

2 R91

@

R93

0_0402_5%

1

2

AL33

SNB_IVB#

DDR3

MISC

Processor Pullups

H_CATERR#

PAD

MISC

AN34

T6

JCPU1B

C26

17 H_SNB_IVB#

R84 2

SNB_IVB# had changed the name to

PROC_SELCT#,function for future platform,

connect to the DF_TVS strap on the PCH

+1.05VS_VTT

RESET#:

15 SYS_PWROK

15 PM_DRAM_PWRGD

R88

0_0402_5%

@

SN74LVC1G07DCKR_SC70-5

200_0402_1%

U11

74AHC1G09GW_TSSOP5

4 BUFO_CPU_RST#

R205

U7

R90

75_0402_1%

1

1

C307

0.1U_0402_16V4Z

THERMAL

+1.5V_CPU_VDDQ

PLT_RST#

Y

G

PLT_RST#

NC

+1.05VS_VTT

C162

0.1U_0402_16V4Z

17

@

R782 2 1

1

0_0402_5%

R64 2 2

1

0_0402_5%

XDP_DBRESET#

XDP_DBRESET# 15

Sandy Bridge_rPGA_Rev0p61

CONN@

Compal Secret Data

Security Classification

Issued Date

2010/10/15

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

Title

Compal Electronics, Inc.

PROCESSOR(2/7) PM,XDP,CLK

Size Document Number

Custom

Rev

0.4

JE50-HR/SJV50-HR M/B Schematics

Date:

Wednesday, October 27, 2010

Sheet

of

61

JCPU1D

11 DDR_A_D[0..63]

11 DDR_A_BS0

11 DDR_A_BS1

11 DDR_A_BS2

AE10

AF10

V6

11 DDR_A_CAS#

11 DDR_A_RAS#

11 DDR_A_WE#

AE8

AD9

AF9

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

SA_CLK[2]

SA_CLK#[2]

SA_CKE[2]

SA_CLK[3]

SA_CLK#[3]

SA_CKE[3]

DDR SYSTEM MEMORY A

C5

D5

D3

D2

D6

C6

C2

C3

F10

F8

G10

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

M8

N10

N8

N7

M10

M9

N9

M7

AG6

AG5

AK6

AK5

AH5

AH6

AJ5

AJ6

AJ8

AK8

AJ9

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

SA_CAS#

SA_RAS#

SA_WE#

Sandy Bridge_rPGA_Rev0p61

@ R184

0_0402_5%

1

2

R217

1K_0402_5%

DIMMreset

DIMM_DRAMRST#_R

1

Q12

BSS138_NL_SOT23-3

SM_DRAMRST#

5 SM_DRAMRST#

R186

4.99K_0402_1%

11,12,14 RST_GATE

SA_CLK_DDR1 11

SA_CLK_DDR#1 11

DDRA_CKE1_DIMMA 11

AB4

AA4

W9

AB3

AA3

W10

DDRA_CS0_DIMMA# 11

DDRA_CS1_DIMMA# 11

SA_ODT[0] AH3

SA_ODT[1] AG3

SA_ODT[2] AG2

SA_ODT[3] AH2

SA_ODT0 11

SA_ODT1 11

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

DDR_A_DQS#0

C4

DDR_A_DQS#1

G6

DDR_A_DQS#2

J3

DDR_A_DQS#3

M6 DDR_A_DQS#4

AL6 DDR_A_DQS#5

AM8 DDR_A_DQS#6

AR12 DDR_A_DQS#7

AM15

DDR_A_DQS#[0..7]

DDR_A_DQS0

DDR_A_DQS1

D4

DDR_A_DQS2

F6

DDR_A_DQS3

K3

DDR_A_DQS4

N6

AL5 DDR_A_DQS5

AM9 DDR_A_DQS6

AR11 DDR_A_DQS7

AM14

DDR_A_DQS[0..7]

DDR_A_MA0

AD10 DDR_A_MA1

W1 DDR_A_MA2

W2 DDR_A_MA3

W7 DDR_A_MA4

DDR_A_MA5

V3

DDR_A_MA6

V2

W3 DDR_A_MA7

W6 DDR_A_MA8

DDR_A_MA9

V1

W5 DDR_A_MA10

AD8 DDR_A_MA11

DDR_A_MA12

V4

DDR_A_MA13

W4

DDR_A_MA14

AF8 DDR_A_MA15

V5

V7

DDR_A_MA[0..15] 11

11

11

12 DDR_B_BS0

12 DDR_B_BS1

12 DDR_B_BS2

12 DDR_B_CAS#

12 DDR_B_RAS#

12 DDR_B_WE#

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

C9

A7

D10

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

J7

J8

K10

K9

J9

J10

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

R6

AA10

AB8

AB9

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

AE2

AD2

R9

SB_CLK_DDR0 12

SB_CLK_DDR#0 12

DDRB_CKE0_DIMMB 12

AE1

AD1

R10

SB_CLK_DDR1 12

SB_CLK_DDR#1 12

DDRB_CKE1_DIMMB 12

AB2

AA2

T9

SB_CLK[2]

SB_CLK#[2]

SB_CKE[2]

AA1

AB1

T10

SB_CLK[3]

SB_CLK#[3]

SB_CKE[3]

AD3

AE3

AD6

AE6

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDRB_CS0_DIMMB# 12

DDRB_CS1_DIMMB# 12

SB_ODT[0] AE4

SB_ODT[1] AD4

SB_ODT[2] AD5

SB_ODT[3] AE5

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

D7

F3

K6

N3

AN5

AP9

AK12

AP15

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

C7

G3

J6

M3

AN6

AP8

AK11

AP14

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

SB_ODT0 12

SB_ODT1 12

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS#[0..7]

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS[0..7]

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_MA[0..15] 12

12

12

Sandy Bridge_rPGA_Rev0p61

CONN@

+1.5V

AA5

AB5

V10

CONN@

R155

1K_0402_5%

2

CPU

Follow CRB1.0

SA_CLK_DDR0 11

12 DDR_B_D[0..63]

SA_CLK_DDR#0 11

DDRA_CKE0_DIMMA 11

SA_CS#[0] AK3

SA_CS#[1] AL3

SA_CS#[2] AG1

SA_CS#[3] AH1

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_BS[0]

SA_BS[1]

SA_BS[2]

AB6

AA6

V9

DDR SYSTEM MEMORY B

JCPU1C

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

C293

0.047U_0402_16V7K

DIMM_DRAMRST# 11,12

S0

RST_GATE hgih ,MOS ON

SM_DRAMRST# HIGH,DIMM_DRAMRST# HIGH

Dimm not reset

S3

RST_GATE Low ,MOS OFF

SM_DRAMRST# lo,DIMM_DRAMRST# HIGH

Dimm not reset

S4,5

RST_GATE Low ,MOS OFF

SM_DRAMRST# lo,DIMM_DRAMRST# low

Dimm reset

Compal Secret Data

Security Classification

Issued Date

2010/10/15

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Title

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

Size Document Number

Custom

Rev

0.4

JE50-HR/SJV50-HR M/B Schematics

Date:

Wednesday, October 27, 2010

1

Sheet

of

61

CFG Straps for Processor

CFG2

R112

1K_0402_5%

D

PEG Static Lane Reversal - CFG2 is for the 16x

JCPU1E

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

1

R513

10K_0402_5%

J15

RSVD24

RSVD25

RSVD26

CFG4

RSVD51

RSVD52

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG6

B34

A33

A34

B35

C35

CFG5

R107

1K_0402_5% @

R108

1K_0402_5%

AJ32

AK32

AH27 change to VCC_DIE_SENSE

RSVD53

PAD

AH27

T7

PCIE Port Bifurcation Straps

RSVD54

RSVD55

RSVD56

RSVD57

RSVD58

AN35

AM35

RSVD54 and RSVD55 had changed to

BCLK_ITP and BCLK_ITP#

11: (Default) x16 - Device 1 functions 1 and 2 disabled

CFG[6:5]

*10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

AT2

AT1

AR1

RSVD27

1/NC : (Default) +1.05VS_VTT

KEY

B1

CFG7

0: +1.0VS_VTT

A19

For 2012 CPU support

J20

B18

A19

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

AR35

AT34

AT33

AP35

AR34

RSVD26 had changed the name to VCCIO_SEL

Need PH +3VALW 10K at +1.05VS_VTT source

for 2012 processor +1.05V and +1.0V select

R102

1K_0402_5%

Sandy Bridge_rPGA_Rev0p61

VCCIO_SEL

VCCIO_SEL

F25

F24

F23

D24

G25

G24

E23

D23

C30

A31

B30

B29

D30

B31

A30

C29

T8

J16

H16

G16

R164

1K_0402_5%

R154

1K_0402_5%

VCCIO_SEL

B

RSVD6

RSVD7

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

For Future CPU M3 support,

Sandey bridge not supportM3,

Check list1.0&CRB say can NC

B4

D1

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

11 SA_DIMM_VREFDQ

12 SB_DIMM_VREFDQ

AJ26

0:Lane Reversed

CFG4

AT26

AM33

AJ27

Display Port Presence Strap

RESERVED

RSVD6 and RSVD7 had changed to

SA_DIMM_VREFDQ and SB_DIMMVREFDQ

definition matches

R109

1K_0402_5%

AJ31

AH31

AJ33

AH33

1: Normal Operation; Lane #

socket pin map definition

CFG2

CFG4

CFG5

CFG6

CFG7

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG2

AK28

AK29

AL26

AL27

AK26

AL29

AL30

AM31

AM32

AM30

AM28

AM26

AN28

AN31

AN26

AM27

AK31

AN29

L7

AG7

AE7

AK2

W8

CFG0

CONN@

PEG DEFER TRAINING

CFG7

1: (Default) PEG Train immediately following xxRESETB

de assertion

0: PEG Wait for BIOS for training

Compal Secret Data

Security Classification

Issued Date

2010/10/15

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

Title

Compal Electronics, Inc.

PROCESSOR(4/7) RSVD,CFG

Size Document Number

Custom

Rev

0.4

JE50-HR/SJV50-HR M/B Schematics

Date:

Wednesday, October 27, 2010

Sheet

of

61

JCPU1F

QC 94A

DC 53A

PEG AND DDR

R02 modify

@

ME interefer,not pop!!

J23

+1.05VS_VTT

CORE SUPPLY

C641

22U_0805_6.3V6M

C291

22U_0805_6.3V6M

C816

220U_B2_2.5VM_R35

C292

22U_0805_6.3V6M

C229

22U_0805_6.3V6M

INTEL Recommend

2*330uF,12*22uF

from PDDG 1.0

R447

75_0402_1%

SVID

VIDALERT#

VIDSCLK

VIDSOUT

R448

43_0402_1%

1

2

R446

R449

2 0_0402_5%

1 1

2 0_0402_5%

H_CPU_SVIDALRT#

AJ29 H_CPU_SVIDCLK

AJ30 H_CPU_SVIDDAT

AJ28

VR_SVID_ALRT# 55

VR_SVID_CLK 55

VR_SVID_DAT 55

Place the PU

resistors close to VR

Place the PU

resistors close to CPU

+CPU_CORE

2010/10/15

VCC_SENSE

VSS_SENSE

VCCSENSE_R

VSSSENSE_R

AJ35

AJ34

R444 1

R443 1

VSSIO_SENSE

B10

A10

VCCIO_SENSE

VSSIO_SENSE

VSSIO_SENSE

2

2

VCCSENSE 55

VSSSENSE 55

0_0402_5%

0_0402_5%

VCCIO_SENSE 53

change to

VSS_SENSE_VCCIO

R442

100_0402_1%

R163

10_0402_5%

SENSE LINES

R445

100_0402_1%

Should change to connect form

power cirucit & layout differential

with VCCIO_SENSE.

Compal Secret Data

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

R450

130_0402_5%

Sandy Bridge_rPGA_Rev0p61

C638

330U_D2_2V_Y

1

@

C232

22U_0805_6.3V6M

1

@

C616

330U_D2_2V_Y

C648

22U_0805_6.3V6M

C288

22U_0805_6.3V6M

+1.05VS_VTT

Security Classification

IssuedCONN@

Date

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

C289

22U_0805_6.3V6M

VCCIO40

+1.05VS_VTT

C649

22U_0805_6.3V6M

2 3

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

C652

22U_0805_6.3V6M

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

C650

22U_0805_6.3V6M

2 3

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

C647

22U_0805_6.3V6M

C606

22U_0805_6.3V6M

2 3

C562

470U_D2_2VM_R4M

PAW00

use 470uF*2

330uF*3

C151

470U_D2_2VM_R4M

2 3

C626

470U_D2_2VM_R4M

C233

470U_D2_2VM_R4M

2 3

C152

470U_D2_2VM_R4M

C160

22U_0805_6.3V6M

Follow Power Suggestion ,

place 3-pin Cap for CPU_CORE

C607

22U_0805_6.3V6M

+CPU_CORE

C171

22U_0805_6.3V6M

C608

22U_0805_6.3V6M

C172

22U_0805_6.3V6M

C609

22U_0805_6.3V6M

C610

22U_0805_6.3V6M

C575

22U_0805_6.3V6M

C635

22U_0805_6.3V6M

C226

22U_0805_6.3V6M

C225

22U_0805_6.3V6M

C627

22U_0805_6.3V6M

C574

22U_0805_6.3V6M

INTEL Recommend

4*470uF,16*22uF and 10*10uF

from PDDG 1.0

C224

22U_0805_6.3V6M

C622

22U_0805_6.3V6M

+1.05VS_VTT

8.5A

C651

22U_0805_6.3V6M

+CPU_CORE

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

C290

22U_0805_6.3V6M

C222

10U_0805_10V4Z

C202

10U_0805_10V4Z

C207

10U_0805_10V4Z

C203

10U_0805_10V4Z

C218

10U_0805_10V4Z

C204

10U_0805_10V4Z

C223

10U_0805_10V4Z

C227

10U_0805_10V4Z

C205

10U_0805_10V4Z

2

D

C206

10U_0805_10V4Z

POWER

+CPU_CORE

SV type CPU

Title

Compal Electronics, Inc.

PROCESSOR(5/7) PWR,BYPASS

Size Document Number

Custom

Rev

0.4

JE50-HR/SJV50-HR M/B Schematics

Date:

Wednesday, October 27, 2010

Sheet

of

61

SENSE

LINES

2

1

VREF

2

1

PAD-OPEN 4x4m

@

+1.5VS

J2

PAD-OPEN 4x4m

@

Short for +1.5VS to +1.5V_1

INTEL Recommend

1*330uF,6*10uF

from PDDG 1.0

+VCCSA

6A

+VCCSA

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA_SENSE

M27

M26

L26

J26

J25

J24

H26

H25

1

@

R1371

1

+

2 0_0402_5%

VCCSA_SENSE

If possible,use os-con cap

if not,use the D2 size

R1411

2 0_0402_5%

VSSSA_SENSE 52

VCCSA_SENSE 52

H23

VCCSA

VCCSA_VID0

FC_C22

VCCSA_VID1

VCCSA_VID1

C22

C24

FC_C22

change to

VCCSA_VID0

VCCSA_VID1 52

R143

10K_0402_5%

VID0

VID1

Vout

2011CPU

2012CPU

0.9V

0.8V

0.725V

0.675V

R138

@ 0_0402_5%

CONN@

Compal Secret Data

Security Classification

2010/10/15

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

INTEL Recommend

1*330uF,3*10uF

from PDDG 1.0

Sandy Bridge_rPGA_Rev0p61

Issued Date

DDR3 -1.5V RAILS

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

INTEL Recommend

1*330uF,1*10uF and 2*1uF(0402)

from PDDG 1.0

VCCPLL1

VCCPLL2

VCCPLL3

+1.5V

J1

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

C221

220U_B2_2.5VM_R35

B6

A6

A2

+1.5V_CPU_VDDQ

10A

C213

10U_0603_6.3V6M

C653

1U_0402_6.3V6K

C654

1U_0402_6.3V6K

C655

10U_0805_10V4Z

C664

220U_B2_2.5VM_R35

R575

100_0402_1%

2

C219

10U_0805_10V4Z

+1.8VS_VCCPLL

C605

10U_0805_10V4Z

1.2A

R528

0_0805_5%

1

2

C688

0.1U_0402_16V4Z

C214

10U_0805_10V4Z

+1.8VS

+V_SM_VREF

AL1

motherboard design (Gfx VR keeps VAXG from

floating) if the VR is stuffed

SM_VREF

R582

100_0402_1%

C355

330U_D2_2V_Y

supports external graphics and if GFX VR is not

stuffed in a common motherboard design,

VAXG can be left floating in a common

+V_SM_VREF should

have 20 mil trace width

C361

10U_0805_10V4Z

Can connect to GND if motherboard only

+1.5V_CPU_VDDQ

C365

10U_0805_10V4Z

Vaxg

VCC_AXG_SENSE 55

VSS_AXG_SENSE 55

C341

10U_0805_10V4Z

UMA@ 2

AK35

AK34

C362

10U_0805_10V4Z

UMA@ 2

VAXG_SENSE

VSSAXG_SENSE

C364

10U_0805_10V4Z

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

C363

10U_0805_10V4Z

UMA@

1

C599

22U_0805_6.3V6M

C600

22U_0805_6.3V6M

UMA@

C273

22U_0805_6.3V6M

UMA@

1

C275

22U_0805_6.3V6M

UMA@

1

C242

22U_0805_6.3V6M

UMA@

1

AT24

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

SA RAIL

POWER

JCPU1G

MISC

C271

22U_0805_6.3V6M

C208

22U_0805_6.3V6M

C274

22U_0805_6.3V6M

C645

330U_D2_2V_Y

C646

330U_D2_2V_Y

UMA@

1

C209

22U_0805_6.3V6M

C210

22U_0805_6.3V6M

UMA@

1

UMA@

1

C231

22U_0805_6.3V6M

UMA@

1

C211

22U_0805_6.3V6M

UMA@

1

C272

22U_0805_6.3V6M

UMA@

1

C212

22U_0805_6.3V6M

UMA@

1

C625

22U_0805_6.3V6M

UMA@

1

C611

22U_0805_6.3V6M

R151

0_0402_5%

DISO@

QC 33A

DC 26A

GRAPHICS

+VGFX_CORE

1.8V RAIL

INTEL Recommend

2*470uF,12*22uF

from PDDG 1.0

Title

Compal Electronics, Inc.

PROCESSOR(6/7) PWR

Size Document Number

Custom

Rev

0.4

JE50-HR/SJV50-HR M/B Schematics

Date:

Wednesday, October 27, 2010

Sheet

of

61

JCPU1H

D

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

JCPU1I

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH26

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

P9

P8

P6

P5

P3

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

M34

L33

L30

L27

L9

L8

L6

L5

L4

L3

L2

L1

K35

K32

K29

K26

J34

J31

H33

H30

H27

H24

H21

H18

H15

H13

H10

H9

H8

H7

H6

H5

H4

H3

H2

H1

G35

G32

G29

G26

G23

G20

G17

G11

F34

F31

F29

Sandy Bridge_rPGA_Rev0p61

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

Sandy Bridge_rPGA_Rev0p61

CONN@

CONN@

Compal Secret Data

Security Classification

Issued Date

2010/10/15

2011/10/15

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

Title

Compal Electronics, Inc.

PROCESSOR(7/7) VSS

Size Document Number

Custom

Rev

0.4

JE50-HR/SJV50-HR M/B Schematics

Date:

Sheet

Wednesday, October 27, 2010

1

10

of

61

+1.5V

+1.5V

DDR_A_D[0..63]

DDR_A0_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS[0..7]

DDR_A_MA[0..15]

DDR_A_D0

DDR_A_D1

DDR_A_DQS#1

DDR_A_DQS1

All VREF traces should

have 10 mil trace width

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

Layout Note:

Place near JDIMM1

DDR_A_DQS#2

DDR_A_DQS2

+1.5V

DDR_A_D18

DDR_A_D19

C409

1U_0402_6.3V6K

C410

1U_0402_6.3V6K

C385

1U_0402_6.3V6K

C371

1U_0402_6.3V6K

DDR_A_D24

DDR_A_D25

DDR_A0_DM3

DDR_A_D26

DDR_A_D27

DDRA_CKE0_DIMMA

6 DDRA_CKE0_DIMMA

+1.5V

DDR_A_BS2

6 DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

C414

10U_0603_6.3V6M

C415

10U_0603_6.3V6M

C378

10U_0603_6.3V6M

C384

10U_0603_6.3V6M

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

SA_CLK_DDR0

SA_CLK_DDR#0

6 SA_CLK_DDR0

6 SA_CLK_DDR#0

+1.5V

1

+

DDR_A_MA13

DDRA_CS1_DIMMA#

6 DDRA_CS1_DIMMA#

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

+0.75VS

DDR_A0_DM5

C388

1U_0402_6.3V6K

C394

1U_0402_6.3V6K

C395

1U_0402_6.3V6K

C393

1U_0402_6.3V6K

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

Layout Note:

Place near JDIMM1.203,204

DDR_A_D56

DDR_A_D57

DDR_A0_DM7

+3VS

+0.75VS

R301

10K_0402_5%

R302

10K_0402_5%

C416

2.2U_0603_6.3V6K

R285

R318

R283

R312

DDR_A_D58

DDR_A_D59

DDR_A0_DM0

DDR_A0_DM1

DDR_A0_DM2

DDR_A0_DM3

DDR_A0_DM4

DDR_A0_DM5

DDR_A0_DM6

DDR_A0_DM7

R315

R284

R286

R316

C404

0.1U_0402_16V4Z

1

1

1

1

1

1

11

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

2

2

2

2

2

2

22

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

205 G1

FOX_AS0A626-U8SN-7F G2

206

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_D6

DDR_A_D7

DDR_A_D12

DDR_A_D13

DDR_A0_DM1

DDR3_DRAMRST#

DIMM_DRAMRST# 6,12

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A0_DM2

DDR_A_D22

DDR_A_D23

DDR_A_D28

DDR_A_D29

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_D30

DDR_A_D31

DDRA_CKE1_DIMMA

DDRA_CKE1_DIMMA 6

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

SA_CLK_DDR1

SA_CLK_DDR#1

SA_CLK_DDR1 6

SA_CLK_DDR#1 6

DDR_A_BS1

DDR_A_RAS#

+1.5V

DDR_A_BS1 6

DDR_A_RAS# 6

DDRA_CS0_DIMMA#

SA_ODT0

SA_ODT1

DDRA_CS0_DIMMA# 6

SA_ODT0 6

R267

1K_0402_5%

SA_ODT1 6

+VREF_CA

DDR_A_D36

DDR_A_D37

DDR_A0_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

C373

0.1U_0402_16V4Z

DDR_A_D32

DDR_A_D33

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

DDR_A_D4

DDR_A_D5

C372

2.2U_0603_6.3V6K

C407

330U_D2_2V_Y

DDR_A_WE#

DDR_A_CAS#

6 DDR_A_WE#

6 DDR_A_CAS#

C383

10U_0603_6.3V6M

C412

10U_0603_6.3V6M

DDR_A_MA10

DDR_A_BS0

6 DDR_A_BS0

C413

10U_0603_6.3V6M

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

6,12,14 RST_GATE

DDR_A_DQS#[0..7]

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

C411

0.1U_0402_16V4Z

BSS138_NL_SOT23-3

R319

1K_0402_5%

C408

2.2U_0603_6.3V6K

1

Q46

@

+1.5V

JDIMM1

1 VREF_DQ

3 VSS2

5 DQ0

7 DQ1

9 VSS4

11 DM0

13 VSS5

15 DQ2

17 DQ3

19 VSS7

21 DQ8

23 DQ9

25 VSS9

27 DQS#1

29

DQS1

31 VSS11

33 DQ10

35 DQ11

37 VSS13

39 DQ16

41 DQ17

43 VSS15

45 DQS#2

47 DQS2

49 VSS18

51 DQ18

53 DQ19

55 VSS20

57 DQ24

59 DQ25

61 VSS22

63 DM3

65 VSS23

67 DQ26

69 DQ27

71 VSS25

+V_DDR_REFA

7 SA_DIMM_VREFDQ

@ R133

0_0402_5%

1

2

R266

1K_0402_5%

R320

1K_0402_5%

M3 support

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A0_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_D62

DDR_A_D63

D_CK_SDATA

D_CK_SCLK

D_CK_SDATA 12,14

D_CK_SCLK 12,14

+0.75VS

CONN@

<Address(SA1,SA0): 00>

DIMM_1 Reserve H:8mm

Compal Secret Data

Security Classification

Issued Date

2010/10/15

Deciphered Date

2011/10/15

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Title

Compal Electronics, Inc.

DDRIII DIMMA

Size Document Number

Custom

Rev

0.4

JE50-HR/SJV50-HR M/B Schematics

Date:

1

Wednesday, October

27, 2010

Sheet

11

of

61

+1.5V

+1.5V

DDR_B_D8

DDR_B_D9

6,11,14 RST_GATE

D

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#[0..7]

DDR_B_DQS[0..7]

DDR_B_D[0..63]

All VREF traces should

have 10 mil trace width

6

6

DDR_B_D10

DDR_B_D11

DDR_B_D16

DDR_B_D17

DDR_B_MA[0..15]

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_D18

DDR_B_D19

Layout Note:

Place near JDIMM2

DDR_B_D24

DDR_B_D25

+1.5V

DDR_B0_DM3

DDR_B_D26

DDR_B_D27

C429

1U_0402_6.3V6K

C430

1U_0402_6.3V6K

C444

1U_0402_6.3V6K

C445

1U_0402_6.3V6K

DDRB_CKE0_DIMMB

6 DDRB_CKE0_DIMMB

DDR_B_BS2

6 DDR_B_BS2

DDR_B_MA12

DDR_B_MA9

+1.5V

DDR_B_MA8

DDR_B_MA5

C449

10U_0603_6.3V6M

C450

10U_0603_6.3V6M

C425

10U_0603_6.3V6M

C424

10U_0603_6.3V6M

DDR_B_MA3

DDR_B_MA1

SB_CLK_DDR0

SB_CLK_DDR#0

6 SB_CLK_DDR0

6 SB_CLK_DDR#0

DDR_B_MA10

DDR_B_BS0

6 DDR_B_BS0

DDR_B_WE#

DDR_B_CAS#

6 DDR_B_WE#

6 DDR_B_CAS#

<BOM Structure>

+1.5V

6 DDRB_CS1_DIMMB#

DDR_B_D32

DDR_B_D33

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_D34

DDR_B_D35

DDR_B_D40

DDR_B_D41

DDR_B0_DM5

DDR_B_D42

DDR_B_D43

+0.75VS

C428

1U_0402_6.3V6K

DDR_B_D48

DDR_B_D49

C439

1U_0402_6.3V6K

C427

1U_0402_6.3V6K

C440

1U_0402_6.3V6K

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_D50

DDR_B_D51

DDR_B_D56

DDR_B_D57

+3VS

DDR_B0_DM7

2