Professional Documents

Culture Documents

Xmatchpro 64

Uploaded by

ammayi9845_930467904Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Xmatchpro 64

Uploaded by

ammayi9845_930467904Copyright:

Available Formats

---------------------------------------------------------------------------------- Company:

-- Engineer:

--- Create Date:

13:27:16 03/22/2010

-- Design Name:

-- Module Name:

xmatchpro64 - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--- Dependencies:

--- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity xmatchpro64 is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

start : in STD_LOGIC;

udata : in STD_LOGIC_VECTOR (63 downto 0);

dataout : out STD_LOGIC_VECTOR (63 downto 0);

addrout : out STD_LOGIC_VECTOR (6 downto 0);

matchhit : out STD_LOGIC);

end xmatchpro64;

architecture Behavioral of xmatchpro64 is

component cam64

port

(clk

: in std_logic;

-- Clock

reset

: in std_logic;

-- Reset

start

: in std_logic;

-- Write

datain

: in std_logic_vector(63 downto 0);-- Tag Data

dataout

: out std_logic_vector(63 downto 0);-- Data out

mh0, mh1, mh2, mh3, mh4, mh5, mh6, mh7 : inout std_logic;

mh8,mh9,mh10,mh11,mh12,mh13,mh14,mh15 : inout std_logic;

mh16,mh17,mh18,mh19,mh20,mh21,mh22,mh23 : inout std_logic;

mh24,mh25,mh26,mh27,mh28,mh29,mh30,mh31 : inout std_logic;

mh32,mh33,mh34,mh35,mh36,mh37,mh38,mh39 : inout std_logic;

mh40,mh41,mh42,mh43,mh44,mh45,mh46,mh47 : inout std_logic;

mh48,mh49,mh50,mh51,mh52,mh53,mh54,mh55 : inout std_logic;

mh56,mh57,mh58,mh59,mh60,mh61,mh62,mh63 : inout std_logic;

mh64, mh65, mh66, mh67, mh68, mh69, mh70, mh71 : inout

std_logic;

mh72,mh73,mh74,mh75,mh76,mh77,mh78,mh79 : inout std_logic;

mh80,mh81,mh82,mh83,mh84,mh85,mh86,mh87 : inout std_logic;

mh88,mh89,mh90,mh91,mh92,mh93,mh94,mh95 : inout std_logic;

mh96,mh97,mh98,mh99,mh100,mh101,mh102,mh103 : inout

std_logic;

mh104,mh105,mh106,mh107,mh108,mh109,mh110,mh111 : inout std_logic;

mh112,mh113,mh114,mh115,mh116,mh117,mh118,mh119 : inout std_logic;

mh120,mh121,mh122,mh123,mh124,mh125,mh126,mh127 : inout std_logic;

matchhit

: out std_logic; --Found Match

addr_out : out std_logic_vector(6 downto 0));

end component;

begin

u3:cam64 port map (clk => clk,reset => reset,start => start,datain => udata,data

out => dataout,

mh0 => open, mh1 => open, mh2 => open, mh3 => open,

mh4 => open, mh5 => open, mh6 => open, mh7 => open,

mh8 => open, mh9 => open, mh10 => open, mh11 => open,

mh12 => open, mh13 => open, mh14 => open, mh15 => open,

mh16 => open, mh17 => open, mh18 => open, mh19 => open,

mh20 => open, mh21 => open, mh22 => open, mh23 => open,

mh24 => open, mh25 => open, mh26 => open, mh27 => open,

mh28 => open, mh29 => open, mh30 => open, mh31 => open,

mh32 => open, mh33 => open, mh34 => open, mh35 => open,

mh36 => open, mh37 => open, mh38 => open, mh39 => open,

mh40 => open, mh41 => open, mh42 => open, mh43 => open,

mh44 => open, mh45 => open, mh46 => open, mh47 => open,

mh48 => open, mh49 => open, mh50 => open, mh51 => open,

mh52 => open, mh53 => open, mh54 => open, mh55 => open,

mh56 => open, mh57 => open, mh58 => open, mh59 => open,

mh60 => open, mh61 => open, mh62 => open, mh63 => open,

mh64 => open,mh65 => open,mh66 => open,mh67 => open,mh68 => open,

mh69 => open,mh70 => open,mh71 => open,mh72 => open,mh73 => open,

mh74 => open,mh75 => open,mh76 => open,mh77 => open,mh78 => open,

mh79 => open,mh80 => open,mh81 => open,mh82 => open,mh83 => open,

mh84 => open,mh85 => open,mh86 => open,mh87 => open,mh88 => open,

mh89 => open,mh90 => open,mh91 => open,mh92 => open,mh93 => open,mh94 => open,

mh95 => open,mh96 => open,mh97 => open,mh98 => open,mh99 => open,mh100 => open,

mh101 => open,mh102 => open,mh103 => open,mh104 => open,mh105 => open,mh106 => o

pen,

mh107 => open,mh108 => open,mh109 => open,mh110 => open,mh111 => open,mh112 => o

pen,

mh113 => open,mh114 => open,mh115 => open,mh116 => open,mh117 => open,mh118 => o

pen,

mh119 => open,mh120 => open,mh121 => open,mh122 => open,mh123 => open,mh124 =>

open,mh125=> open,

mh126 => open,mh127 => open,

matchhit => matchhit,

addr_out => addrout);

end Behavioral;

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Superscripts: 2 2x 2x 2x Subscripts: X X X XDocument1 pageSuperscripts: 2 2x 2x 2x Subscripts: X X X Xammayi9845_930467904No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Carry-Select and Conditional-Sum AddersDocument14 pagesCarry-Select and Conditional-Sum Adderssivakumarb92No ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Work plan for designing and testing a remote data acquisition systemDocument3 pagesWork plan for designing and testing a remote data acquisition systemammayi9845_930467904No ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Lcd Interfacing with Lpc2148 MicrocontrollerDocument3 pagesLcd Interfacing with Lpc2148 Microcontrollerammayi9845_930467904No ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

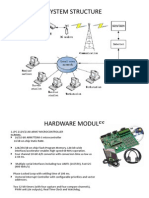

- System StructureDocument3 pagesSystem Structureammayi9845_930467904No ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Phytomonitoring System: Data Colection Software SensorsDocument3 pagesPhytomonitoring System: Data Colection Software Sensorsammayi9845_930467904No ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Data Acquisition - Why 3G?Document3 pagesData Acquisition - Why 3G?ammayi9845_930467904No ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- SIMCOM 900 GSM Module GSM GPRS Modem Features RS232 Interface TCP IP StackDocument3 pagesSIMCOM 900 GSM Module GSM GPRS Modem Features RS232 Interface TCP IP Stackammayi9845_930467904No ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Continued: Detection of A/D ConvertionDocument2 pagesContinued: Detection of A/D Convertionammayi9845_930467904No ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- Agenda: Phytomonitoring System Recommended Setup Block Diagram Work Done Future Work Plan ReferenceDocument3 pagesAgenda: Phytomonitoring System Recommended Setup Block Diagram Work Done Future Work Plan Referenceammayi9845_930467904No ratings yet

- February: Interfacing Multiple Sensors Using Wireless Network and Using Visual Software Display On MonitorDocument3 pagesFebruary: Interfacing Multiple Sensors Using Wireless Network and Using Visual Software Display On Monitorammayi9845_930467904No ratings yet

- Future Work Plan: Tasks by MonthDocument2 pagesFuture Work Plan: Tasks by Monthammayi9845_930467904No ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Design RequirementsDocument2 pagesDesign Requirementsammayi9845_930467904No ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Work Done Till First ReviewDocument3 pagesWork Done Till First Reviewammayi9845_930467904No ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Design RequirementsDocument5 pagesDesign Requirementsammayi9845_930467904No ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Work Flow ChartDocument3 pagesWork Flow Chartammayi9845_930467904No ratings yet

- 1Document4 pages1ammayi9845_930467904No ratings yet

- 1 ADocument2 pages1 Aammayi9845_930467904No ratings yet

- Swami Proj. ProposalDocument1 pageSwami Proj. Proposalammayi9845_930467904No ratings yet

- Swami New Proj - ProposalDocument1 pageSwami New Proj - Proposalammayi9845_930467904No ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Xmatchpro 64Document2 pagesXmatchpro 64ammayi9845_930467904No ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- New Proj - SynopsisDocument2 pagesNew Proj - Synopsisammayi9845_930467904No ratings yet

- Comp AnimationDocument1 pageComp Animationammayi9845_930467904No ratings yet

- MayaDocument1 pageMayaammayi9845_930467904No ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- LlcompDocument2 pagesLlcompammayi9845_930467904No ratings yet

- Figure 1: A Block Diagram of A Basic FilterDocument10 pagesFigure 1: A Block Diagram of A Basic Filterammayi9845_930467904No ratings yet

- SynopsisDocument6 pagesSynopsisammayi9845_930467904No ratings yet

- XmatcDocument3 pagesXmatcammayi9845_930467904No ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- 5GDocument20 pages5GshubhiNo ratings yet

- Image Processing and Compression TechniquesDocument16 pagesImage Processing and Compression Techniquesammayi9845_930467904No ratings yet

- Sch40 80 ASTM A53Document2 pagesSch40 80 ASTM A53Keshia Murillo PinnockNo ratings yet

- DT Progression Pathways ks3 Textiles Y9Document1 pageDT Progression Pathways ks3 Textiles Y9api-240012980No ratings yet

- Medical Robot ReportDocument21 pagesMedical Robot Reporta_m_shihaNo ratings yet

- Project calculation sheet for pull-out capacity of holding down boltsDocument1 pageProject calculation sheet for pull-out capacity of holding down boltsKhalid ElazharyNo ratings yet

- Code of Conduct at Pizza HutDocument2 pagesCode of Conduct at Pizza HutAdeel Chaudhary0% (1)

- CONSTRUCTION OF INTERNAL ROADS & INFRASTRUCTURE WORKS FOR SECTOR EAST 25, PHASE 2, ABU DHABI - DELAY EVENT IMPACT CALCULATIONSDocument10 pagesCONSTRUCTION OF INTERNAL ROADS & INFRASTRUCTURE WORKS FOR SECTOR EAST 25, PHASE 2, ABU DHABI - DELAY EVENT IMPACT CALCULATIONS143No ratings yet

- Mindmup Group-2Document10 pagesMindmup Group-2api-271772521No ratings yet

- Feature Setup Description: Software Basic Data Mcs - TCBCDocument77 pagesFeature Setup Description: Software Basic Data Mcs - TCBCAlexis MauricioNo ratings yet

- WELKIN - Price Reference - 2021-07-15Document1 pageWELKIN - Price Reference - 2021-07-15marcoaparrafNo ratings yet

- Imageclass Lbp611cn 613cdw 2Document2 pagesImageclass Lbp611cn 613cdw 2Maulana Ikhwan SadikinNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Unethical Business Pratices in Corporates: March 2016Document13 pagesUnethical Business Pratices in Corporates: March 2016Manju Nadh ChakravadhanulaNo ratings yet

- MMDS Indoor/Outdoor Transmitter Manual: Chengdu Tengyue Electronics Co., LTDDocument6 pagesMMDS Indoor/Outdoor Transmitter Manual: Chengdu Tengyue Electronics Co., LTDHenry Jose OlavarrietaNo ratings yet

- Critical Reading As ReasoningDocument18 pagesCritical Reading As ReasoningKyle Velasquez100% (3)

- By Himanshu Panwar Asst. Prof. Civil Engineering Department AkgecDocument34 pagesBy Himanshu Panwar Asst. Prof. Civil Engineering Department AkgecAlok0% (1)

- Built-In Exceptions in PythonDocument6 pagesBuilt-In Exceptions in PythonUjwala BhogaNo ratings yet

- Assignment OracleDocument4 pagesAssignment OracleKyle Austin PabustanNo ratings yet

- Computed TomographyDocument94 pagesComputed TomographyBMT100% (3)

- 194 Sample ChapterDocument27 pages194 Sample ChapterVikas TiwariNo ratings yet

- Simovert Masterdrives VCDocument16 pagesSimovert Masterdrives VCangeljavier9No ratings yet

- II B.Tech II Semester Regular Examinations, Apr/May 2007 Chemical Engineering Thermodynamics-IDocument7 pagesII B.Tech II Semester Regular Examinations, Apr/May 2007 Chemical Engineering Thermodynamics-IrajaraghuramvarmaNo ratings yet

- Course Overview CSC 1707 Maths For ComputingDocument16 pagesCourse Overview CSC 1707 Maths For ComputingSarah JNo ratings yet

- TM4320 PDFDocument85 pagesTM4320 PDFandres cortezNo ratings yet

- Binary PDFDocument13 pagesBinary PDFbyprasadNo ratings yet

- IALA Design of Fairways Doc - 307 - EngDocument42 pagesIALA Design of Fairways Doc - 307 - EngDeanna Barrett100% (2)

- BS Basics Boundary Scan PDFDocument2 pagesBS Basics Boundary Scan PDFShankar ArunmozhiNo ratings yet

- 4-way switch wiring diagram for a 2 pickup guitarDocument1 page4-way switch wiring diagram for a 2 pickup guitarNebojša JoksimovićNo ratings yet

- PDF Ebook Pickle Things by Marc Brown Download BookDocument5 pagesPDF Ebook Pickle Things by Marc Brown Download BookCorissNo ratings yet

- Week 6: Practice Challenge 1 - Charts: InstructionsDocument7 pagesWeek 6: Practice Challenge 1 - Charts: InstructionskiranNo ratings yet

- SmartPlant Instrumentation installation checklistDocument2 pagesSmartPlant Instrumentation installation checklistmnoormohamed82No ratings yet

- Marketing Research of Pre-Start-UpDocument2 pagesMarketing Research of Pre-Start-UpafsalpkgroupNo ratings yet

- Defensive Cyber Mastery: Expert Strategies for Unbeatable Personal and Business SecurityFrom EverandDefensive Cyber Mastery: Expert Strategies for Unbeatable Personal and Business SecurityRating: 5 out of 5 stars5/5 (1)

- Dealers of Lightning: Xerox PARC and the Dawn of the Computer AgeFrom EverandDealers of Lightning: Xerox PARC and the Dawn of the Computer AgeRating: 4 out of 5 stars4/5 (88)

- Scary Smart: The Future of Artificial Intelligence and How You Can Save Our WorldFrom EverandScary Smart: The Future of Artificial Intelligence and How You Can Save Our WorldRating: 4.5 out of 5 stars4.5/5 (54)

- Algorithms to Live By: The Computer Science of Human DecisionsFrom EverandAlgorithms to Live By: The Computer Science of Human DecisionsRating: 4.5 out of 5 stars4.5/5 (722)

- ChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveFrom EverandChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveNo ratings yet

- Digital Gold: Bitcoin and the Inside Story of the Misfits and Millionaires Trying to Reinvent MoneyFrom EverandDigital Gold: Bitcoin and the Inside Story of the Misfits and Millionaires Trying to Reinvent MoneyRating: 4 out of 5 stars4/5 (51)