Professional Documents

Culture Documents

Chapter 4: Modules and Ports: Answer

Uploaded by

Raffi SkOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter 4: Modules and Ports: Answer

Uploaded by

Raffi SkCopyright:

Available Formats

Chapter 4: Modules and Ports

by tarique on October 4th, 2011

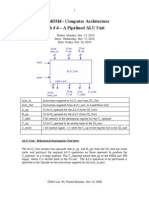

1. What are the basic components of a module? Which components are mandatory? ANSWER: i) Module Name, Port List, Port Declarations, Parameters, Declarations of wires, regs and other variables, Data flow statements, Instantiation of lower level modules, always and initial blocks, Tasks and functions, endmodule statement. ii) module, module name,and endmodule. 2. Does a module that does not interact with its environment have any I/O ports? Does it have a port list in the module definition? ANSWER: i) have ii) no 3. A 4-bit parallel shift register has I/O pins as shown in the figure bellow. Write the module definition for this module shift_reg. Include the list of ports and port declarations. You do not need to show the internals.

ANSWER: module shift_reg(reg_out,reg_in,clock); output reg [3:0]reg_out; input [3:0]reg_in; input clock; endmodule

4. Declare a top-level module stimulus. Define REG_IN(4-bit)and CLK(1-bit)as reg register variables and REG_OUT(4-bit)as wire. Instanitiate the module shift_reg and call it sr1. Connect the ports by ordered list. ANSWER: module stimulus; reg [3:0]REG_IN; reg CLK; wire [3:0]REG_OUT; shift_reg sr1(REG_OUT,REG_IN,CLK); endmodule 5. Connect the ports in Step 4 by name. ANSWER: shift_reg(.reg_out(REG_OUT),.reg_in(REG_IN),.clock(CLK)); 6.Write the hierarchical names for variables REG_IN,CLK,REG_OUT; ANSWER: stimulus.REG_IN, stimulus.CLK, stimulus.REG_OUT 7. Write the hierarchical name for the instance sr1. Write the hierarchical names for its ports clock and reg_in. ANSWER: stimulus.sr1, stimulus.sr1.clock stimulus.sr1.reg_in Reference: Smair Palnitkar, Verilog HDL: A Guide to Digital Design and Synthesis (2nd) Source: http://www.cnblogs.com/halflife

You might also like

- Modules and PortsDocument20 pagesModules and PortsSoumyadeep DasNo ratings yet

- Verilog Chapter 3: Modules and Hierarchical StructureDocument24 pagesVerilog Chapter 3: Modules and Hierarchical Structurecuong03No ratings yet

- EE371 Verilog Tutorial 2Document10 pagesEE371 Verilog Tutorial 2Nguyễn Trung TuấnNo ratings yet

- A Simple Design - DoulosDocument2 pagesA Simple Design - DoulosMiguel BrunoNo ratings yet

- Module 2.1 Gate-Level/Structural Modeling: UNIT 2: Modeling in VerilogDocument9 pagesModule 2.1 Gate-Level/Structural Modeling: UNIT 2: Modeling in VerilogNikhilPrakashNo ratings yet

- Algorithm Function Block-2Document2 pagesAlgorithm Function Block-2Babar BobyNo ratings yet

- Configure Serial Number Function BlockDocument2 pagesConfigure Serial Number Function BlockBabar BobyNo ratings yet

- Verilog ModuleDocument14 pagesVerilog ModuleMuskan YadavNo ratings yet

- Chapter 2 - ModuleHierarchical StructureDocument19 pagesChapter 2 - ModuleHierarchical StructurePhạm Gia LongNo ratings yet

- 8051 MC 2010Document7 pages8051 MC 2010Vikram RaoNo ratings yet

- Vlsi Unit 5 NotesDocument21 pagesVlsi Unit 5 NotesRamana Sekar100% (1)

- Verilog HDL: A Solution For EverybodyDocument30 pagesVerilog HDL: A Solution For EverybodyLKNo ratings yet

- Vimiaa01 Verilog PrintDocument29 pagesVimiaa01 Verilog PrintManjunath BadigerNo ratings yet

- IO Plus ManualDocument30 pagesIO Plus ManualMohamed AzzuzNo ratings yet

- Microprocessors and Applications GuideDocument3 pagesMicroprocessors and Applications GuideImmanuel VinothNo ratings yet

- Mod 4Document25 pagesMod 4Sandro Silva100% (1)

- Verilog Parameters and Operators GuideDocument25 pagesVerilog Parameters and Operators GuideR INI BHANDARINo ratings yet

- IC - 4 Sem Micro ControllerDocument7 pagesIC - 4 Sem Micro ControllerVikram RaoNo ratings yet

- Experiment No. 1: Switch and Gate Level Modeling Pre Lab TaskDocument17 pagesExperiment No. 1: Switch and Gate Level Modeling Pre Lab TaskMuhammad ShoaibNo ratings yet

- Digital Design Lab Manual: Introduction To VerilogDocument48 pagesDigital Design Lab Manual: Introduction To VerilogKeith FernandesNo ratings yet

- HDL Lab SyllabusDocument2 pagesHDL Lab Syllabussuhas RNo ratings yet

- Chapter2PLC Hardware Components-2Document88 pagesChapter2PLC Hardware Components-2Fati AldNo ratings yet

- Question Bank: Subject Code: Ec1303 Sem / Year Subject NameDocument3 pagesQuestion Bank: Subject Code: Ec1303 Sem / Year Subject NameShafeeq AbduljameelNo ratings yet

- ICC2Design Planning01initial - DPDocument22 pagesICC2Design Planning01initial - DPRAZNo ratings yet

- Second Year 4TH Sem Question Bank For Microprocessor and Micro ControllerDocument6 pagesSecond Year 4TH Sem Question Bank For Microprocessor and Micro ControllerPRIYA RAJINo ratings yet

- Mtds 1 VHDL Quick LookDocument6 pagesMtds 1 VHDL Quick Looknithinsp92No ratings yet

- GATE LEVEL HALF ADDERDocument10 pagesGATE LEVEL HALF ADDERrizwan900No ratings yet

- Programming Assignment Solution-Week2Document3 pagesProgramming Assignment Solution-Week2MADAN MadyNo ratings yet

- Lab 03Document14 pagesLab 03Asif MalikNo ratings yet

- Chapter-1: 1.1. Serial Data TransmissionDocument44 pagesChapter-1: 1.1. Serial Data TransmissionSanjay BedudooriNo ratings yet

- 8051 MICROCONTROLLER LABORATORY MANUALDocument20 pages8051 MICROCONTROLLER LABORATORY MANUALjasoneinsteinNo ratings yet

- ITDR2102 Computer Organization AnswersDocument2 pagesITDR2102 Computer Organization AnswersM Arif SiddiquiNo ratings yet

- Basic Elements of VHDL: VHSIC Hardware Description Language (VHDL)Document3 pagesBasic Elements of VHDL: VHSIC Hardware Description Language (VHDL)Jyoti SahooNo ratings yet

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitDocument8 pagesECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilNo ratings yet

- Verilogxl TutDocument68 pagesVerilogxl TutPrak AshNo ratings yet

- VLSI and OFC Lab2016 PDFDocument63 pagesVLSI and OFC Lab2016 PDFsandeep_hriturajNo ratings yet

- Lab 1 - OLED, GPIO, InterruptDocument6 pagesLab 1 - OLED, GPIO, Interruptprakash_shrNo ratings yet

- PLCQDocument2 pagesPLCQdenramrNo ratings yet

- Merge PDFDocument26 pagesMerge PDFAnonymous dhsZ0D0g9bNo ratings yet

- C2 MCQDocument34 pagesC2 MCQBUQRA AN FARDEENA BINTI MOHAMED FAIRUZ STUDENTNo ratings yet

- VERILOGDocument89 pagesVERILOGrhythm 2021No ratings yet

- Verilog HDL: A Guide To Digital Design DS TH I and SynthesisDocument62 pagesVerilog HDL: A Guide To Digital Design DS TH I and SynthesisSharan ChaitanyaNo ratings yet

- C Language Function BlockDocument14 pagesC Language Function BlockThilinaNNo ratings yet

- EC6504-Microcroprocessor and Microcontroller QBDocument6 pagesEC6504-Microcroprocessor and Microcontroller QBL Narayanan DevaNo ratings yet

- MPMC Overall Question BankDocument5 pagesMPMC Overall Question BankLAKSHMINo ratings yet

- Lab Manual-1st TermDocument12 pagesLab Manual-1st Termcmp2012No ratings yet

- Lab Description - Keil ToolsDocument21 pagesLab Description - Keil ToolsGnurt NeyugnNo ratings yet

- Verilog: Here, We Will Use The Verilog HDL VHDL Is Another Common HDLDocument21 pagesVerilog: Here, We Will Use The Verilog HDL VHDL Is Another Common HDLNirmith VishwanathNo ratings yet

- Structural Design StyleDocument7 pagesStructural Design StyleLilya OuarabNo ratings yet

- 4.1 Assembler BasicsDocument24 pages4.1 Assembler BasicsnarayananprasanthNo ratings yet

- Verilog Lecture 1 - NoopurDocument41 pagesVerilog Lecture 1 - NoopurMonis KhanNo ratings yet

- Ec8691 - Microprocessors and Microcontrollers: Question BankDocument5 pagesEc8691 - Microprocessors and Microcontrollers: Question Bankrkkumar07No ratings yet

- MP Assign5Document5 pagesMP Assign5Fahad Ali KhanNo ratings yet

- Verilog TutorialDocument92 pagesVerilog TutorialAmmar AjmalNo ratings yet

- Day1 and 2Document48 pagesDay1 and 2Effecure HealthcareNo ratings yet

- Ee6502 Microprocessors and Microcontrollers 2 Mark Question and Answers BY Ensolt ElakkiaDocument38 pagesEe6502 Microprocessors and Microcontrollers 2 Mark Question and Answers BY Ensolt ElakkiaBalaprakash VadivelNo ratings yet

- Prelim Module5 - BDocument7 pagesPrelim Module5 - BCelimen, John Renz C.No ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- PIC Projects and Applications using C: A Project-based ApproachFrom EverandPIC Projects and Applications using C: A Project-based ApproachRating: 4 out of 5 stars4/5 (2)

- Mastering Python: A Comprehensive Guide to ProgrammingFrom EverandMastering Python: A Comprehensive Guide to ProgrammingNo ratings yet

- Compile Test CodesDocument24 pagesCompile Test CodesRaffi SkNo ratings yet

- (WWW - Entrance-Exam - Net) - Wipro Sample Paper 2 PDFDocument0 pages(WWW - Entrance-Exam - Net) - Wipro Sample Paper 2 PDFRaffi SkNo ratings yet

- (WWW - Entrance Exam - Net) Electronics Based CompaniesDocument11 pages(WWW - Entrance Exam - Net) Electronics Based CompaniesPrativendra PatelNo ratings yet

- VgaDocument7 pagesVgafenutfenutNo ratings yet

- Lab 1Document24 pagesLab 1Raffi SkNo ratings yet

- Chp8 PDFDocument15 pagesChp8 PDFRaffi SkNo ratings yet

- Lab 1Document24 pagesLab 1Raffi SkNo ratings yet

- Wipro 3Document11 pagesWipro 3akmalrahmanNo ratings yet

- Vlsi Lab DocumentDocument18 pagesVlsi Lab DocumentRaffi SkNo ratings yet

- 2 Design Specification For 4 Bit ProcessorDocument4 pages2 Design Specification For 4 Bit ProcessorAjay G BellamNo ratings yet

- TermsDocument1 pageTermsRaffi SkNo ratings yet

- Written Test Pattern Is Verbal 15 Quetions Quanti. Cum Reasoing 15 Questions Technical 20 QuestionsDocument3 pagesWritten Test Pattern Is Verbal 15 Quetions Quanti. Cum Reasoing 15 Questions Technical 20 QuestionsRaffi SkNo ratings yet

- Adc0809-N Data SheetDocument19 pagesAdc0809-N Data SheetJesus BernalNo ratings yet

- A Synchronous Synchronous Reset Design in ASICDocument38 pagesA Synchronous Synchronous Reset Design in ASICadaiadaiNo ratings yet

- Cadence 5Document6 pagesCadence 5Raffi SkNo ratings yet

- Exercise 6 - Sequential Circuit Design: 60-265 Computer Architecture I: Digital Design Fall 2012Document5 pagesExercise 6 - Sequential Circuit Design: 60-265 Computer Architecture I: Digital Design Fall 2012Raffi SkNo ratings yet

- DM7474 PDFDocument5 pagesDM7474 PDFRaffi SkNo ratings yet

- 2 Design Specification For 4 Bit ProcessorDocument4 pages2 Design Specification For 4 Bit ProcessorAjay G BellamNo ratings yet

- Verilog modules for 4-bit ALU, register, RAM and instruction decoderDocument6 pagesVerilog modules for 4-bit ALU, register, RAM and instruction decoderRaffi SkNo ratings yet

- OopDocument67 pagesOopRaffi SkNo ratings yet

- Assignment6 Solution 3rd EditionDocument10 pagesAssignment6 Solution 3rd EditionRaffi SkNo ratings yet

- Chapter 6. Dataflow Modeling: 6.7 ExercisesDocument8 pagesChapter 6. Dataflow Modeling: 6.7 ExercisesRaffi SkNo ratings yet

- Synonyms & AntonymsDocument30 pagesSynonyms & AntonymsMohan100% (2)

- TCS Talent Test InstructionsDocument17 pagesTCS Talent Test InstructionsRaffi SkNo ratings yet

- New Text DocumentDocument4 pagesNew Text DocumentRaffi SkNo ratings yet

- A Greedy Algorithm For Wire Length OptimizationDocument4 pagesA Greedy Algorithm For Wire Length OptimizationRaffi SkNo ratings yet

- 06242064Document6 pages06242064Raffi SkNo ratings yet

- 04041915Document9 pages04041915Raffi SkNo ratings yet

- A Blind Digital Watermarking Algorithm Based On Wavelet TransformDocument4 pagesA Blind Digital Watermarking Algorithm Based On Wavelet TransformShivangi TandonNo ratings yet